storage device

A storage device and storage array technology, applied in the direction of electrical components, electrical solid-state devices, circuits, etc., can solve the problems of increasing the area occupied by the well voltage extraction area, constrained lithography process limit, and unfavorable utilization of semiconductor substrates. Achieve the effects of reducing the occupied area, reducing production costs and improving utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

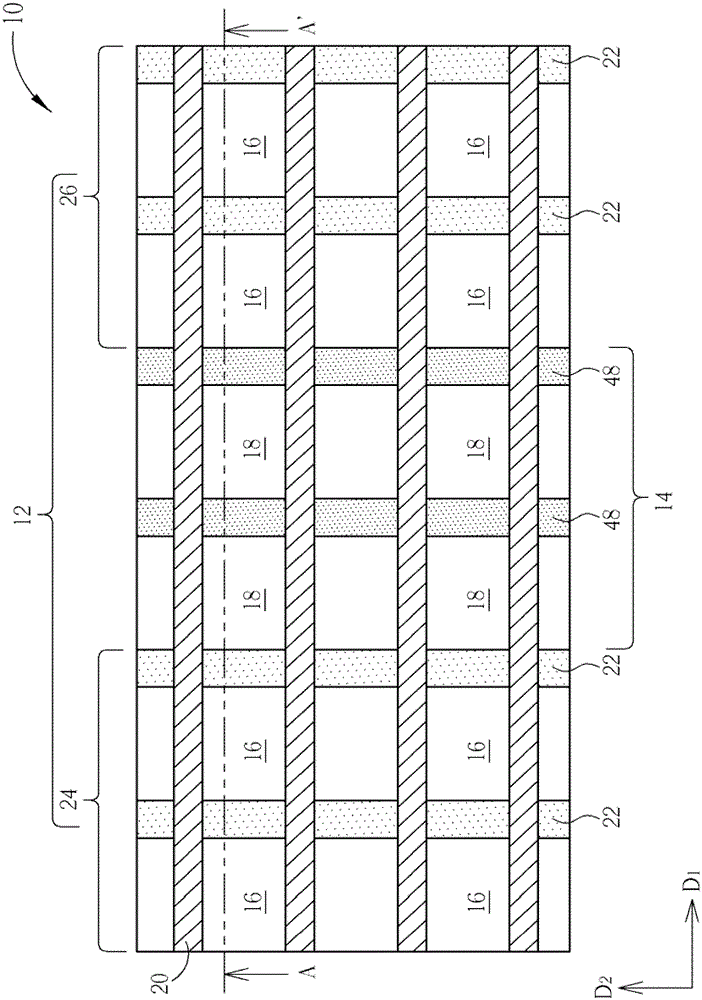

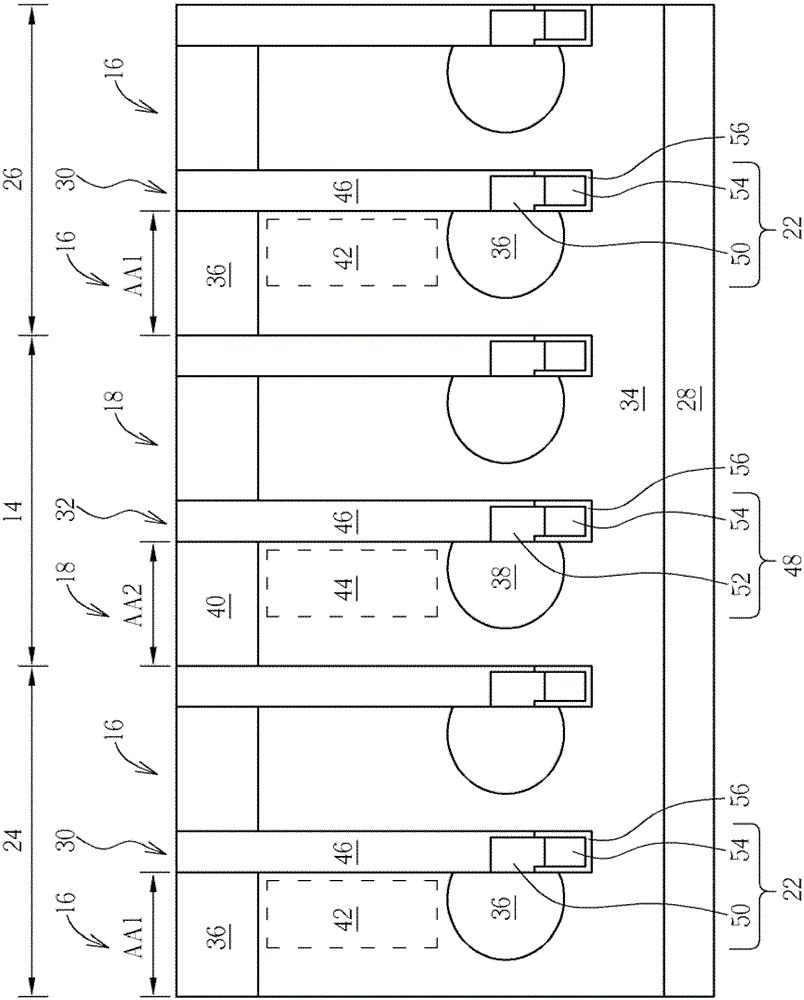

[0026] figure 1 It is a schematic diagram of a storage device according to a preferred embodiment of the present invention. Such as figure 1 As shown, the memory device 10 includes a memory array 12 and at least one well voltage extraction region 14 . The memory array 12 includes a plurality of vertical transistors 16 electrically coupled to corresponding word lines 20 and buried bit lines 22, wherein the word lines 20 extend along a first direction D1, and the buried bit lines 22 extend along a second direction D2. , and the first direction D1 is substantially perpendicular to the second direction D2. The well voltage extraction region 14 includes at least one transistor structure 18 for releasing the well region of the memory device 10 ( figure 1 (not shown) accumulated electrons to adjust the voltage of the well region. In addition, the well voltage extraction region 14 traverses the memory array 12 along the second direction D2, and the memory array 12 is divided into t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More