Multi-core CPU (Central Processing Unit) load balancing method, multi-core CPU and solid state disk

A solid-state hard disk, load balancing technology, applied in multi-programming devices, input/output to record carrier, resource allocation, etc., can solve complex algorithms, reduce development efficiency, increase load balancing code development cycle and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

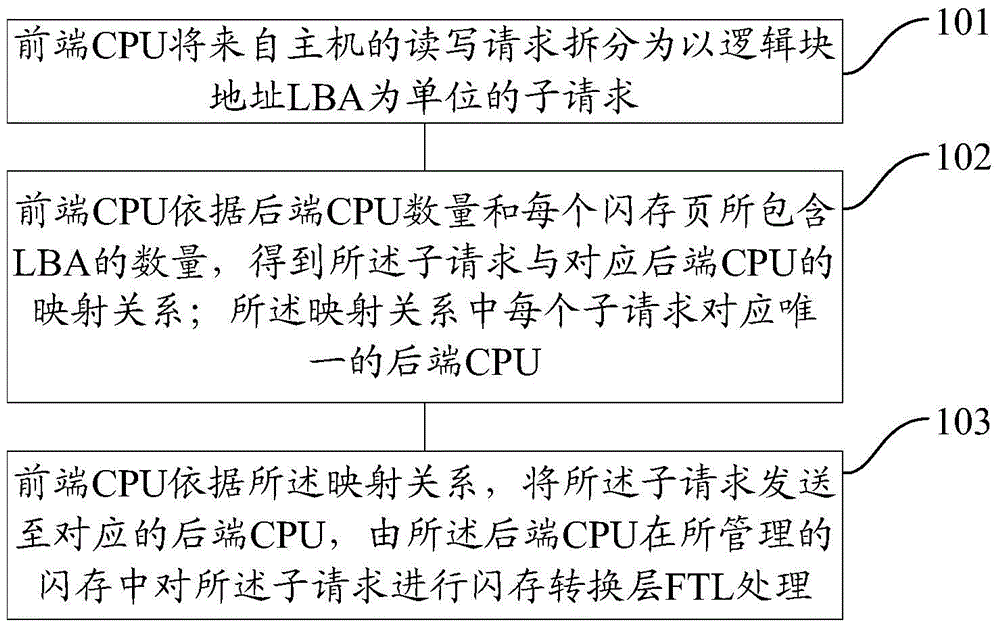

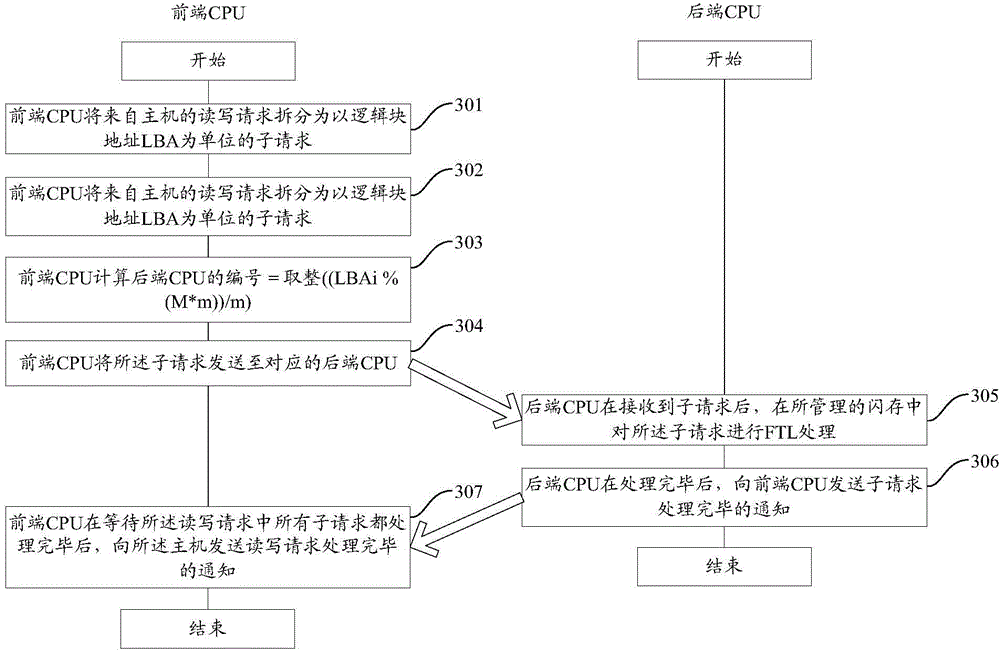

[0036] refer to figure 1 , shows a flow chart of Embodiment 1 of a multi-core CPU load balancing method of the present invention, the multi-core CPU may specifically include a front-end CPU and at least one back-end CPU, each of which is used to manage solid-state The flash memory of the hard disk, and the flash memory managed by each back-end CPU is different, and the method may specifically include:

[0037] Step 101, the front-end CPU splits the read and write request from the host into sub-requests with the logical block address LBA as the unit;

[0038] The embodiment of the present invention can be applied to a solid-state hard disk device that uses a multi-core CPU to implement FTL, and is used to improve the development efficiency of the multi-core CPU load balancing code on the device.

[0039] Assuming that the size of each LBA is 4096bytes, and the read and write request involves reading 24 LBAs starting from 0, then the front-end CPU can split it into 24 sub-reque...

Embodiment 2

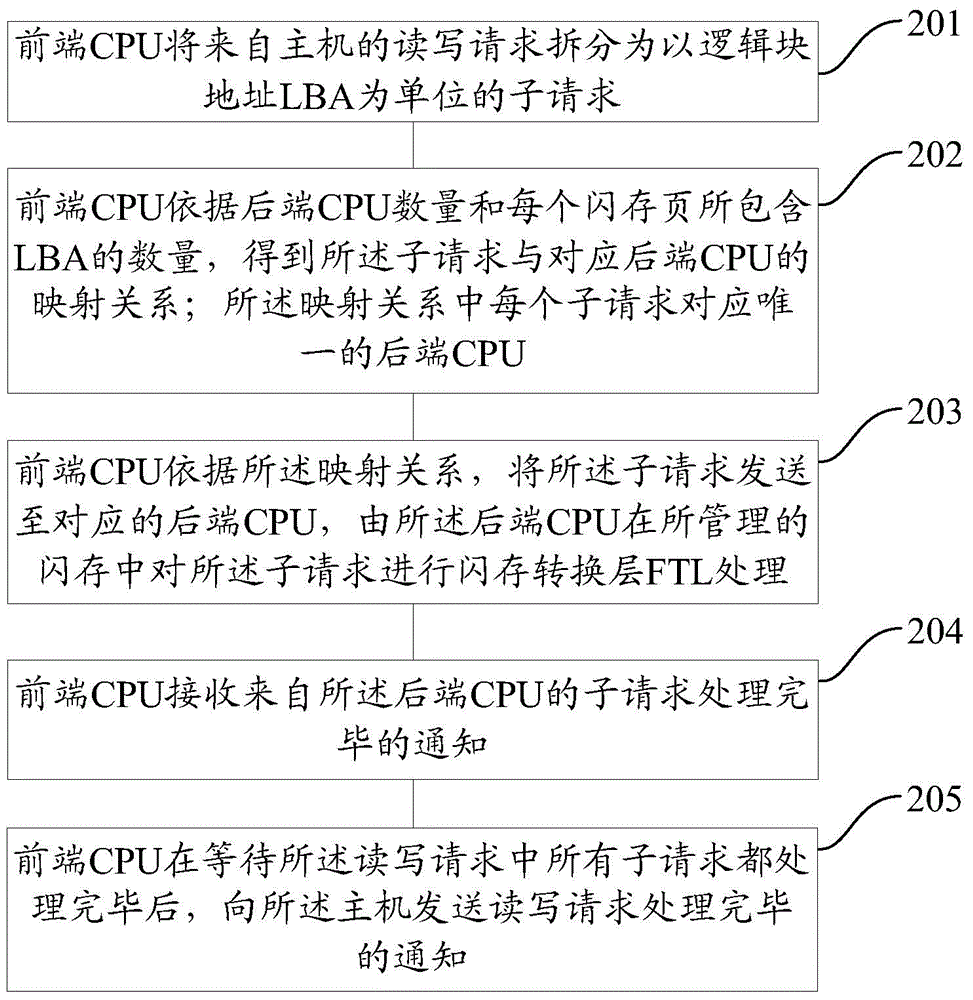

[0051] refer to figure 2 , shows a flow chart of Embodiment 2 of a multi-core CPU load balancing method of the present invention, the multi-core CPU may specifically include a front-end CPU and at least one back-end CPU, each of which is used to manage solid-state The flash memory of the hard disk, and the flash memory managed by each back-end CPU is different, and the method may specifically include:

[0052] Step 201, the front-end CPU splits the read and write request from the host into sub-requests with the logical block address LBA as the unit;

[0053] Step 202, the front-end CPU obtains the mapping relationship between the sub-request and the corresponding back-end CPU according to the number of back-end CPUs and the number of LBAs contained in each flash page; in the mapping relationship, each sub-request corresponds to a unique back-end CPU;

[0054] Step 203, the front-end CPU sends the sub-request to the corresponding back-end CPU according to the mapping relation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com