Removable indicator structure in electronic chips of a common substrate for process adjustment

A technology of electronic chips and indicators, applied in the direction of electric solid devices, circuits, electrical components, etc., to achieve the effect of low power consumption and small resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

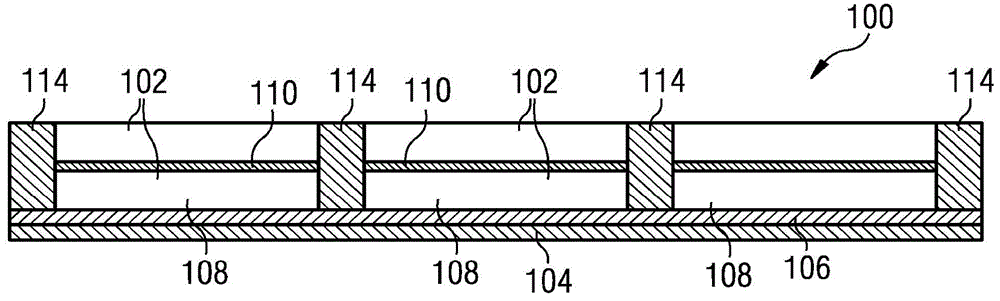

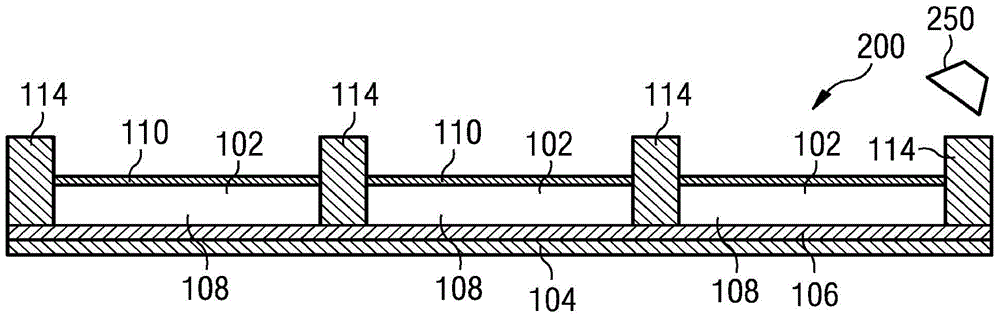

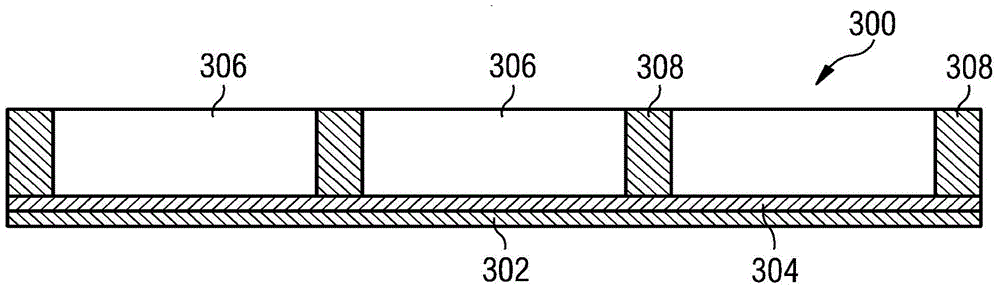

[0057] The illustrations in the figures are schematic.

[0058] A conventional method of etching electronic chips is a timed plasma etch process, where the plasma etch process is terminated when a target depth is reached. The process duration can be calculated using the known etch rate for the semiconductor substrate. However, variations in substrate etch rate (intra-wafer and / or from wafer-to-wafer) translate directly into variations in etch depth, and thus into thinned chips, making it impossible to have a true endpoint.

[0059] In another conventional approach, an etch stop layer is implemented in the semiconductor chip at a target depth to provide an etch stop after exposure of the etch stop layer due to the high selectivity of the etch process to the substrate above the stop layer, That is due to the high ratio of the etch rate of the substrate to the etch rate of the stop layer. However, this approach requires that an etch stop layer must be provided in the semiconduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More