Patents

Literature

34results about How to "Short current path" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

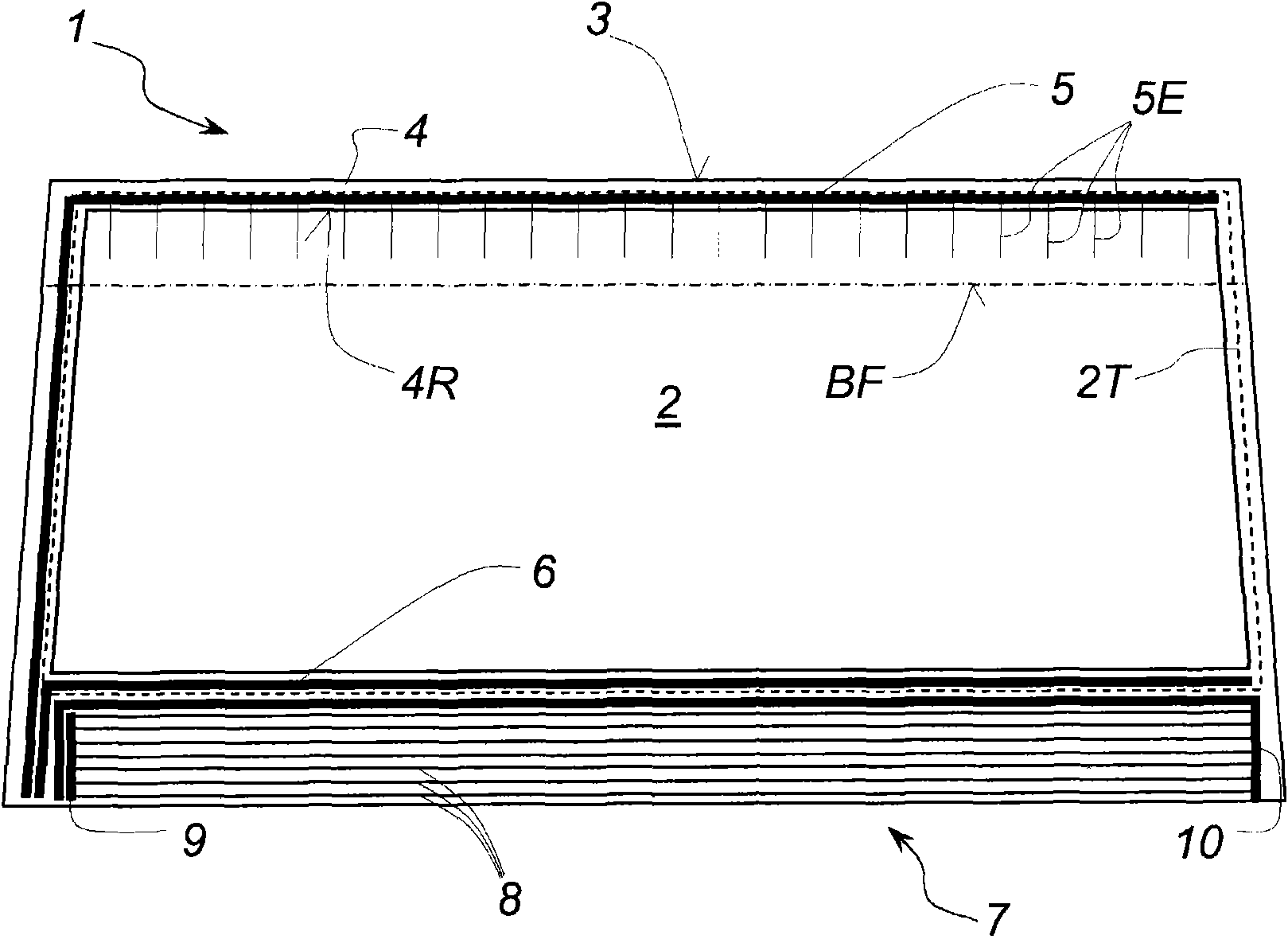

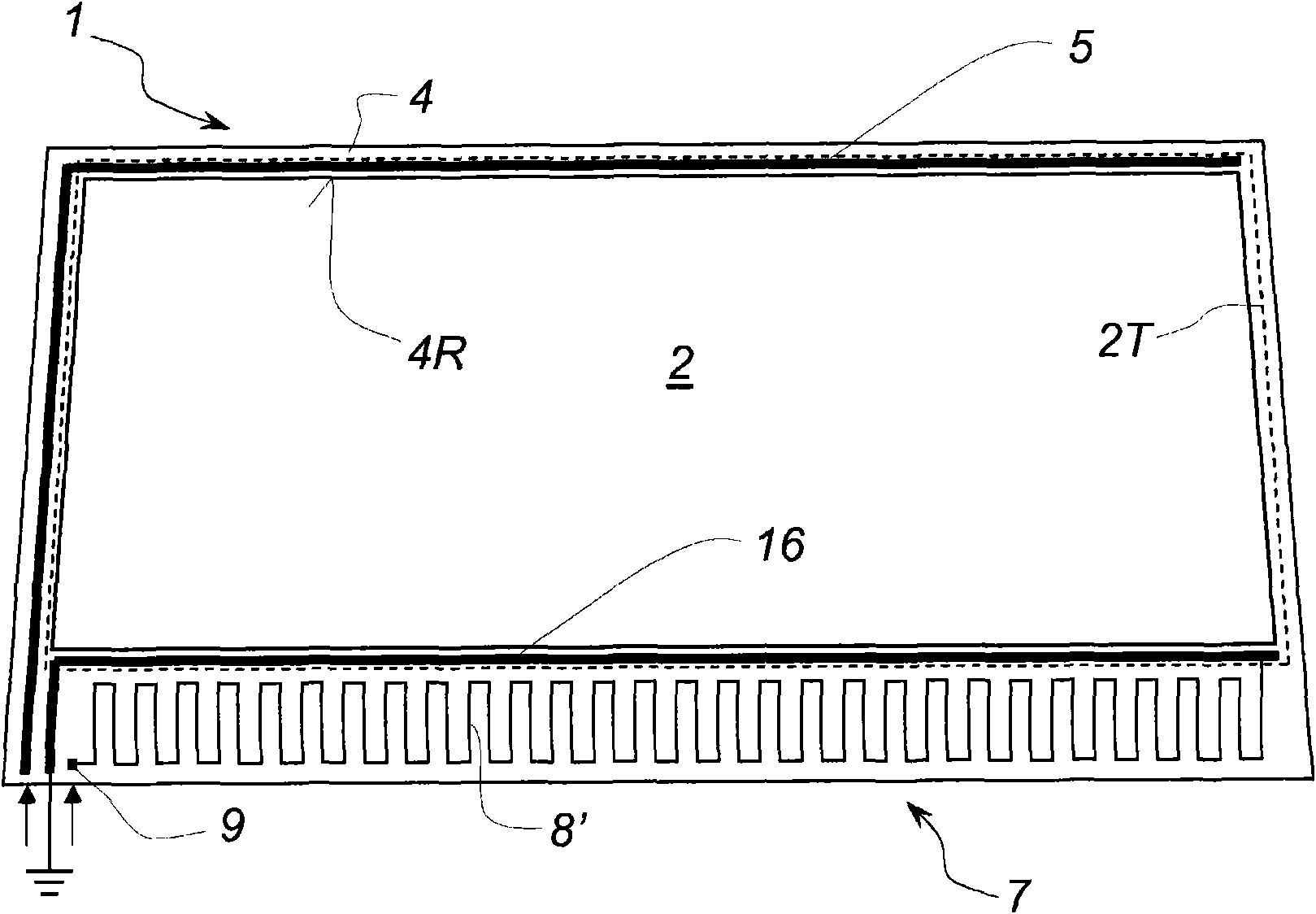

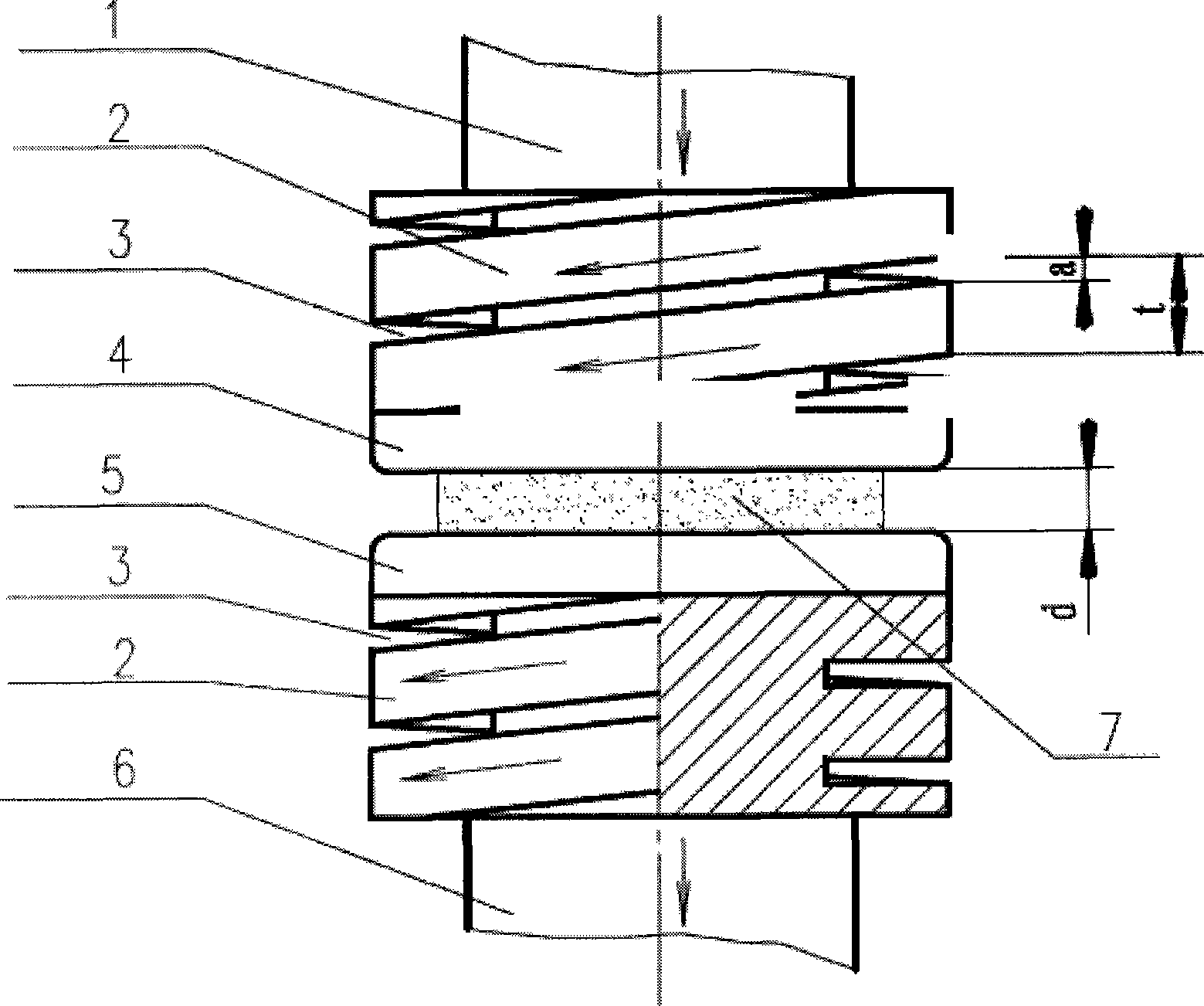

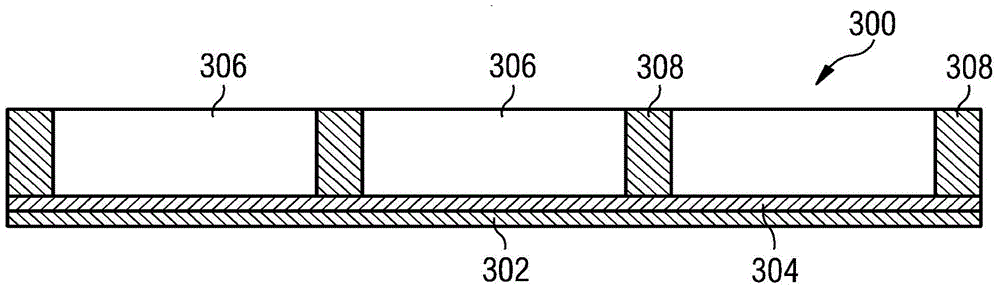

Transparent glass with heating coating

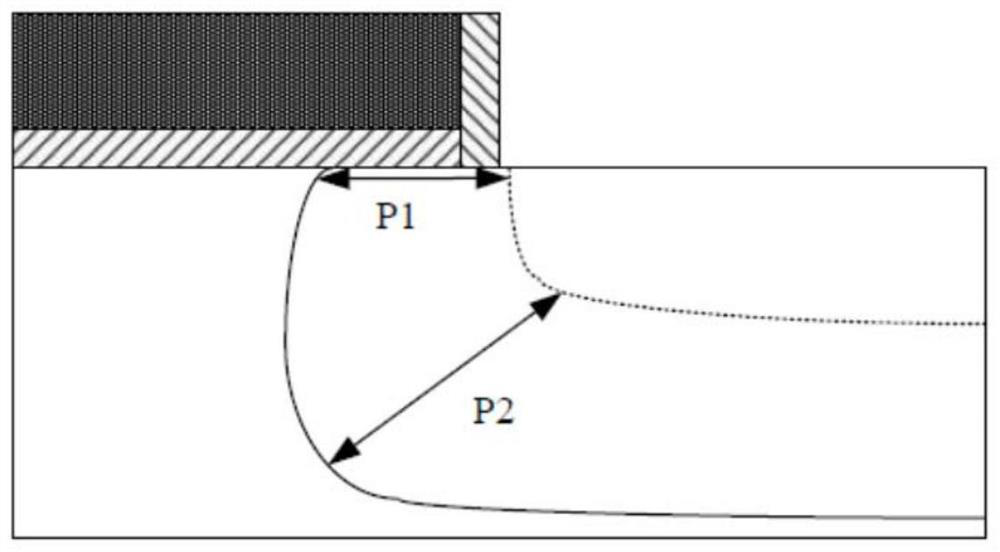

InactiveCN101653038AReduce distanceShort current pathTransparent/reflecting heating arrangementsGlass/slag layered productsElectrical resistance and conductanceVoltage

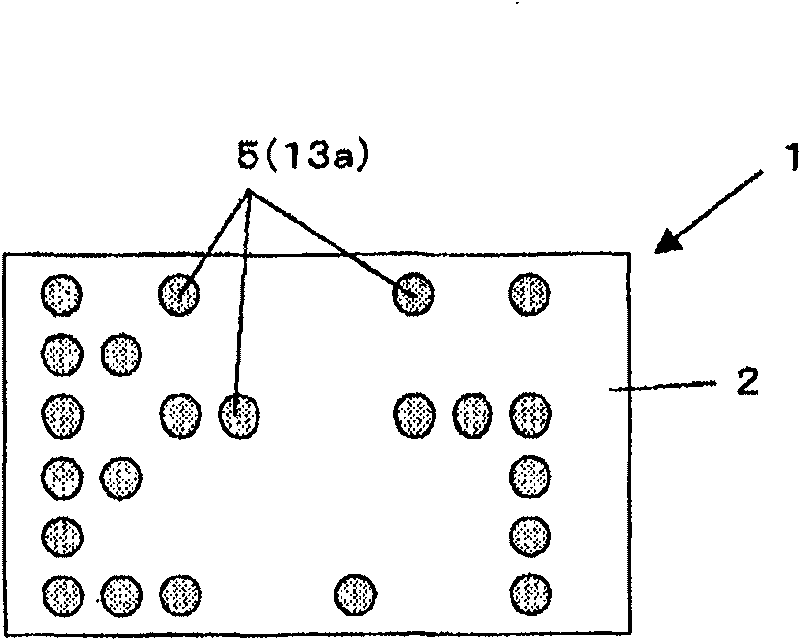

The invention relates to a transparent glass (1) having an electrically heating coating (2) extending on a large portion of the glass surface, in particular in the field of vision (4R), and electrically connected to at least two collecting conductors having a low electrical resistance (5, 6) so that, after applying an electric supply voltage to the collecting conductors, an electric current flowsin the heating field defined by the coating. According to the invention, a heating member (7) is provided with low electric-resistance conducting members (8, 8') such as wires and / or printed conducting tracks in an area of the surface that is not heated by the coating (2) and preferably located at the edge of the transparent glass (1) on the same face as the coating (2). It is thus possible to obtain an independent heating of said area of the surface while shortening the current paths in the coating with a relatively high electric resistance.

Owner:SAINT-GOBAIN GLASS FRANCE

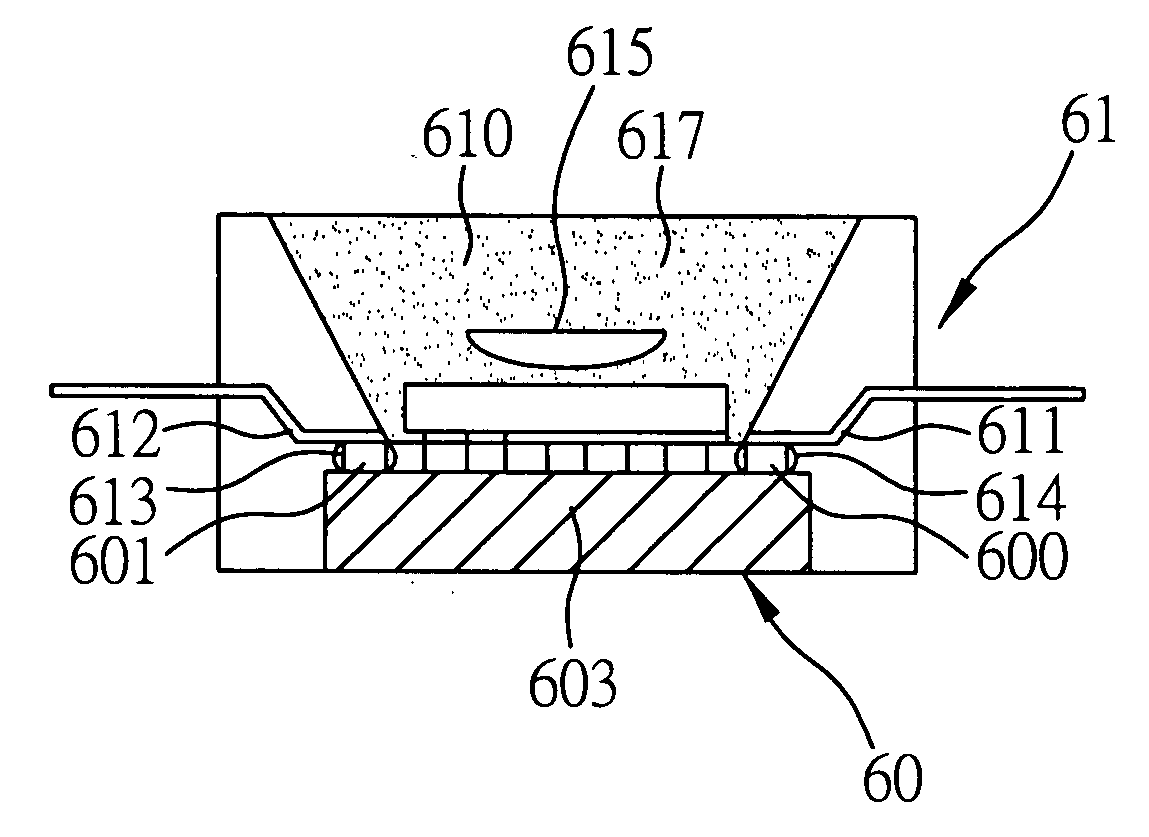

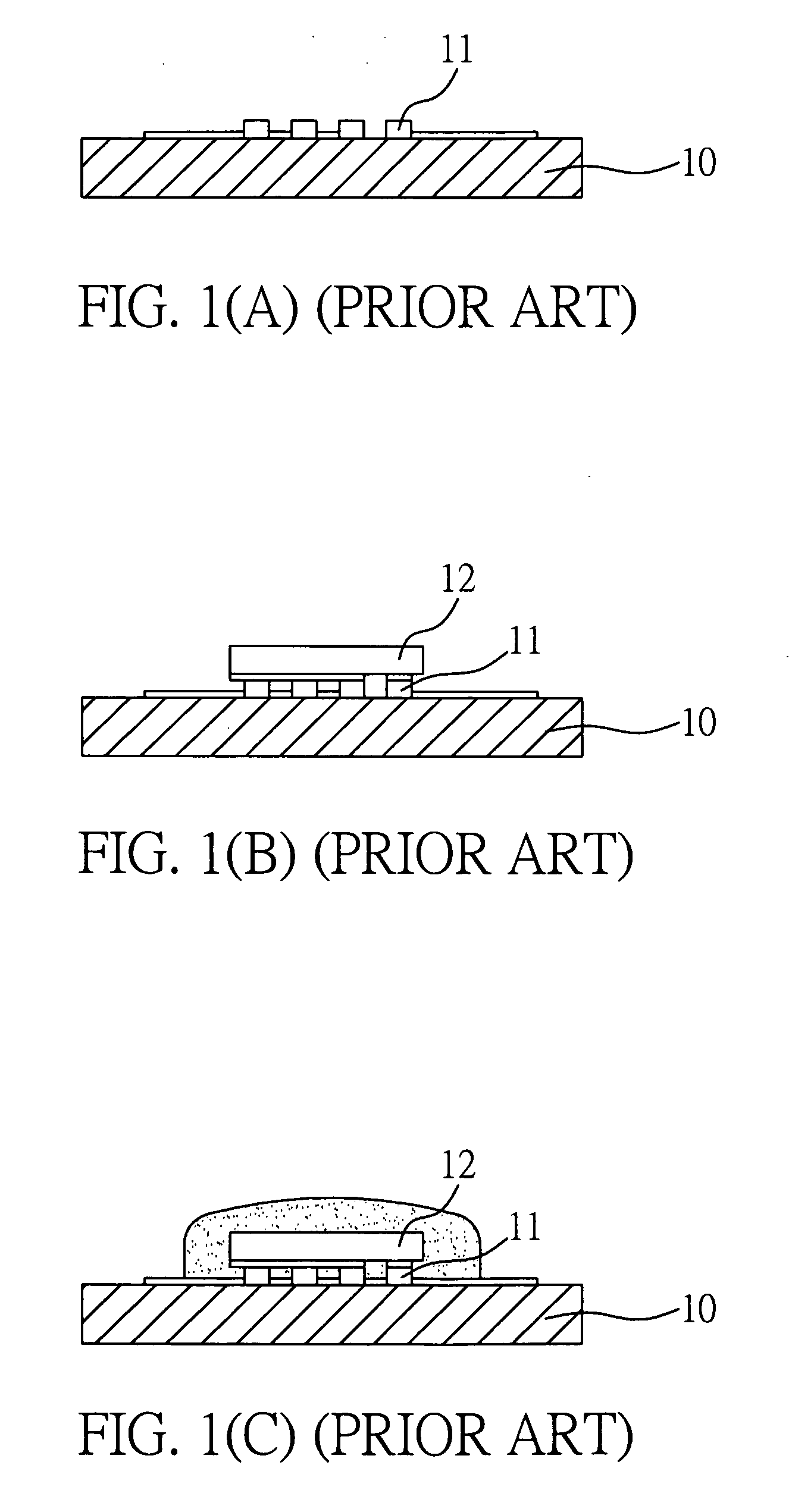

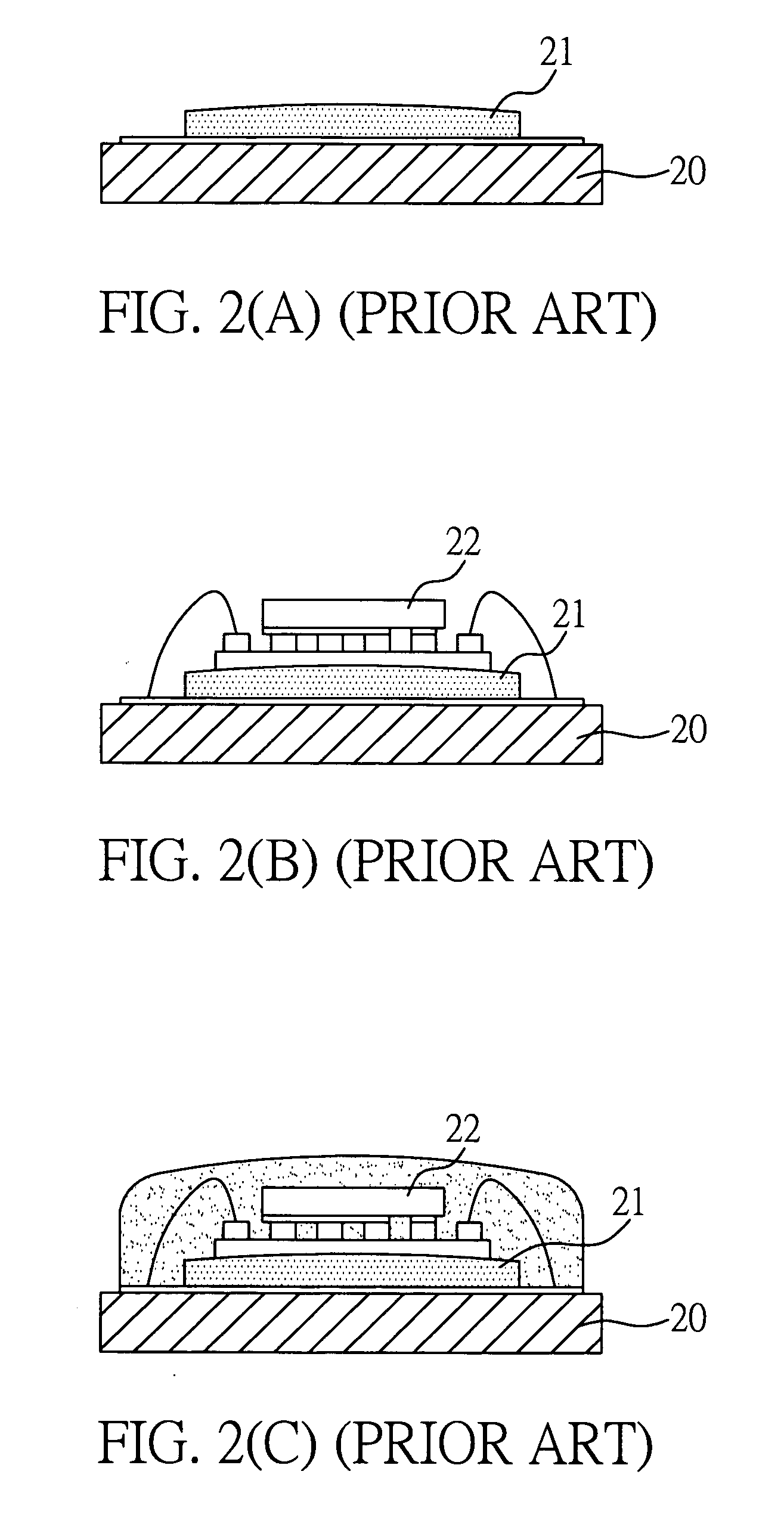

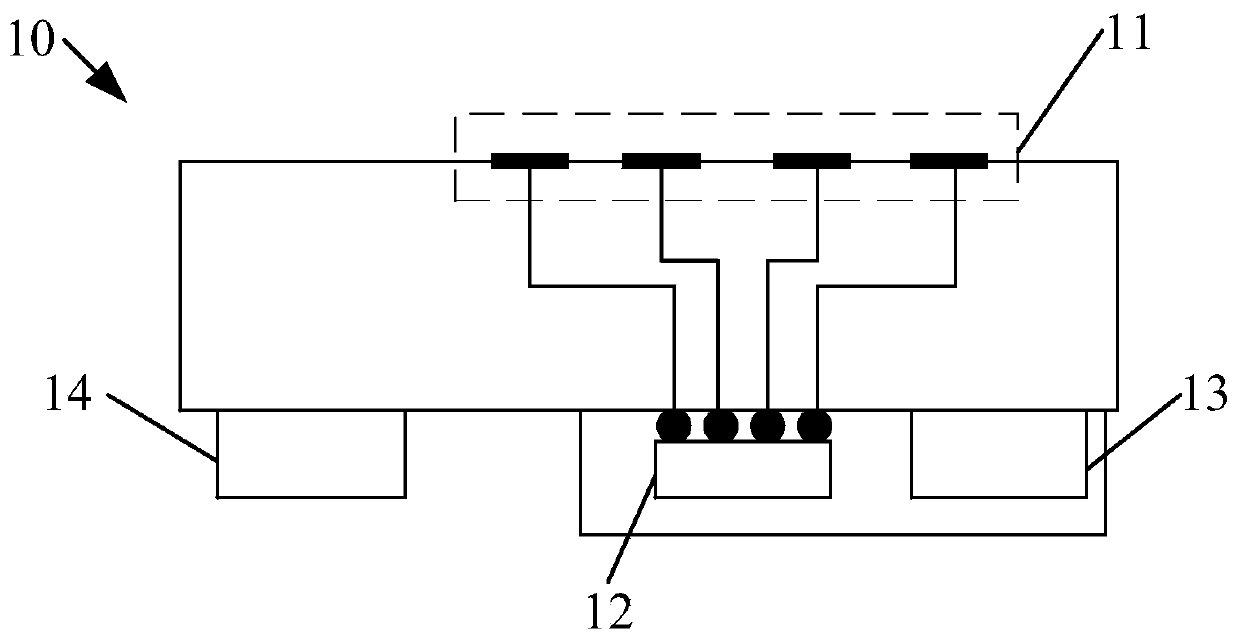

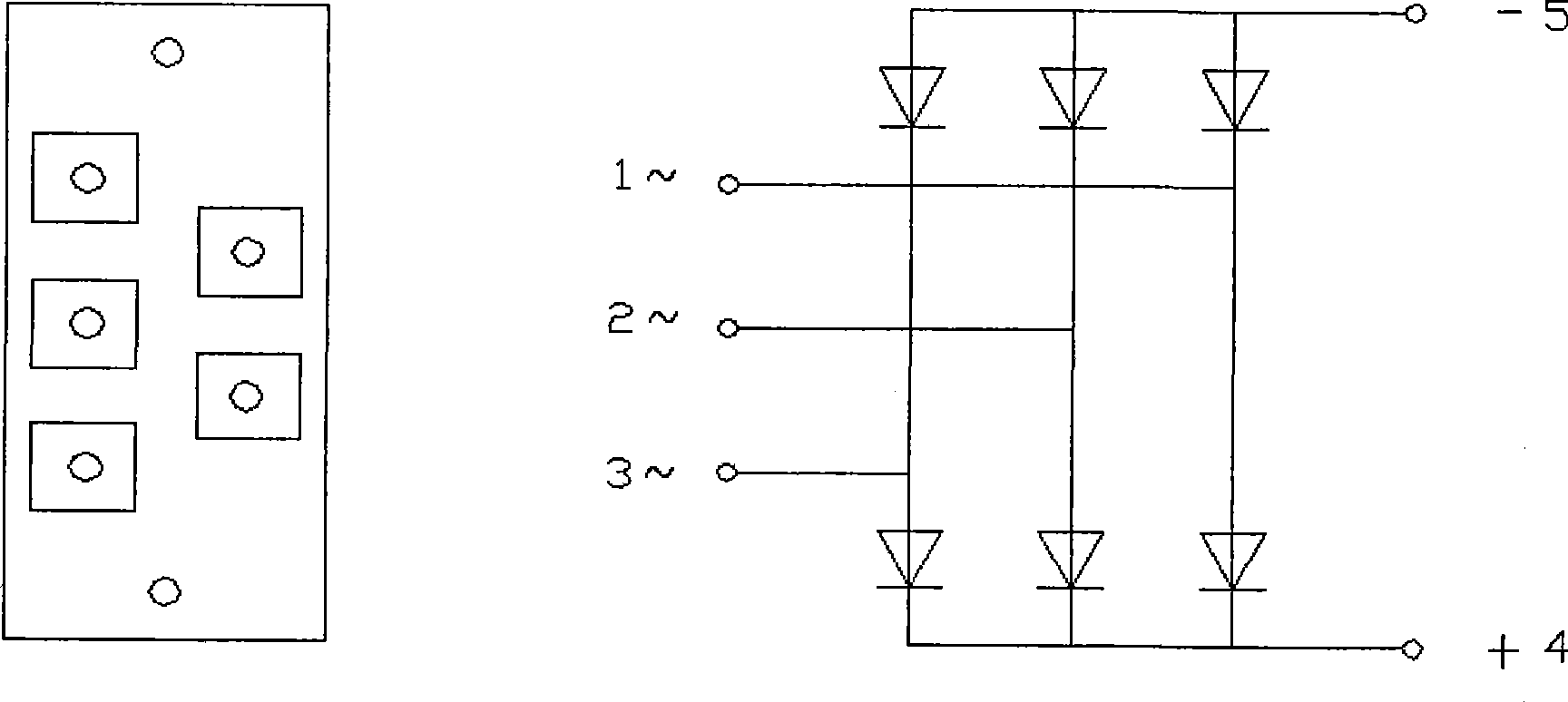

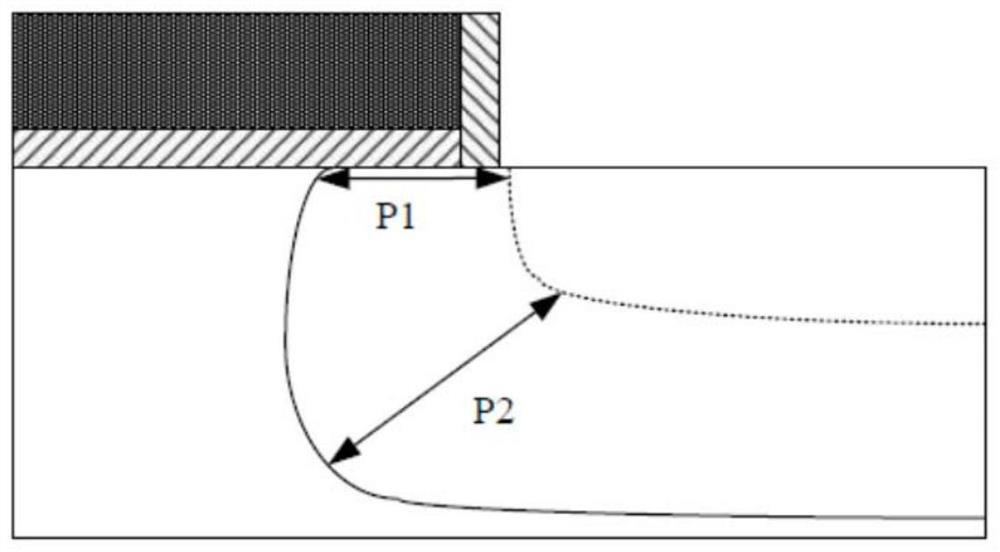

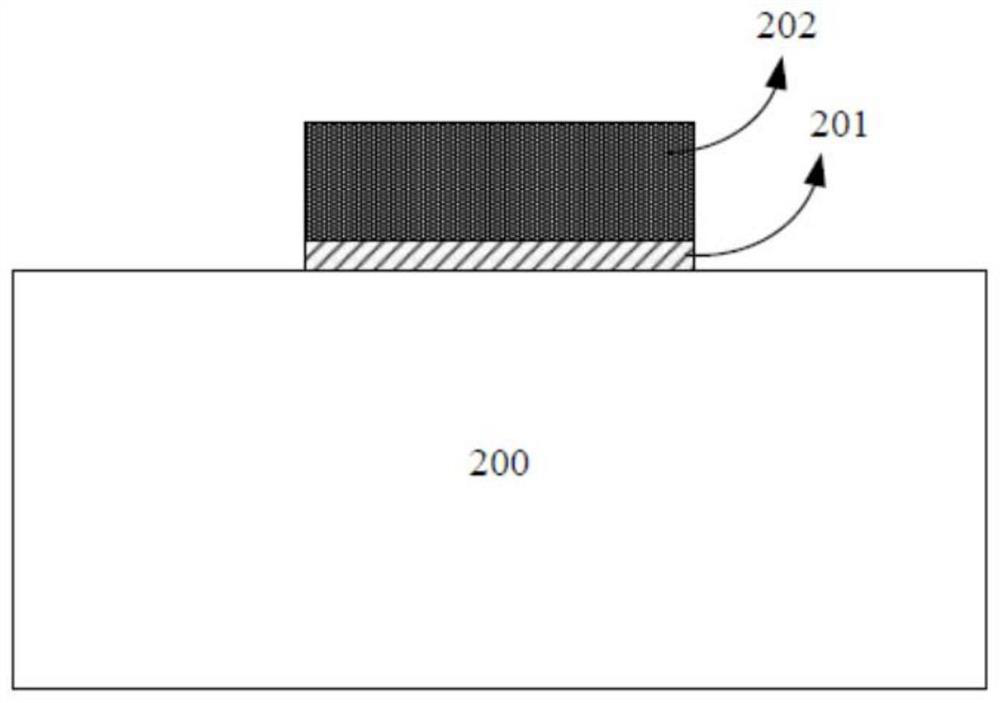

Light emitting device

InactiveUS20070069219A1Short current pathReduce thermal resistanceSolid-state devicesSemiconductor devicesElectrical connectionThermal resistance

A light emitting device is proposed, which emits light while connected to the power. The light emitting device includes a light emitting element having at least two electrodes disposed at the side of the light output surface thereof; and a base member having a recess and lead portions corresponding to the electrodes, the light emitting element being mounted on the base member and received in the recess, wherein the light output surface faces toward opening of the recess that becomes smaller while approaching the light output surface, and the electrodes are respectively in electrical connection with the lead portions that extend from the connection positions to outer edge of the base member for power connection. The light emitting device of the present invention has advantages of short current path, low series thermal resistance and low cost. In addition, the depth of the recess can further be increased to improve light collecting efficiency.

Owner:IND TECH RES INST

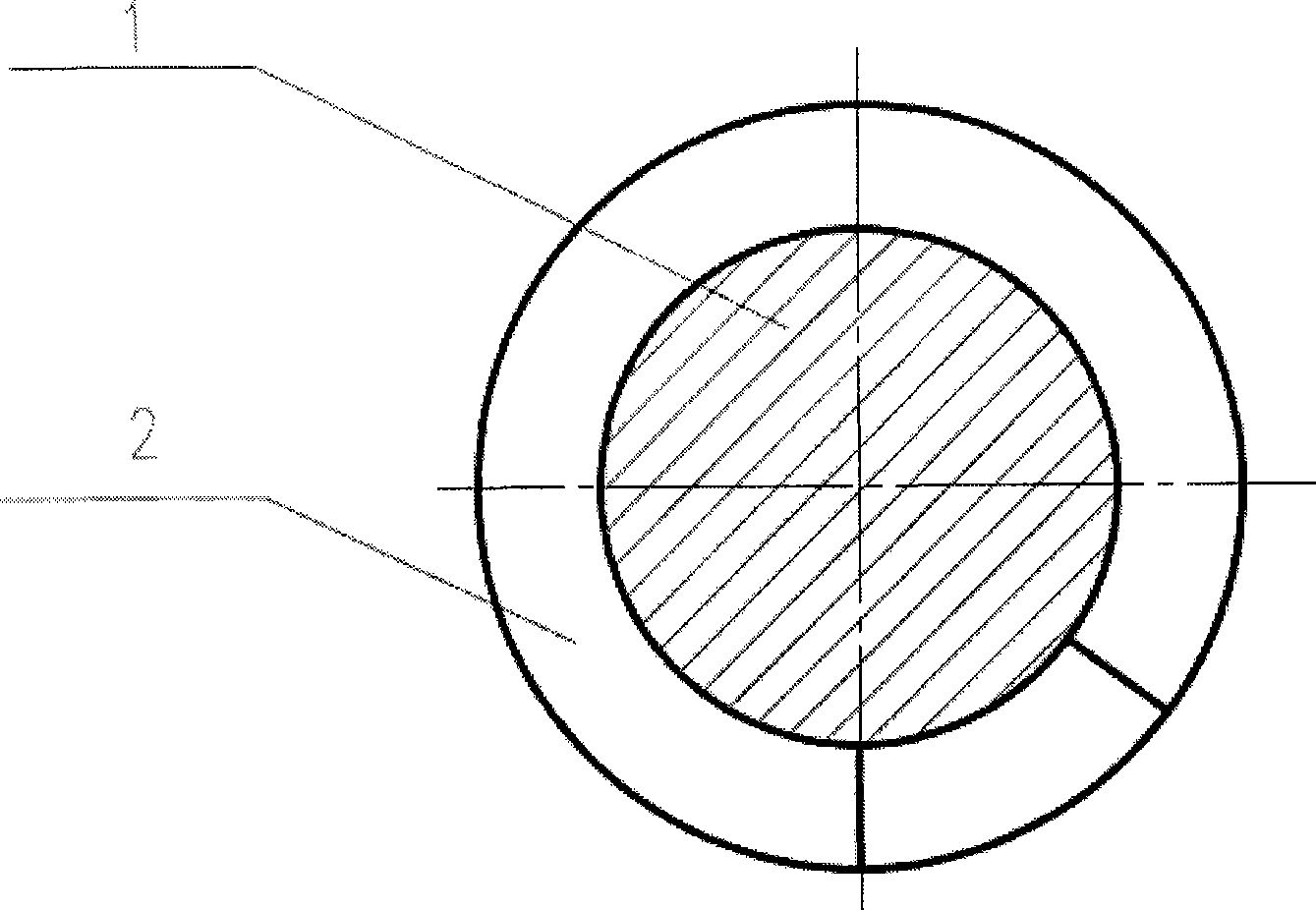

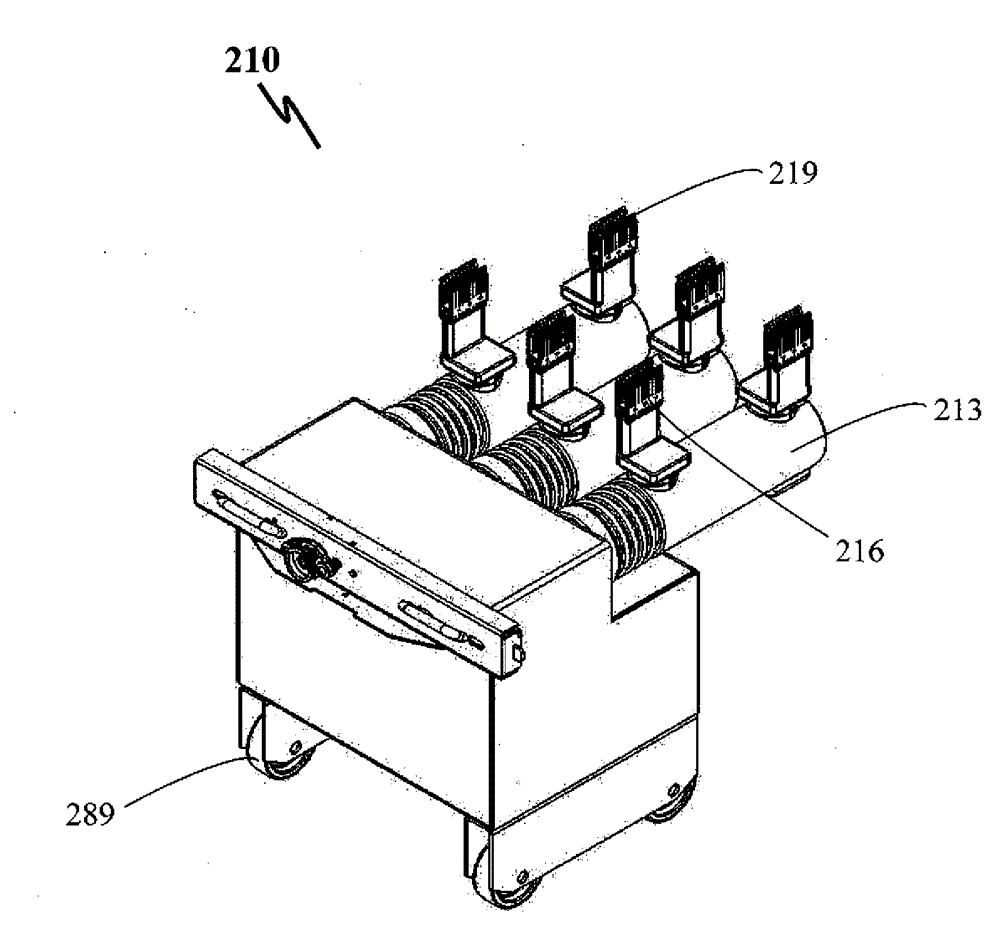

Vacuum switch tube for helical coil longitudinal magnetic field electrode

InactiveCN101425424AObvious superioritySignificant current pathHigh-tension/heavy-dress switchesAir-break switchesEngineeringVacuum switch

The invention provides a thread-coil type longitudinal magnetic field electrode vacuum switching tube which relates to the technical field of vacuum switches. The invention aims at providing a vacuum switching tube which has the arrangement disposal of the thread-coil type longitudinal magnetic field electrode so that the contradiction between the current conduction capacity and the short circuit current on-off capacity can be solved better. The vacuum switching tube comprises a moving conducting rod, a fixed conducting rod, a spiral coil, a spiral groove, a moving contact and a fixed contact which form a conducting loop. A coil of the vacuum switching tube takes the shape of a spiral body, and the turning direction of two thread coils arranged on a moving conductor and a fixed conductor is the same, and the moving contact and the fixed contact connected with the two thread coils are oppositely and longitudinally arranged. In the invention, the produced longitudinal magnetic field causes the vacuum arc produced between the contacts to keep in a non-aggregated state during the live cut-off; and the vacuum arc is extinguished when the current of an external circuit exceeds zero point, thereby the on-off of the circuit is finished.

Owner:湖北汉光科技股份有限公司

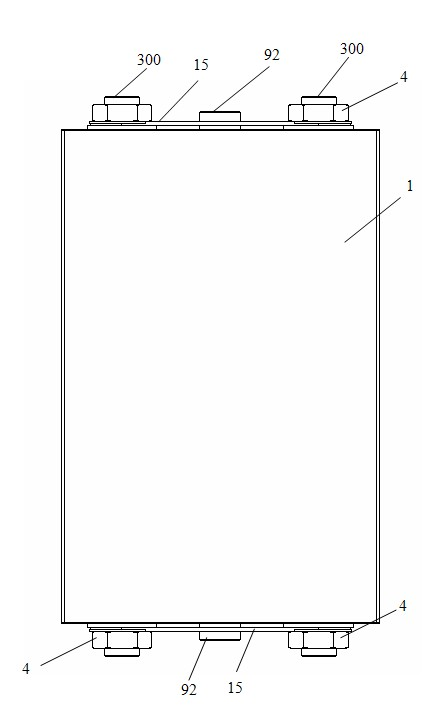

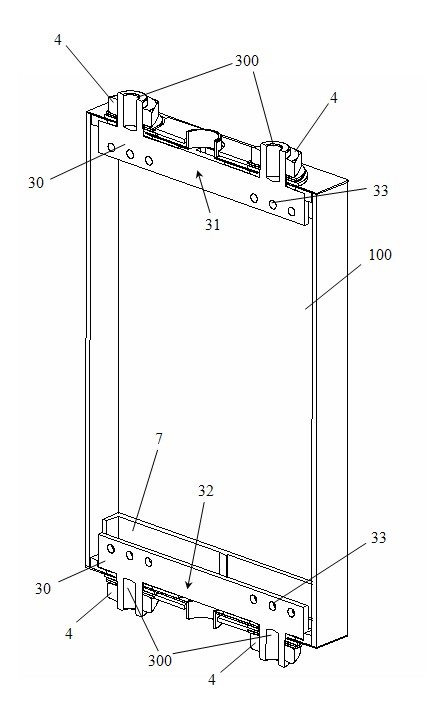

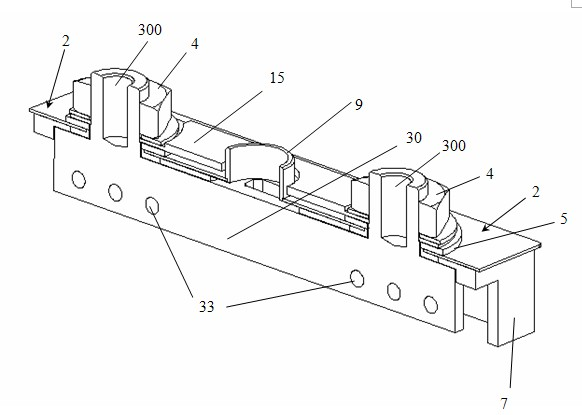

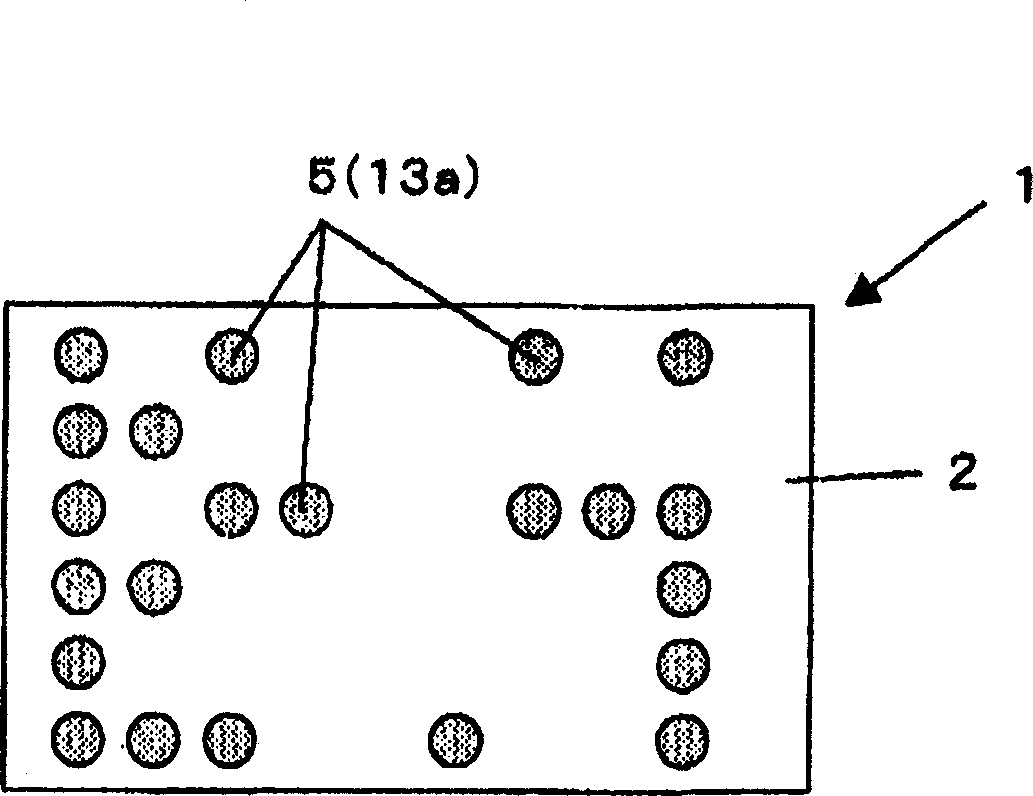

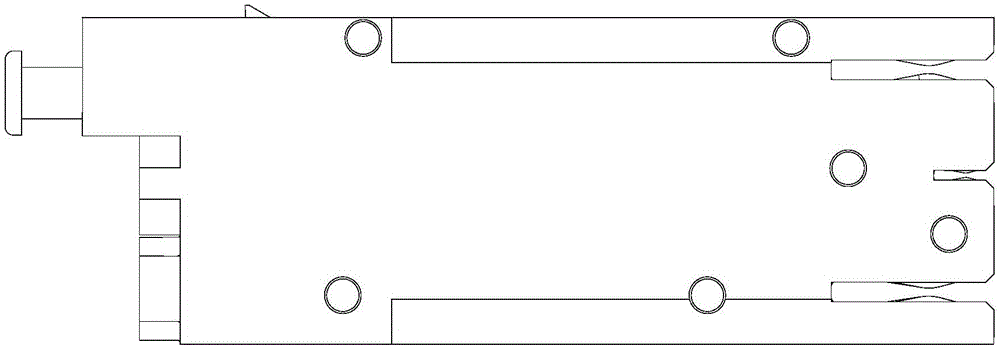

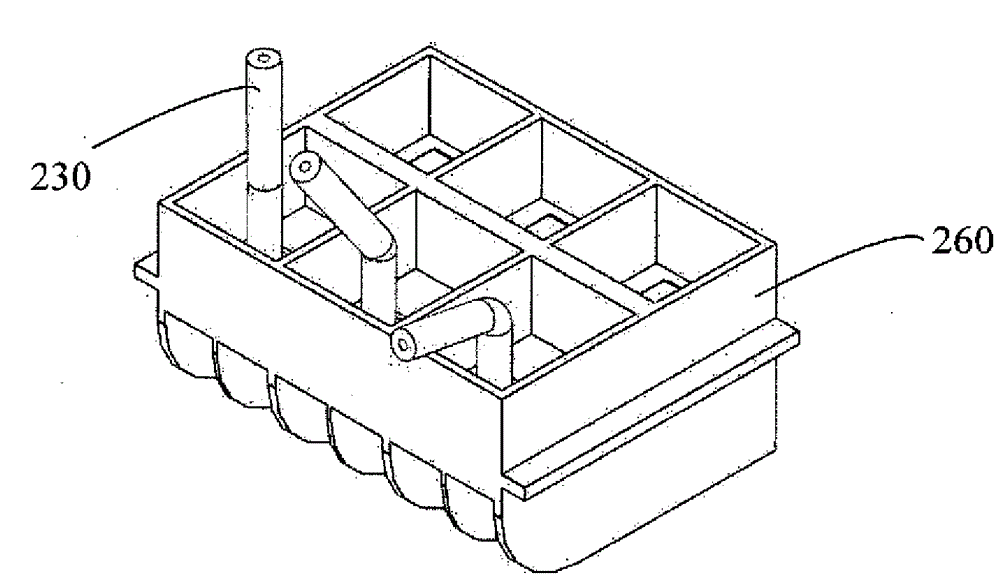

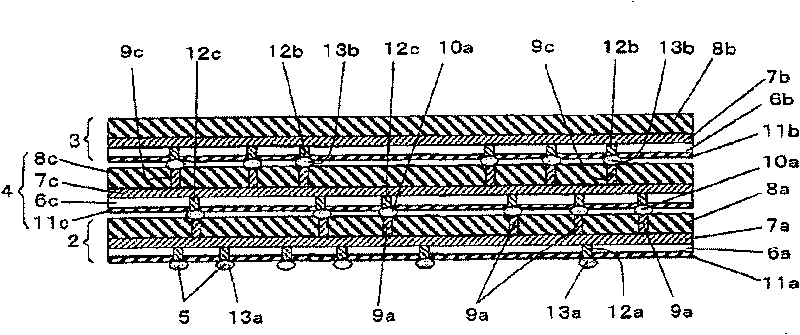

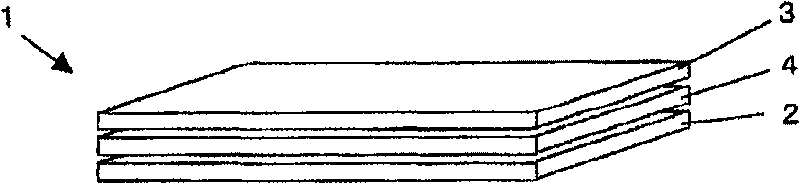

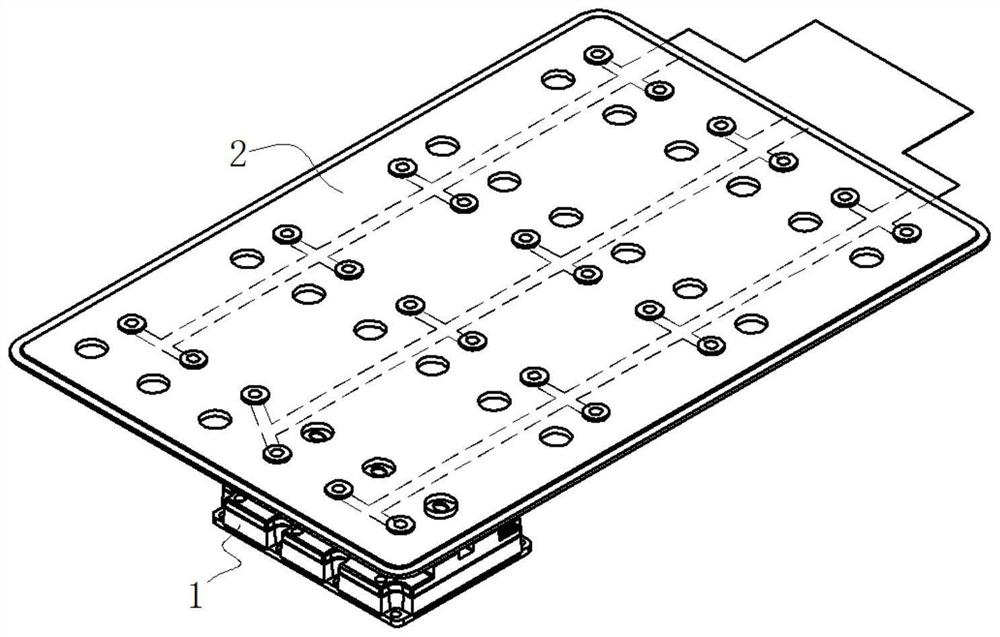

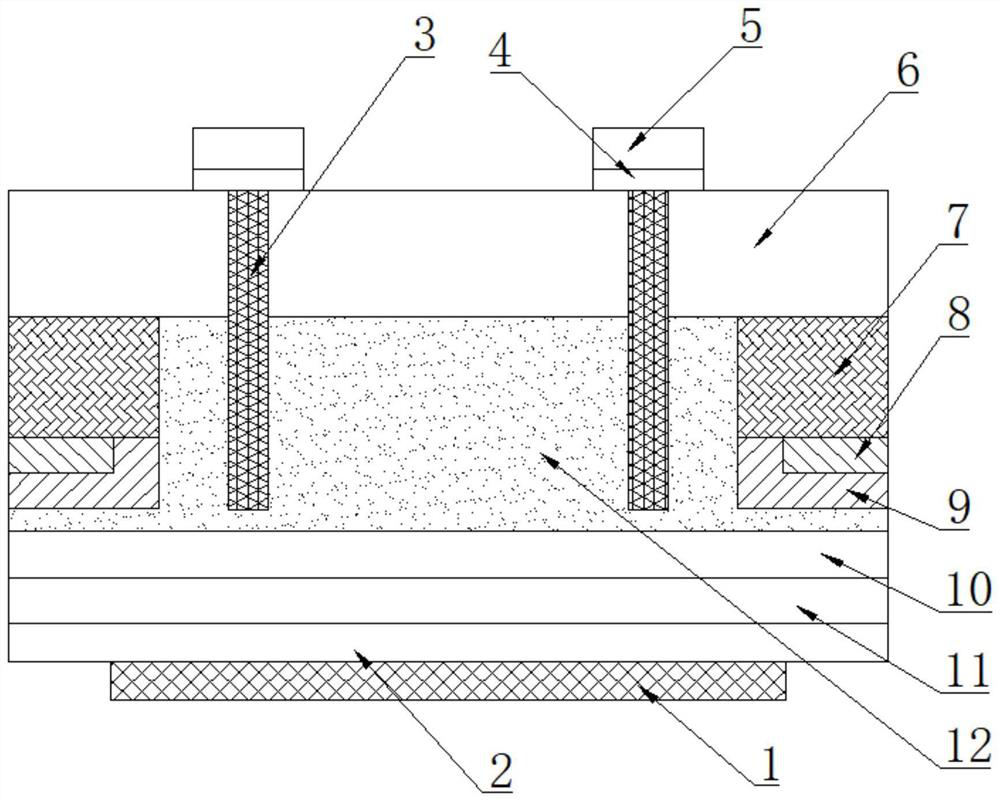

Lithium ion power battery with bidirectional current collectors

InactiveCN102013513AIncrease energy densityImprove rate discharge performanceElectrode carriers/collectorsSecondary cellsLithiumPower battery

The invention discloses a lithium ion power battery with bidirectional current collectors, which comprises a battery case (1). A battery core electrode group (100) is arranged in the battery case (1). An anode current collector (31) and a cathode current collector (32) are fixedly arranged at the upper and lower ends of the battery core electrode group (100) respectively. Cylindrical terminal posts (300) are arranged at the left and right ends of each of the anode current collector (31) and the cathode current collector (32) respectively. Battery covers (2) are arranged on the outer surfaces of the anode current collector (31) and the cathode current collector (32). The lithium ion power battery with the bidirectional current collectors adopts bidirectionally led-out external current collector structures, realizes a shortest current path and uniform current density, has increased energy density, improved rate discharge performance and relatively better current collection effect, and can be widely applied in the field of traffic and transportation.

Owner:TIANJIN LISHEN BATTERY

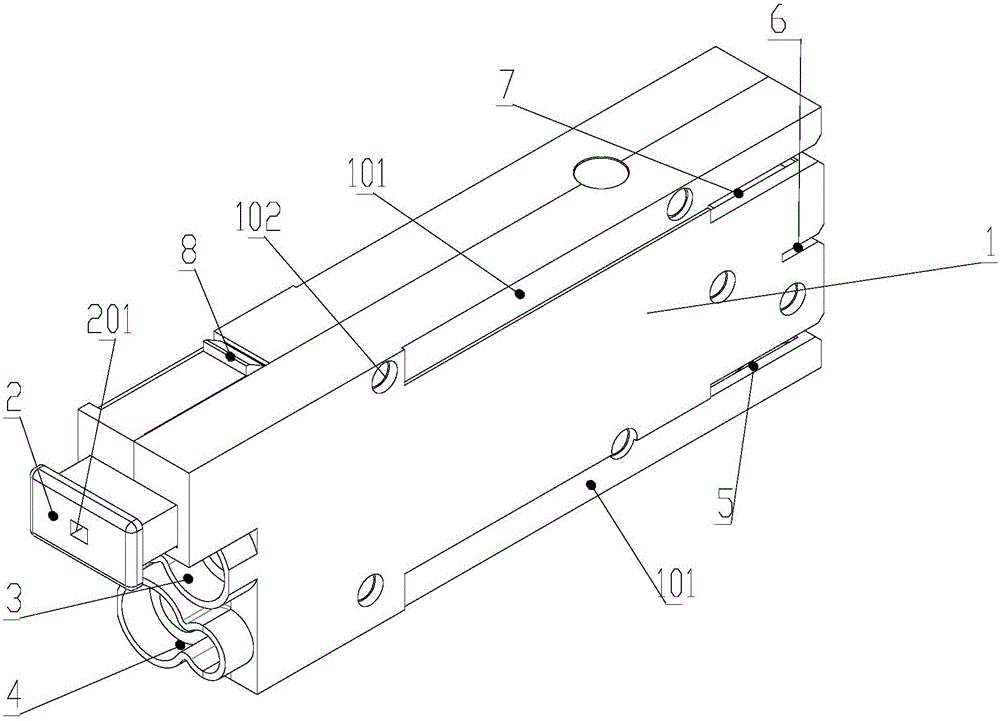

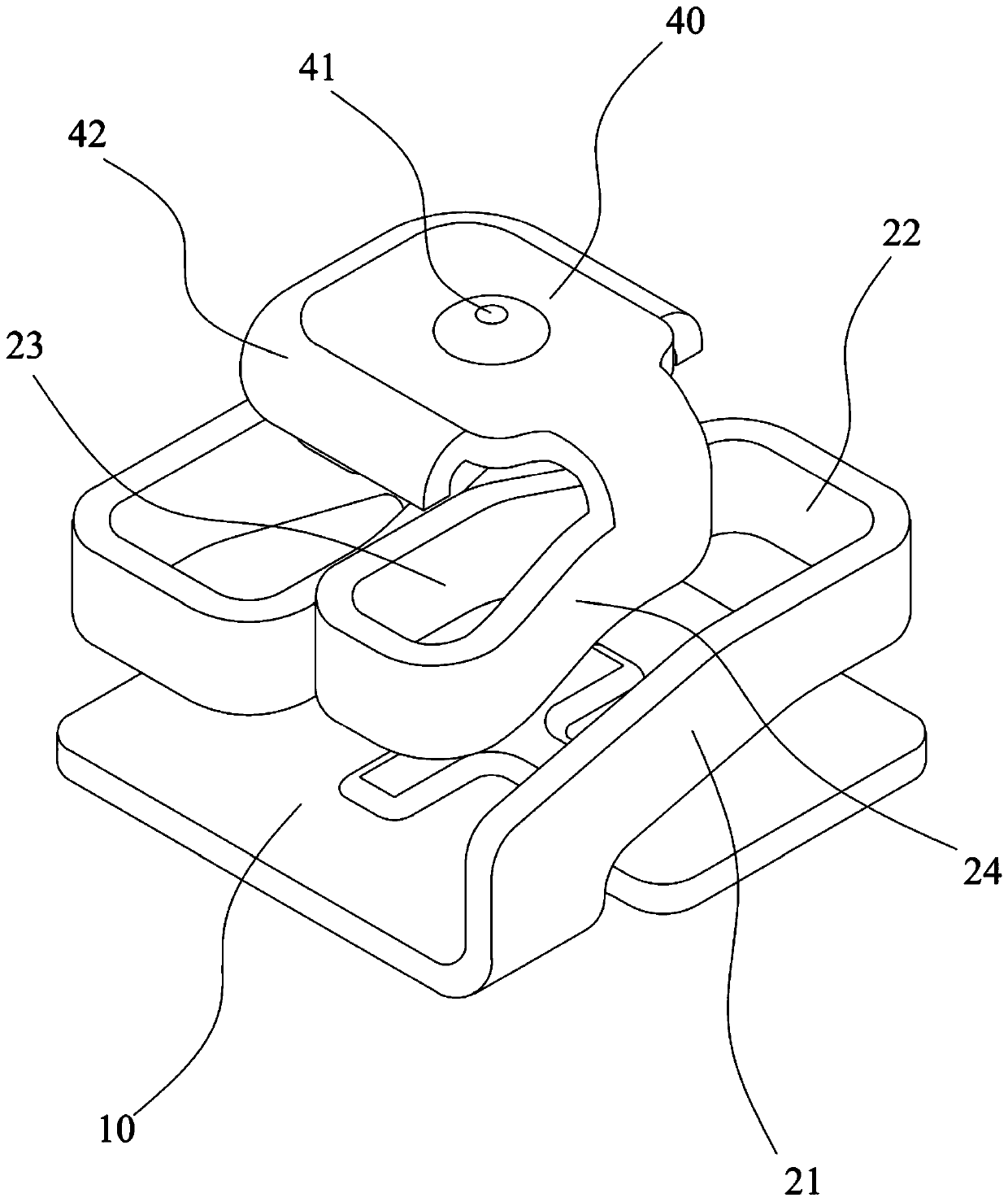

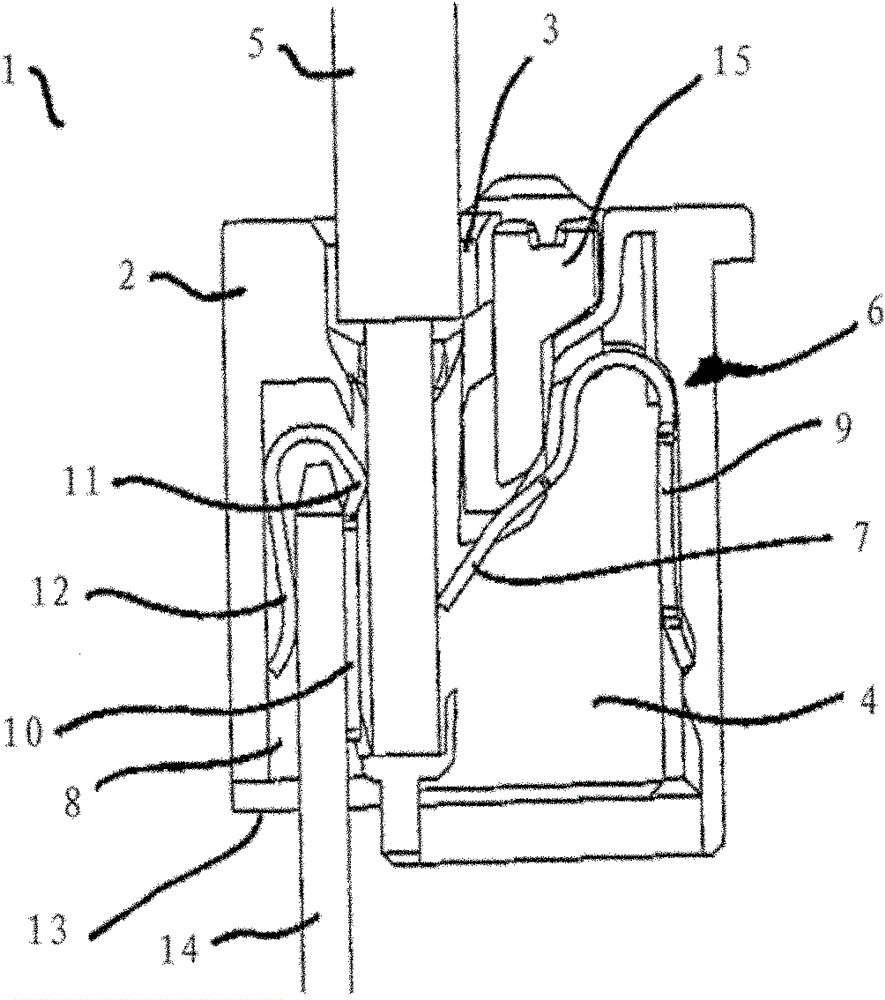

Plug-in connector

ActiveCN102195175ASave materialGood spring contactCoupling contact membersClamped/spring connectionsBusbarEngineering

In a plug-in connector (1), at least one part of the busbar element (10) is in each case arranged in the boundary area between an associated conductor entry opening (3) and an associated contact pin receiving opening (8) in such a manner that the part of the busbar element (10) is located between a contact pin (14) and an electric conductor (5) and electrically conductively rests against the contact pin (14) and the electric conductor (5). The busbar element (10) has a resilient contact area in the contact pin receiving opening (8) for electrically contacting the busbar element (10) by a spring force with a contact pin (14) which can be inserted into an associated contact pin receiving opening (8).

Owner:WAGO VERW GMBH

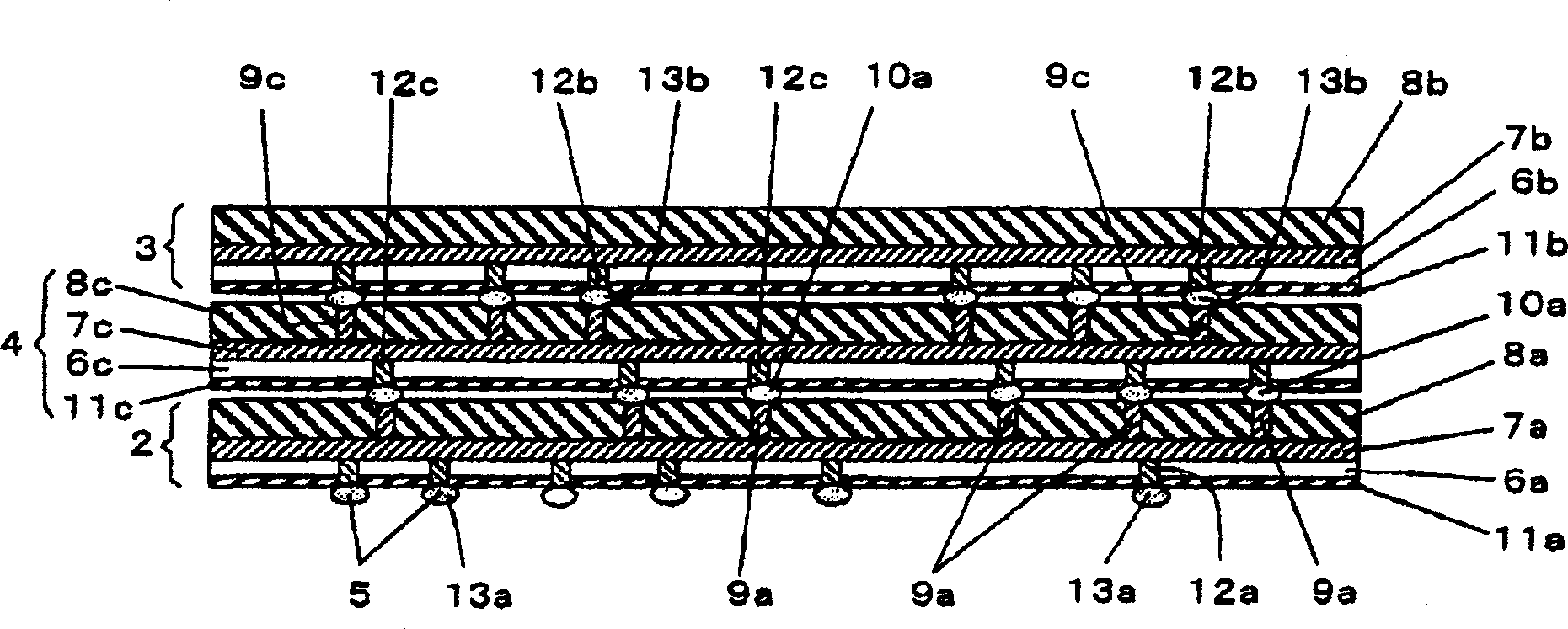

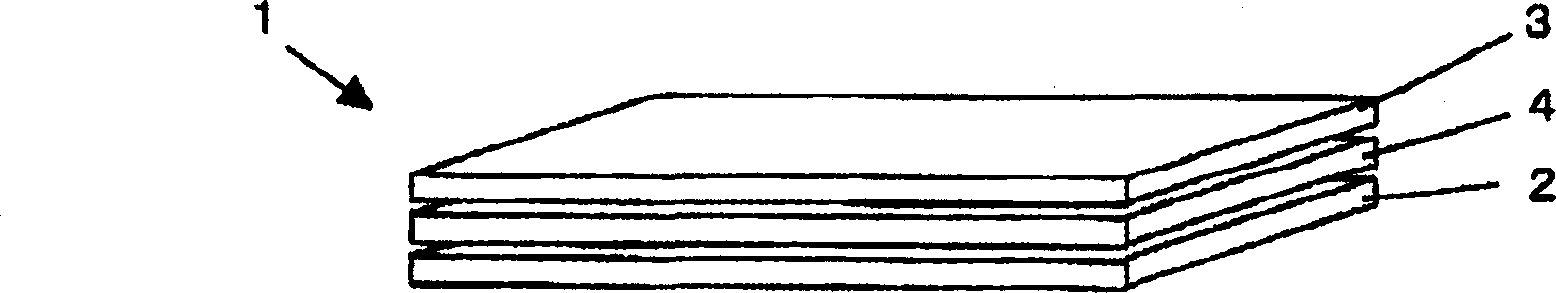

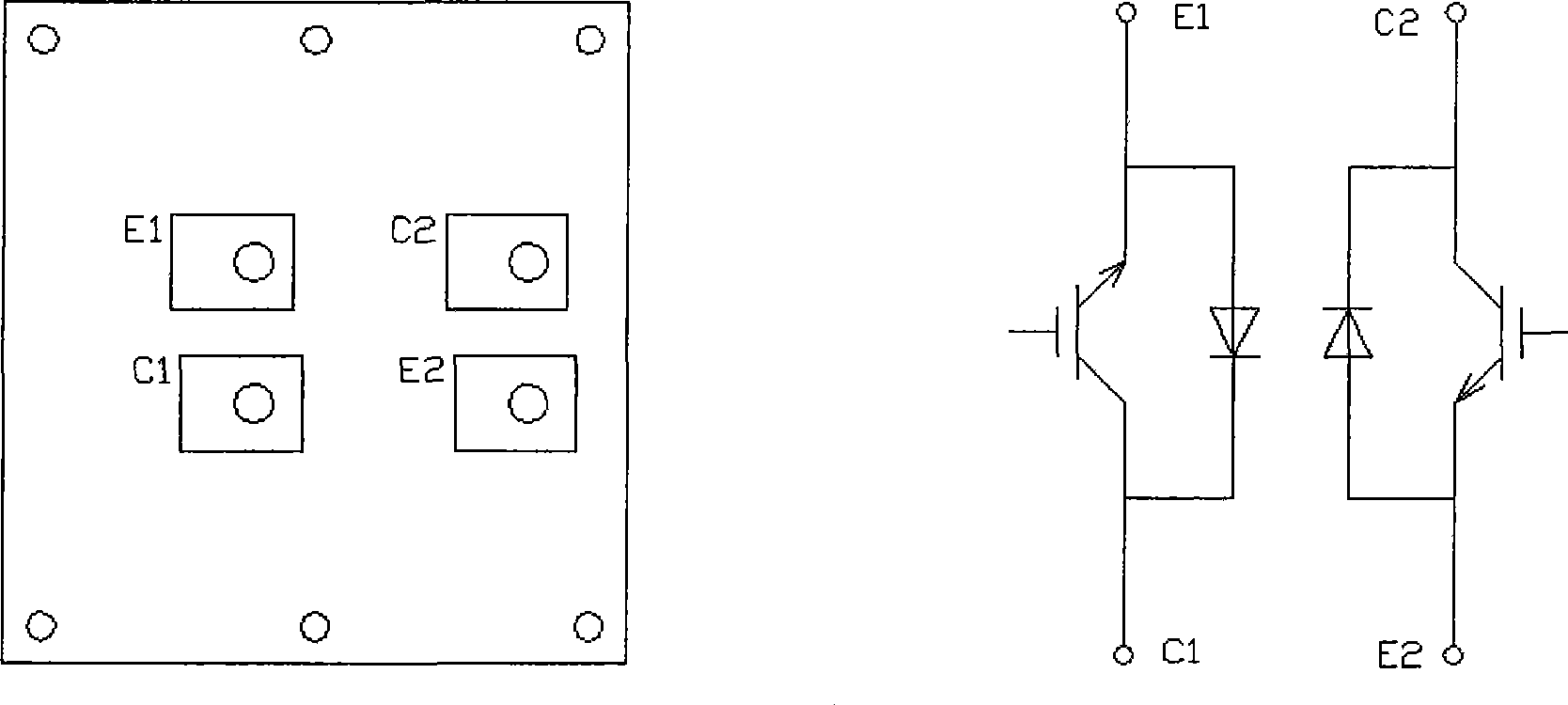

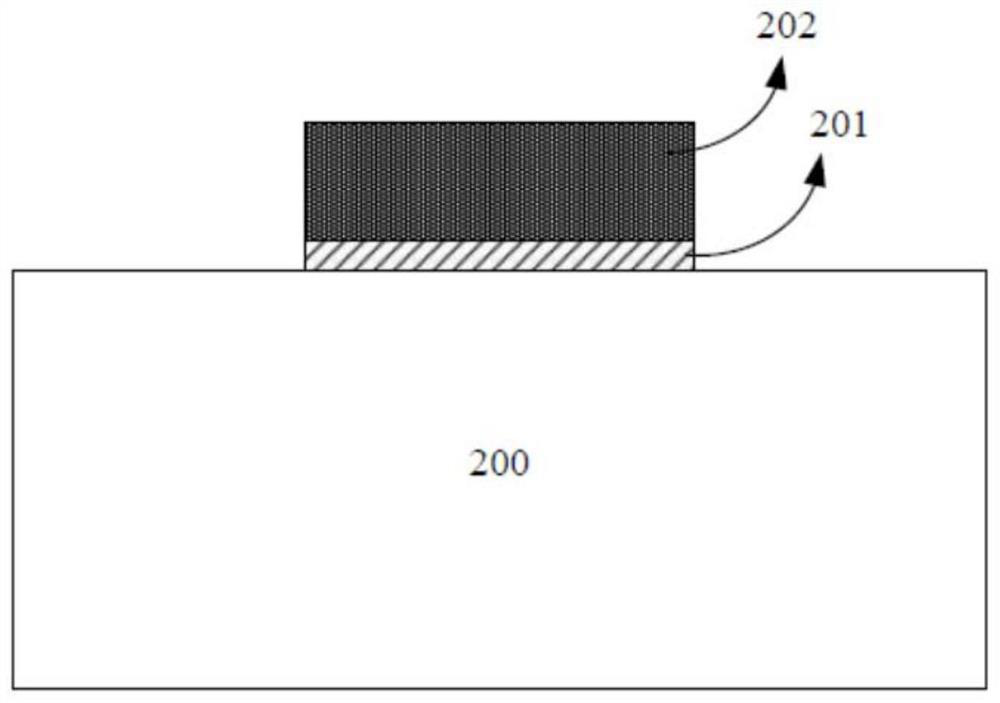

Semiconductor device and process for fabricating the same

ActiveCN1875481AAchieve thinningExcellent electrical propertiesSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A thin stacked semiconductor device suitable for high speed operation. A plurality of specified circuits are formed on one surface of a semiconductor substrate while being arranged, and wiring and insulating layers being connected electrically with the circuits are laminated and formed sequentially in a specified pattern to form a multilayer wiring part. At the stage for forming the multilayer wiring part, a filling electrode is formed on the semiconductor substrate such that the surface is covered with an insulating film, a post electrode is formed on specified wiring at the multilayer wiring part, a first insulating layer is formed on one surface of the semiconductor substrate, the surface of the first insulating layer is removed by a specified thickness to expose the post electrode, the other surface of the semiconductor substrate is ground to expose the filling electrode and to form a through-type electrode, forward end of the through-type electrode is projected by etching one surface of the semiconductor substrate, a second insulating layer is formed on one surface of the semiconductor substrate while exposing the forward end of the through-type electrode, bump electrodes are formed on both electrodes and then the semiconductor substrate is divided to form a semiconductor device. A plurality of semiconductor devices thus obtained are stacked and secured at the bump electrodes thus manufacturing a stacked semiconductor device.

Owner:阿奇里斯科技公司

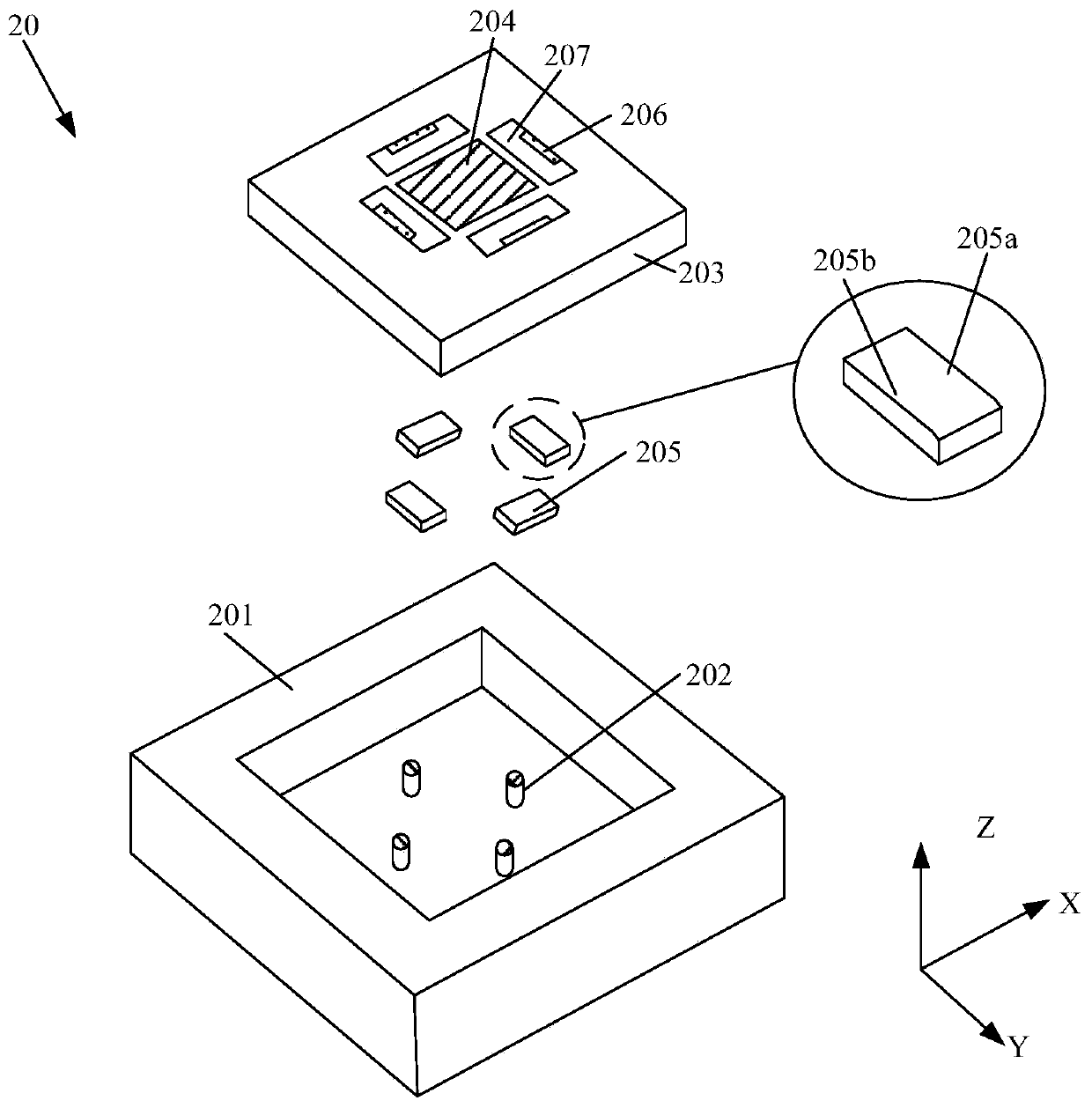

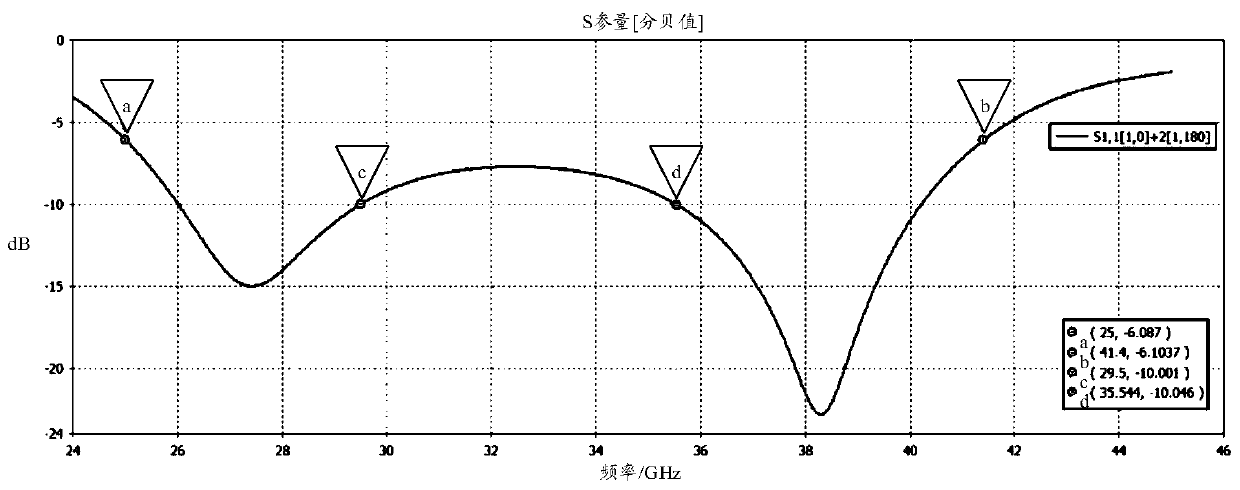

Antenna unit and electronic equipment

PendingCN110828987AShort current pathHigh bandwidthAntenna supports/mountingsRadiating elements structural formsElectrical connectionMillimetre wave

The embodiment of the invention provides an antenna unit and electronic equipment, relates to the technical field of communication, and aims at solving the problem that a millimeter wave antenna of existing electronic equipment covers less frequency bands; the antenna unit comprises a metal groove, M feeding parts arranged at the bottom of the metal groove, M feeding arm units and a first insulator arranged in the metal groove, and a target radiator borne by the first insulator; each feeding arm unit comprises a first feed arm, a second feed arm electrically connected with the first end of thefirst feed arm and a third feed arm electrically connected with the second feed arm, and the second end of the first feed arm in each feeding arm unit is electrically connected with different feedingparts in the M feeding parts; the third feed arm in each feeding arm unit is coupled with the target radiator, or the first feed arm, the second feed arm and the third feed arm in each feeding arm unit are coupled with the target radiator, and M is an integer greater than 1. The antenna unit is applied to the electronic equipment.

Owner:VIVO MOBILE COMM CO LTD

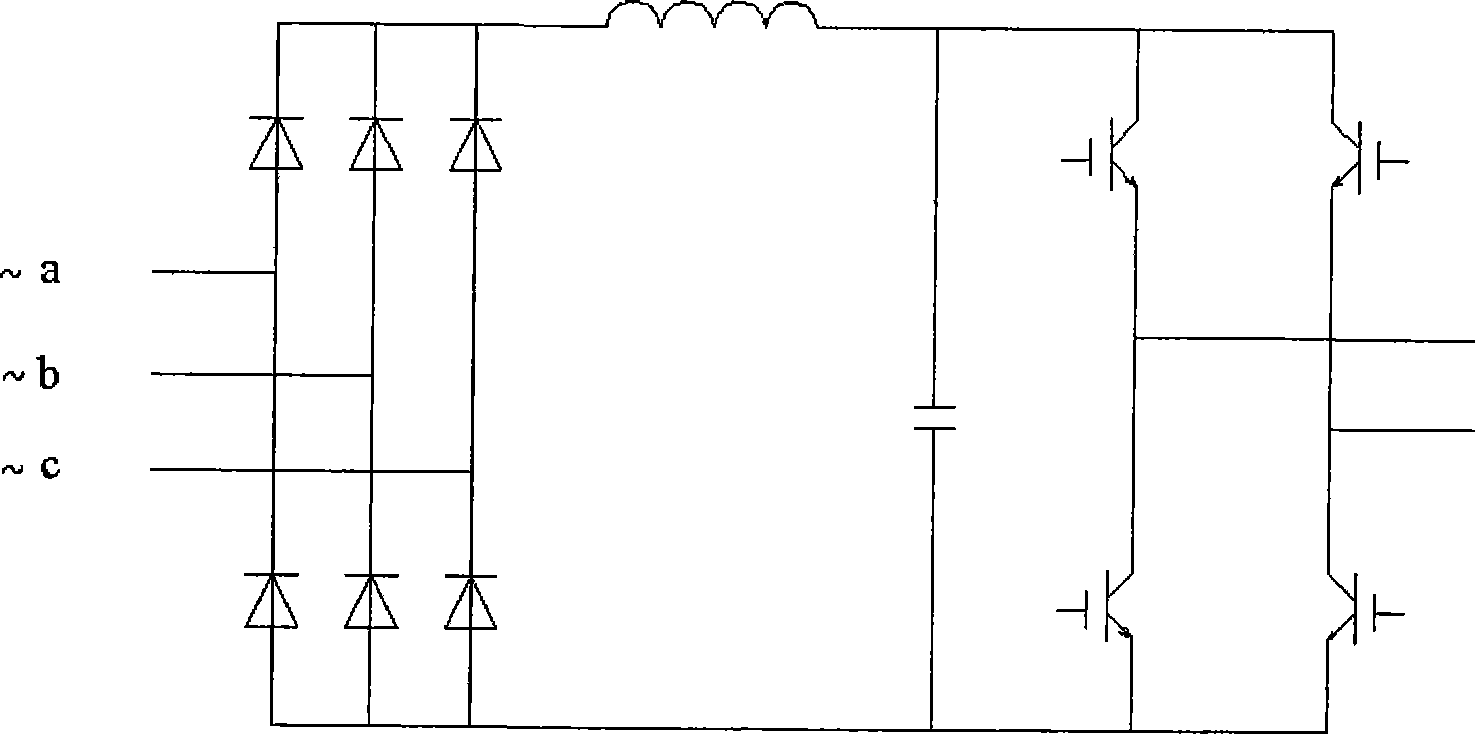

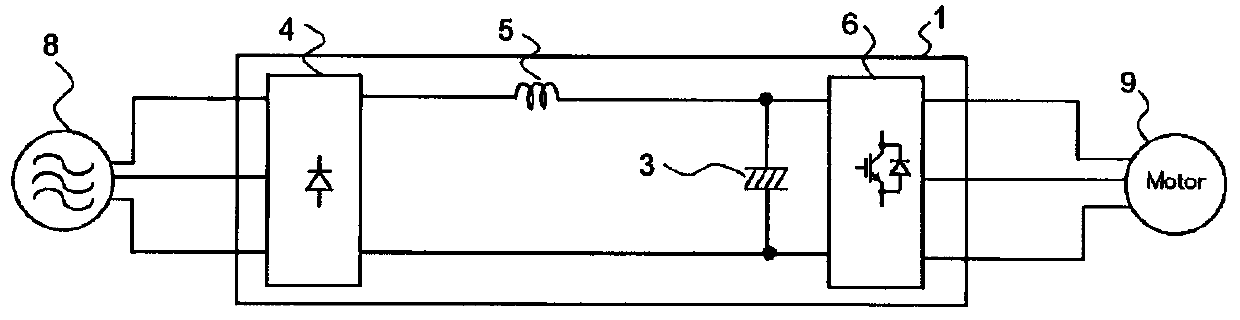

A type bus bar stacking method for large power pulse switch power supply

InactiveCN101478224AReduce electromagnetic radiationShorten connection lengthPower conversion systemsTransformerBusbar

The invention discloses a method for laminating A-type busbars of a high-power pulse switch power supply. The method is structurally characterized in that four rectifier bridge modules are selected to be connected in parallel and rectified, and two IGBT (insulated gate bipolar translator) modules are selected to output a main circuit; a filter capacitor, a power switching tube or a rectifier, and an inductor or a transformer in the main circuit are placed close to each other; the directions of the components are determined, that is, in design of the high power pulse switch power supply, a capacitor plate, A, B, C, anode phase input copperplate are installed by copperplate lamination, therefore, the wiring is reduced, the influence of the lead inductance and resistance is eliminated, electromagnetic interference is further reduced and the purpose to inhibit electromagnetic interference is achieved.

Owner:INST OF MODERN PHYSICS CHINESE ACADEMY OF SCI

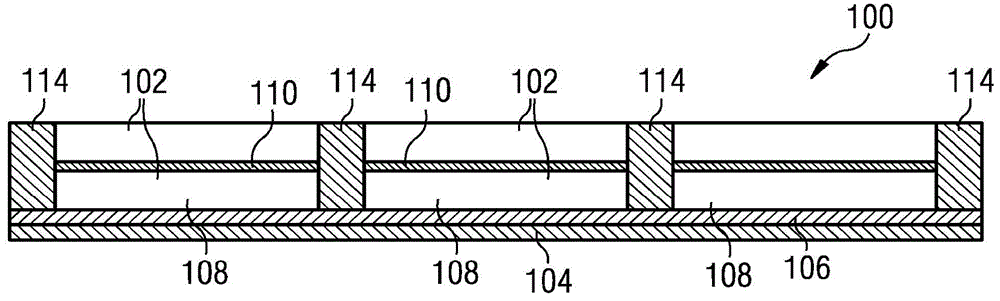

Removable indicator structure in electronic chips of a common substrate for process adjustment

ActiveCN104134607AFault robustReduce thicknessSemiconductor/solid-state device testing/measurementSolid-state devicesEtchingEngineering

A method of processing a plurality of packaged electronic chips being connected to one another in a common substrate is provided, wherein the method comprises etching the electronic chips, detecting information indicative of an at least partial removal of an indicator structure following an exposure of the indicator structure embedded within at least a part of the electronic chips and being exposed after the etching has removed chip material above the indicator structure, and adjusting the processing upon detecting the information indicative of the at least partial removal of the indicator structure.

Owner:INFINEON TECH AG

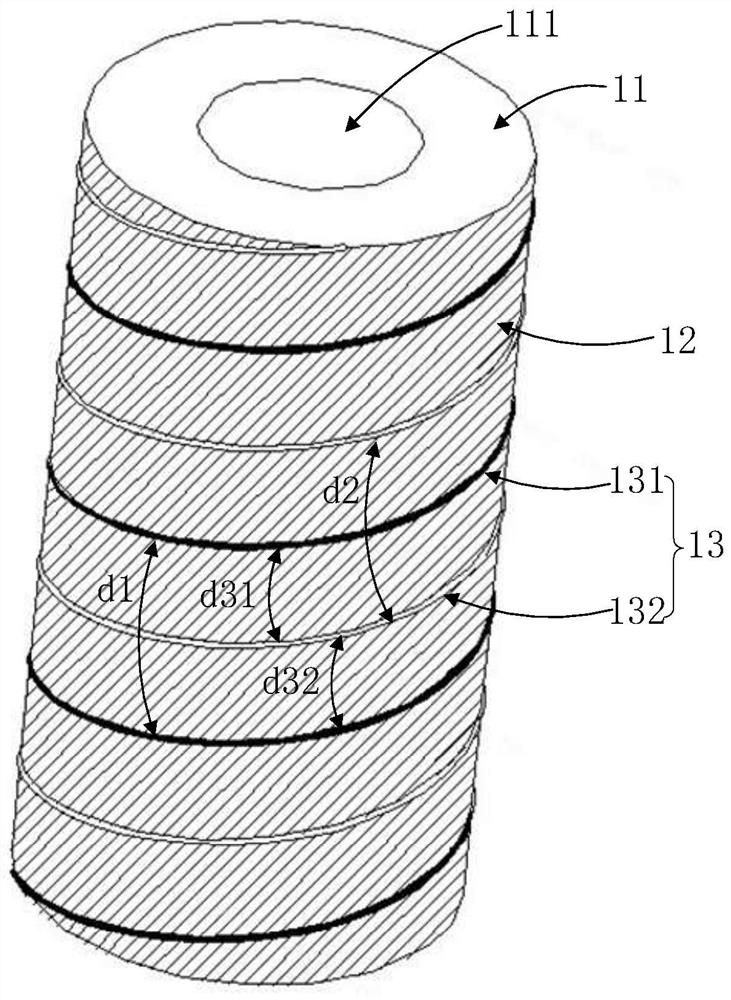

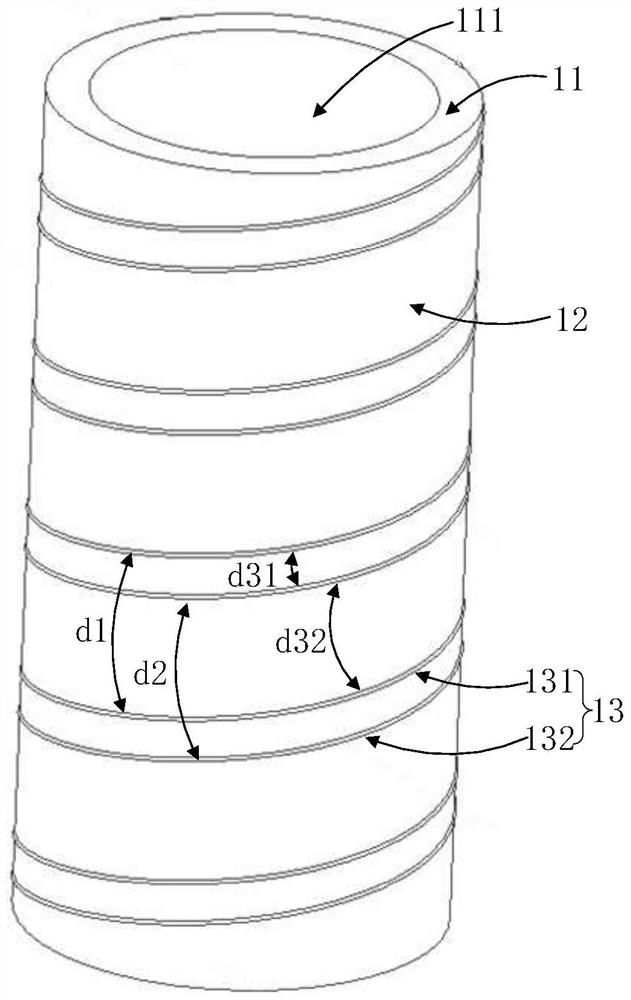

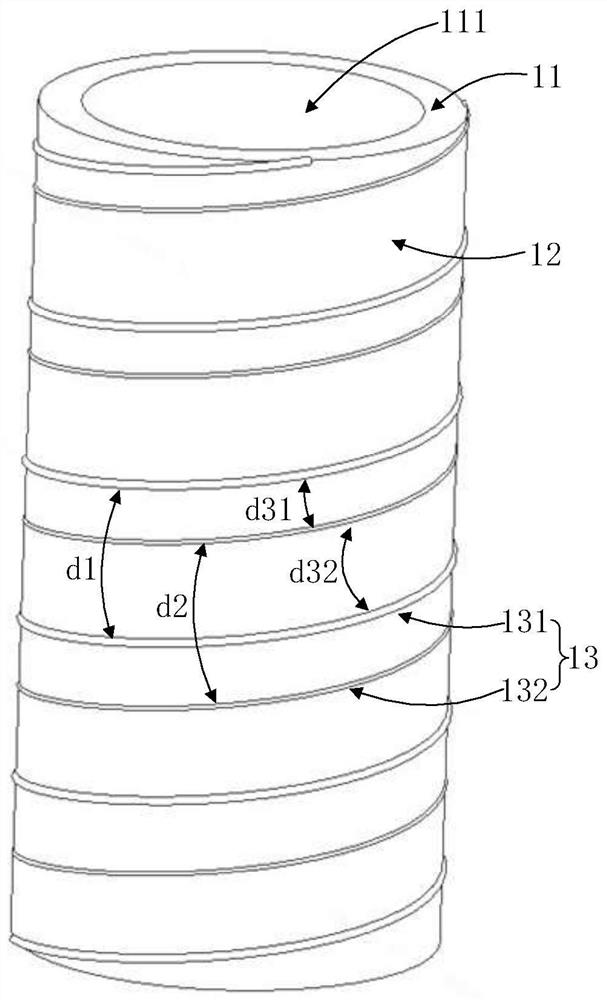

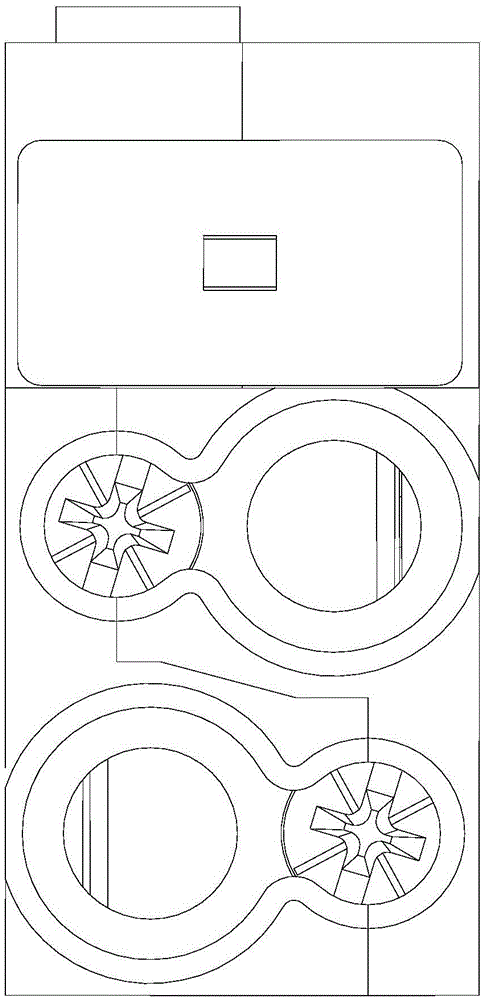

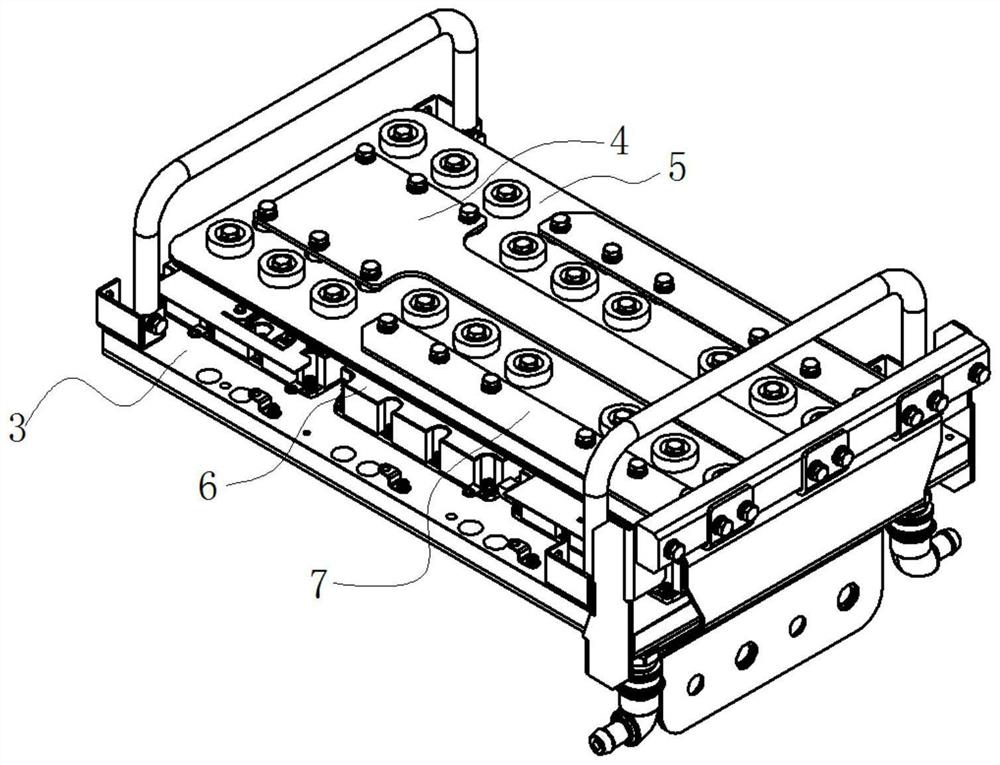

Heater and smoking set comprising same

ActiveCN112841741AImprove efficiencyShort current pathOhmic-resistance waterproof/air-tight sealsHeating element shapesElectrical resistance and conductanceEngineering

The invention relates to the field of smoking sets, and provides a heater and a smoking set comprising the same. The heater comprises: a base body; an infrared electric heating coating arranged on the surface of the base body; and a conductive module comprising a first conductive part and a second conductive part which are arranged on the surface of the base body, wherein the first conductive part and the second conductive part are at least partially electrically connected with the infrared electric heating coating. The first conductive part comprises a first conductive part spiral section, the second conductive part comprises a second conductive part spiral section, and the distance between the first conductive part spiral section and the second conductive part spiral section is not zero. Through the first conductive part spiral section and the second conductive part spiral section which are arranged on the surface of the base body, the path of current flowing through the infrared electric heating coating of the base body can be relatively short, the resistance value of equivalent resistance of the infrared electric heating coating is reduced, and the heater efficiency is improved.

Owner:SHENZHEN FIRST UNION TECH CO LTD

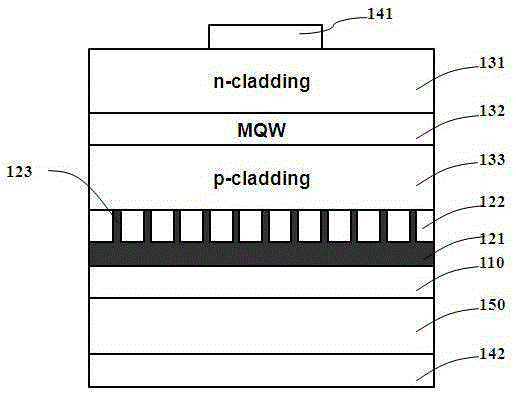

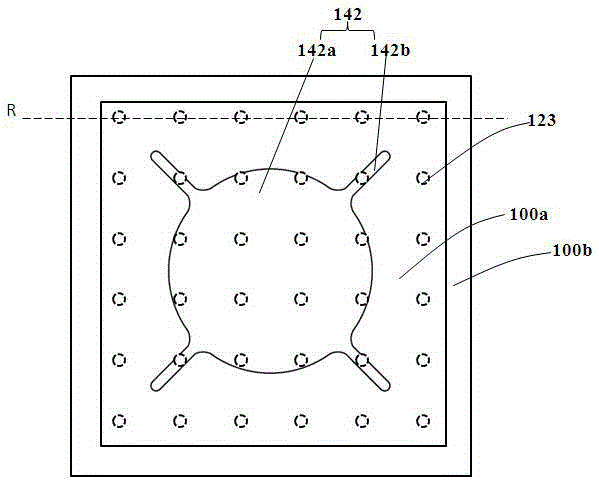

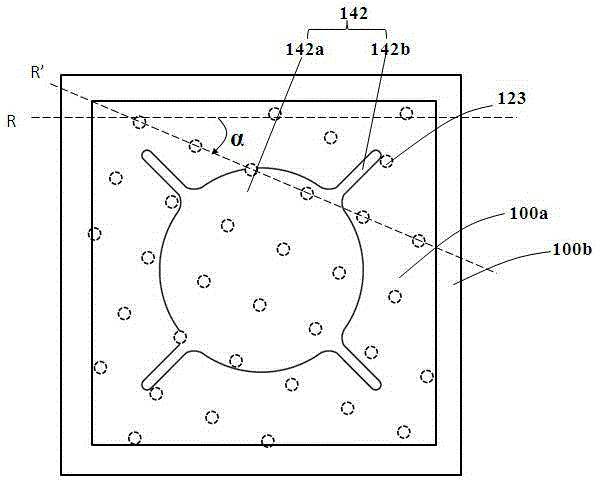

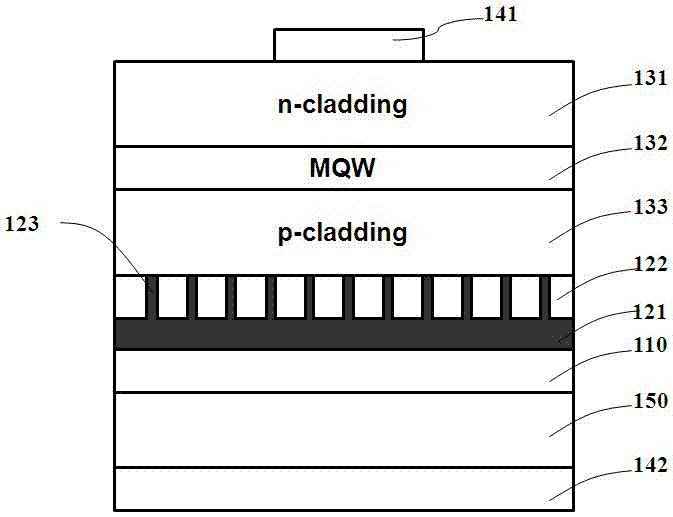

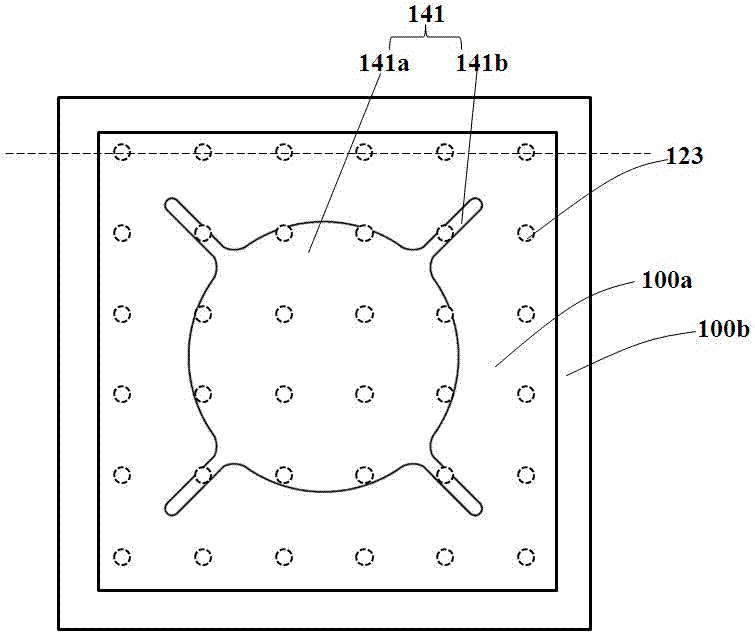

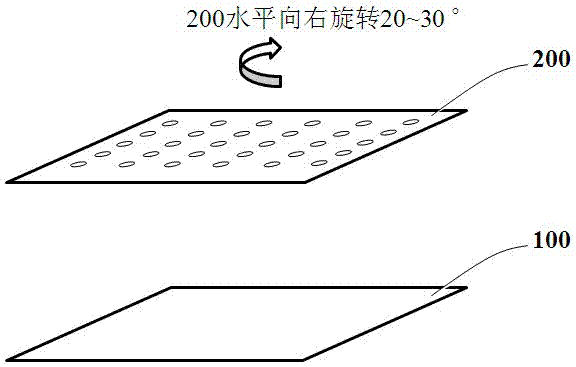

Light emitting diode chip and manufacturing method therefor

ActiveCN105322068AMake sure the area stays the sameShort current pathSemiconductor devicesElectrical conductorOhmic contact

The invention provides a light emitting diode chip. The light emitting diode chip comprises a light emitting epitaxial laminated layer, a dielectric layer, a metal conductive layer, a conductive substrate, and a first electrode, wherein the light emitting epitaxial laminated layer comprises a first type semiconductor layer, a second semiconductor layer and an active layer sandwiched between the first type semiconductor layer and the second semiconductor layer; the dielectric layer is positioned on the lower surface of the light emitting epitaxial laminated layer and provided with a conductive through hole array; the metal conductive layer is positioned on the lower surface of the dielectric layer; the conductive through hole is filled with the metal conductive layer; the metal conductive layer and the light emitting epitaxial laminated layer form ohmic contact; the conductive substrate is positioned on the lower surface of the metal conductive layer for supporting the light emitting epitaxial laminated layer; the first electrode is positioned on the upper surface of the light emitting epitaxial laminated layer; the first electrode comprises a bonding pad electrode and a finger-shaped electrode; a rotation angle is between the conductive through hole array and the finger-shaped electrode; and the selection of the rotation angle enables the conductive through holes with the preferable quantity to be not shielded by the bonding pad electrode and the finger-shaped electrode. The invention also provides a method for manufacturing the light emitting diode chip.

Owner:TIANJIN SANAN OPTOELECTRONICS

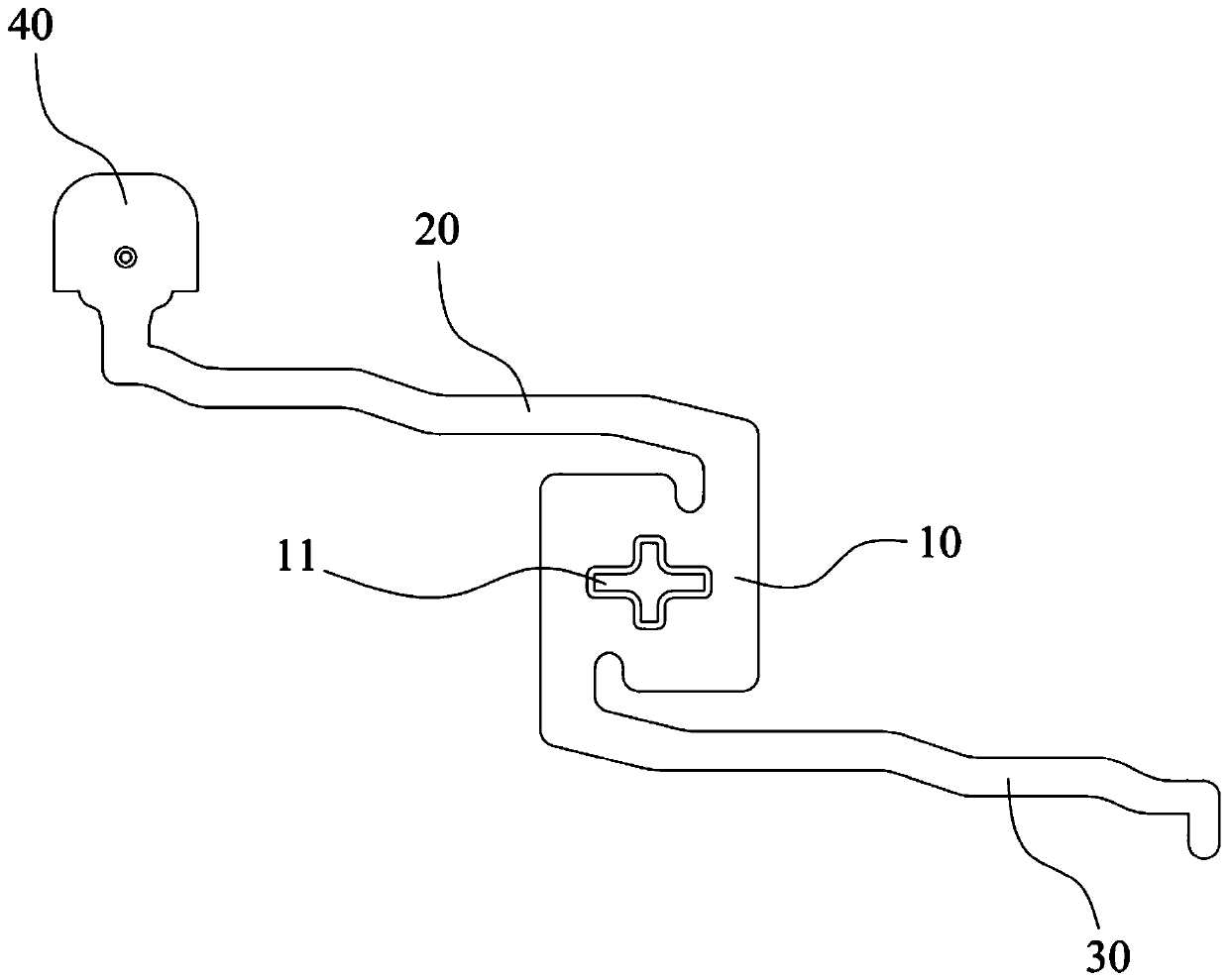

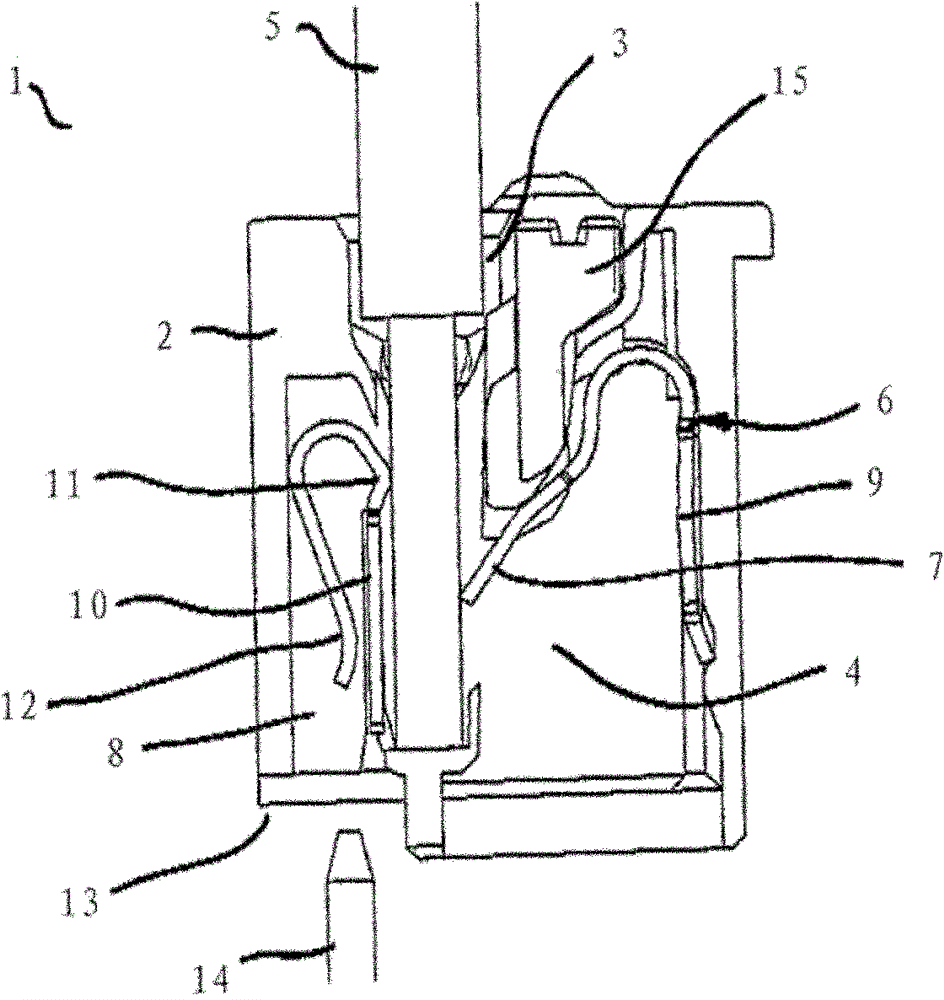

Plug-in type miniature circuit breaker housing installation structure

InactiveCN106340427AShort current pathSave installation spaceProtective switch terminals/connectionsLow voltageEconomic benefits

The invention provides a plug-in type miniature circuit breaker housing installation structure, which comprises a housing body (1) of a hexagonal cuboid structure, and is characterized in that the upper portion of the left side surface of the housing body (1) is provided with a button (2), the left side surface is provided with a left wiring terminal 1 (3) and a left wiring terminal 2 (4) below the button (2), guide limiting grooves (101) are formed in the upper portion and / or bottom portion of the front side surface and / or rear side surface of the housing body (1), a right wiring groove 1 (5), an information line wiring groove (6) and a right wiring groove 2 (7) are formed in the right side surface of the housing body (1) from bottom to top in sequence, and buckles (8) are arranged on the upper side surface and / or lower side surface of the housing body (1) on one side of the button (2). The plug-in type miniature circuit breaker housing installation structure adopts a plug-in type customized interface, so that a loop in which a circuit breaker is arranged has the shortest current path in a whole low-voltage power transmission and distribution conductive system, and the installation and wiring spaces are saved, thus the materials are saved, and good economic benefit is generated.

Owner:SHANGHAI LIANGXIN ELECTRICAL

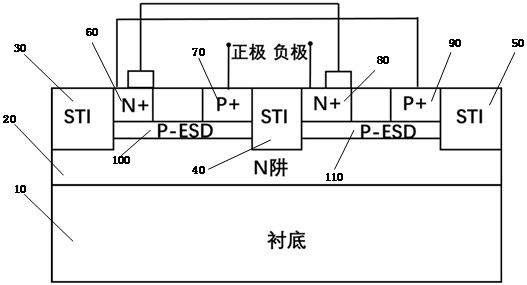

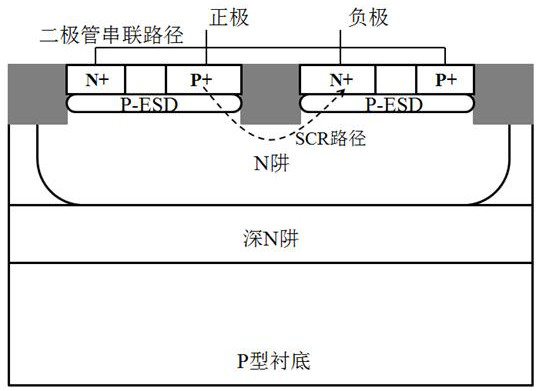

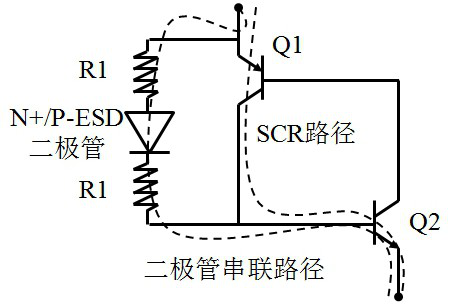

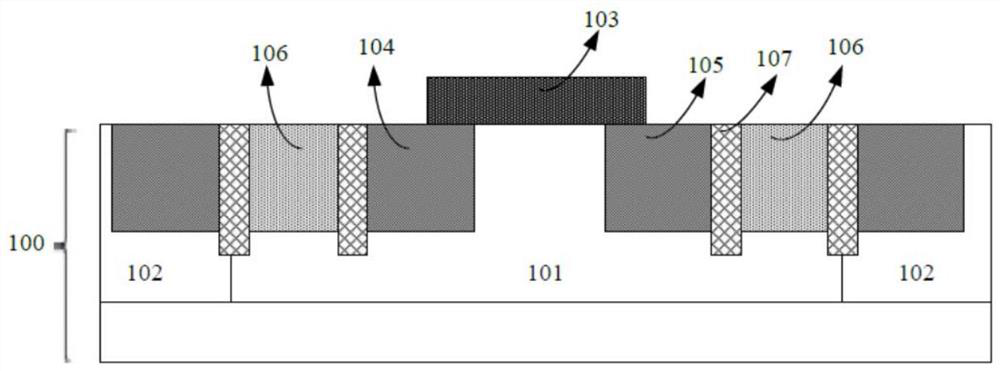

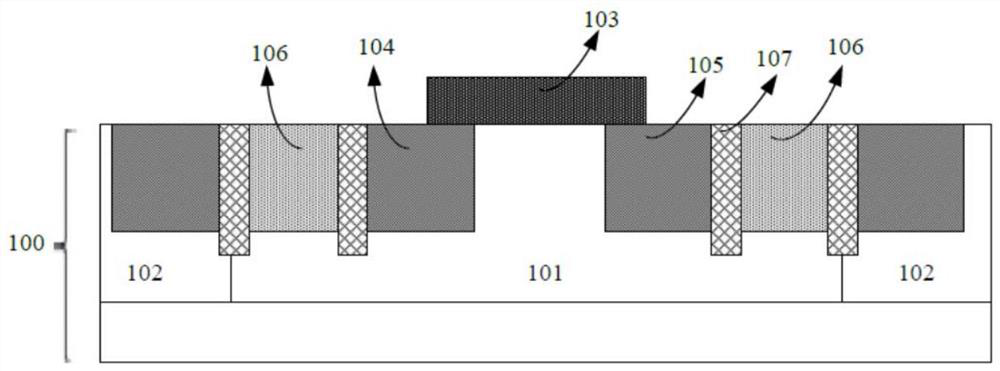

Silicon controlled rectifier electrostatic discharge protection structure

ActiveCN114783997AShort current pathLower on-resistanceTransistorSolid-state devicesPhysicsElectrostatic discharge protection

The invention discloses a silicon controlled rectifier electrostatic discharge protection structure which comprises a substrate, an N well, a first isolation groove, a second isolation groove, a third isolation groove, a first N + injection region, a first P + injection region, a second N + injection region, a second P + injection region, a first ESD injection layer and a second ESD injection layer. The N well is arranged in the surface area of the substrate; the N well is sequentially provided with a first isolation groove, a first ESD injection layer, a second isolation groove, a second ESD injection layer and a third isolation groove from one end to the other end; two sides of the first ESD injection layer are respectively connected with the first isolation groove and the second isolation groove, and two sides of the second ESD injection layer are respectively connected with the second isolation groove and the third isolation groove; a first N + injection region and a first P + injection region are arranged on the surface of the first ESD injection layer, and a second N + injection region and a second P + injection region are arranged on the surface of the second ESD injection layer. According to the embodiment of the invention, the electrostatic discharge protection effect can be effectively improved.

Owner:MICROTERA SEMICON (GUANGZHOU) CO LTD

Illuminating device

ActiveCN100499188CShort current pathAdd depthSolid-state devicesSemiconductor devicesLight emitting deviceSupply current

The invention is a light emitter to emit light after connected with power supply, at least comprising: luminous body having at least two electrodes to connect with power supply to make the luminous body offer a light source where the electrodes and the light outgoing surface of the luminous body are on the same side; bearing body with a groove to hold the luminous body, where the groove corresponds to the light outgoing surface and forms a diminishing shape close to the light outgoing and is equipped with connectors to connect with the light outgoing in the holding positions; and the invention has thin structure and makes the supply current path have advantages of low series thermal resistance and low cost, able to further increase light receiving efficiency by increasing groove depth.

Owner:IND TECH RES INST

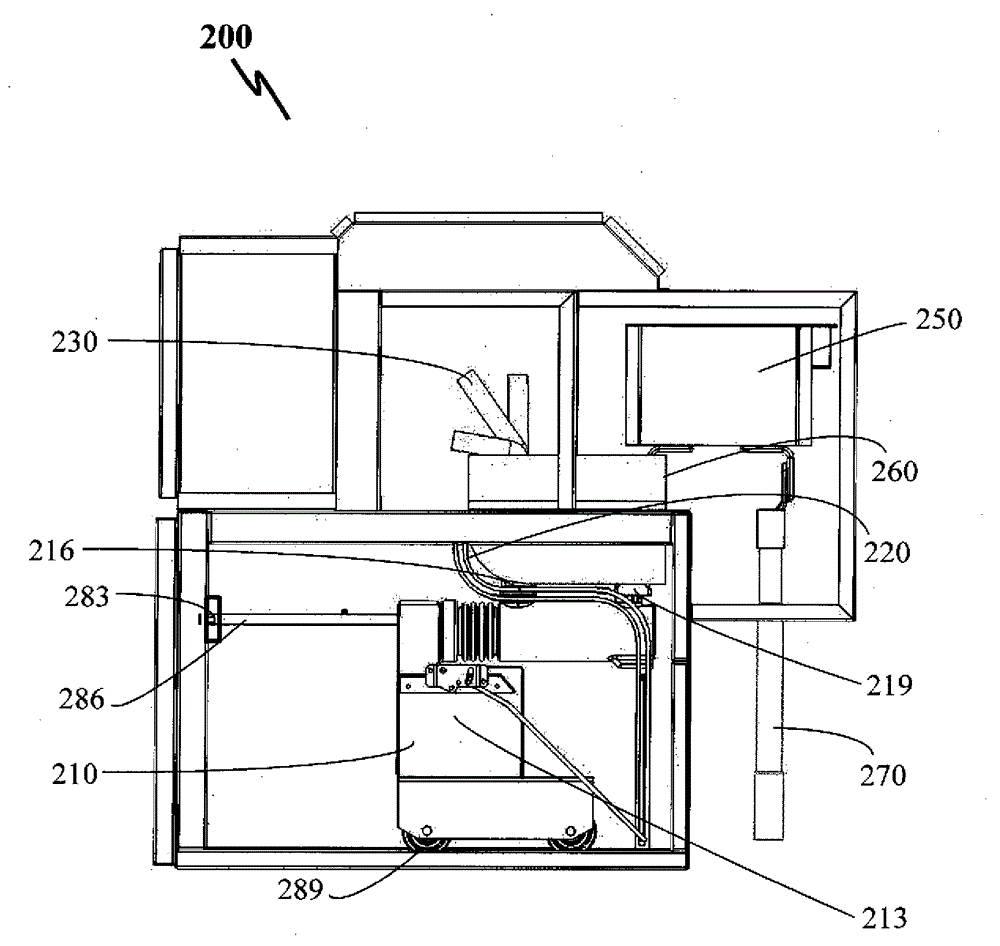

A compact switchgear and a shutter arrangement therefor

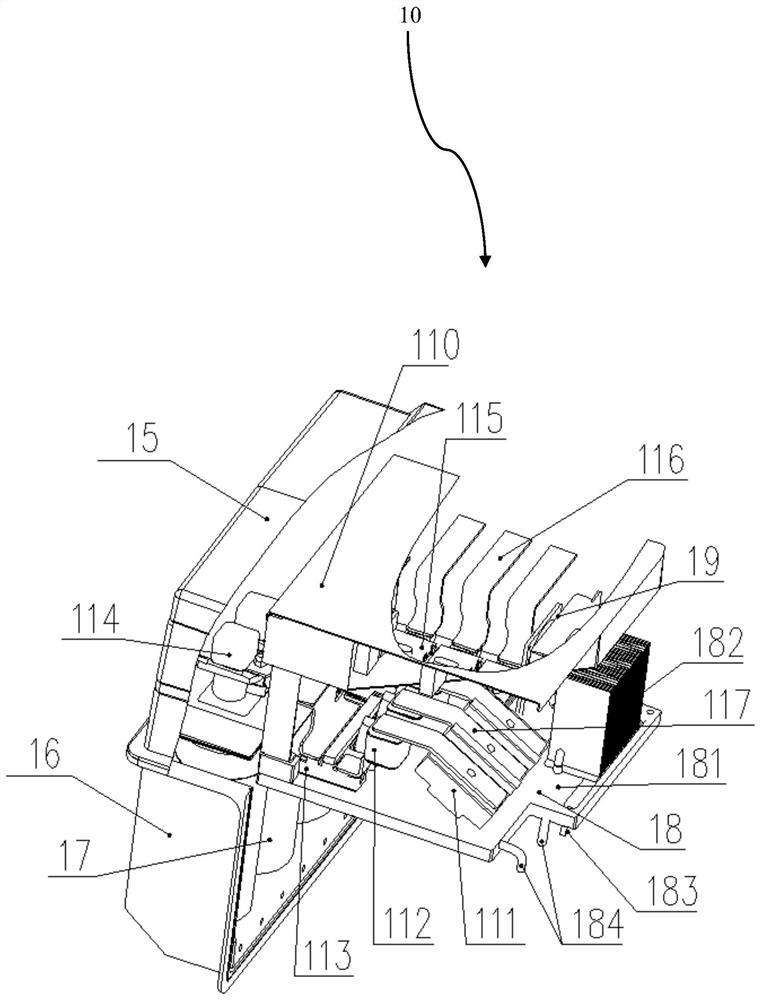

InactiveCN104685738ASimple structureCost effectiveSwitchgear with horizontal withdrawalSubstation/switching arrangement cooling/ventilationEngineeringSwitchgear

The invention relates to a compact switchgear having more simplified construction. The switchgear of the invention comprises a circuit breaker and a monoblock. The monoblock is electrically connectible to the circuit breaker of the switchgear. The invention also provides a shutter arrangement for the compact switchgear of the invention. The invention further relates to a method of operating the switchgear having the shutter arrangement, of the invention.

Owner:ABB 技术有限公司

Method for manufacturing a semiconductor device and semiconductor device

ActiveCN112447845BNot easy to concentrateShort current pathSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

The present invention provides a manufacturing method of a semiconductor device and the semiconductor device. The manufacturing method includes: providing a semiconductor substrate on which a gate structure is formed; performing a lightly doped source-drain ion implantation process to Forming lightly doped source and drain regions in the semiconductor substrate on both sides of the gate structure; performing pocket region ion implantation to form a pocket ion implantation region at the bottom of the lightly doped source and drain region; performing source and drain ion implantation implanted to form source and drain regions in the semiconductor substrate on both sides of the gate, wherein the lightly doped source and drain regions, the pocket ion implantation region and the source and drain regions are jointly formed in the There are source and drain electrodes with inclined topography under the gate structure. According to the manufacturing method of the semiconductor device and the same area of the semiconductor device, it can have a higher current capability (current capability of the transmission line pulse test), so it has higher robustness than conventional technology.

Owner:CSMC TECH FAB2 CO LTD

Semiconductor device and process for fabricating the same

ActiveCN1875481BAchieve thinningExcellent electrical propertiesSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A thin stacked semiconductor device suitable for high speed operation. A plurality of specified circuits are formed on one surface of a semiconductor substrate while being arranged, and wiring and insulating layers being connected electrically with the circuits are laminated and formed sequentially in a specified pattern to form a multilayer wiring part. At the stage for forming the multilayer wiring part, a filling electrode is formed on the semiconductor substrate such that the surface is covered with an insulating film, a post electrode is formed on specified wiring at the multilayer wiringpart, a first insulating layer is formed on one surface of the semiconductor substrate, the surface of the first insulating layer is removed by a specified thickness to expose the post electrode, theother surface of the semiconductor substrate is ground to expose the filling electrode and to form a through-type electrode, forward end of the through-type electrode is projected by etching one surface of the semiconductor substrate, a second insulating layer is formed on one surface of the semiconductor substrate while exposing the forward end of the through-type electrode, bump electrodes areformed on both electrodes and then the semiconductor substrate is divided to form a semiconductor device. A plurality of semiconductor devices thus obtained are stacked and secured at the bump electrodesthus manufacturing a stacked semiconductor device.

Owner:TAIWAN SEMICON MFG CO LTD

A type bus bar stacking method for large power pulse switch power supply

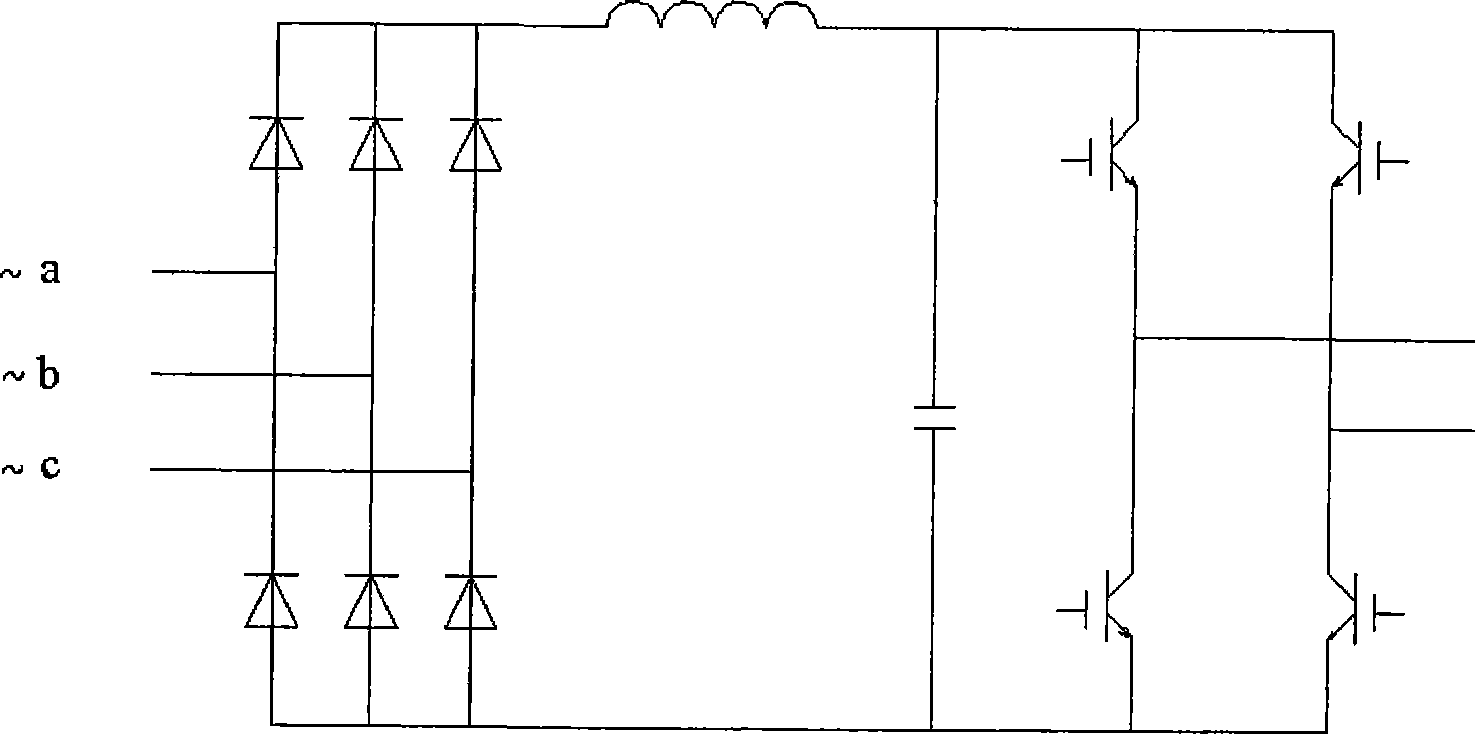

InactiveCN101478224BReduce electromagnetic radiationShorten connection lengthPower conversion systemsBusbarPower switching

The invention discloses a method for laminating A-type busbars of a high-power pulse switch power supply. The method is structurally characterized in that four rectifier bridge modules are selected to be connected in parallel and rectified, and two IGBT (insulated gate bipolar translator) modules are selected to output a main circuit; a filter capacitor, a power switching tube or a rectifier, andan inductor or a transformer in the main circuit are placed close to each other; the directions of the components are determined, that is, in design of the high power pulse switch power supply, a capacitor plate, A, B, C, anode phase input copperplate are installed by copperplate lamination, therefore, the wiring is reduced, the influence of the lead inductance and resistance is eliminated, electromagnetic interference is further reduced and the purpose to inhibit electromagnetic interference is achieved.

Owner:INST OF MODERN PHYSICS CHINESE ACADEMY OF SCI

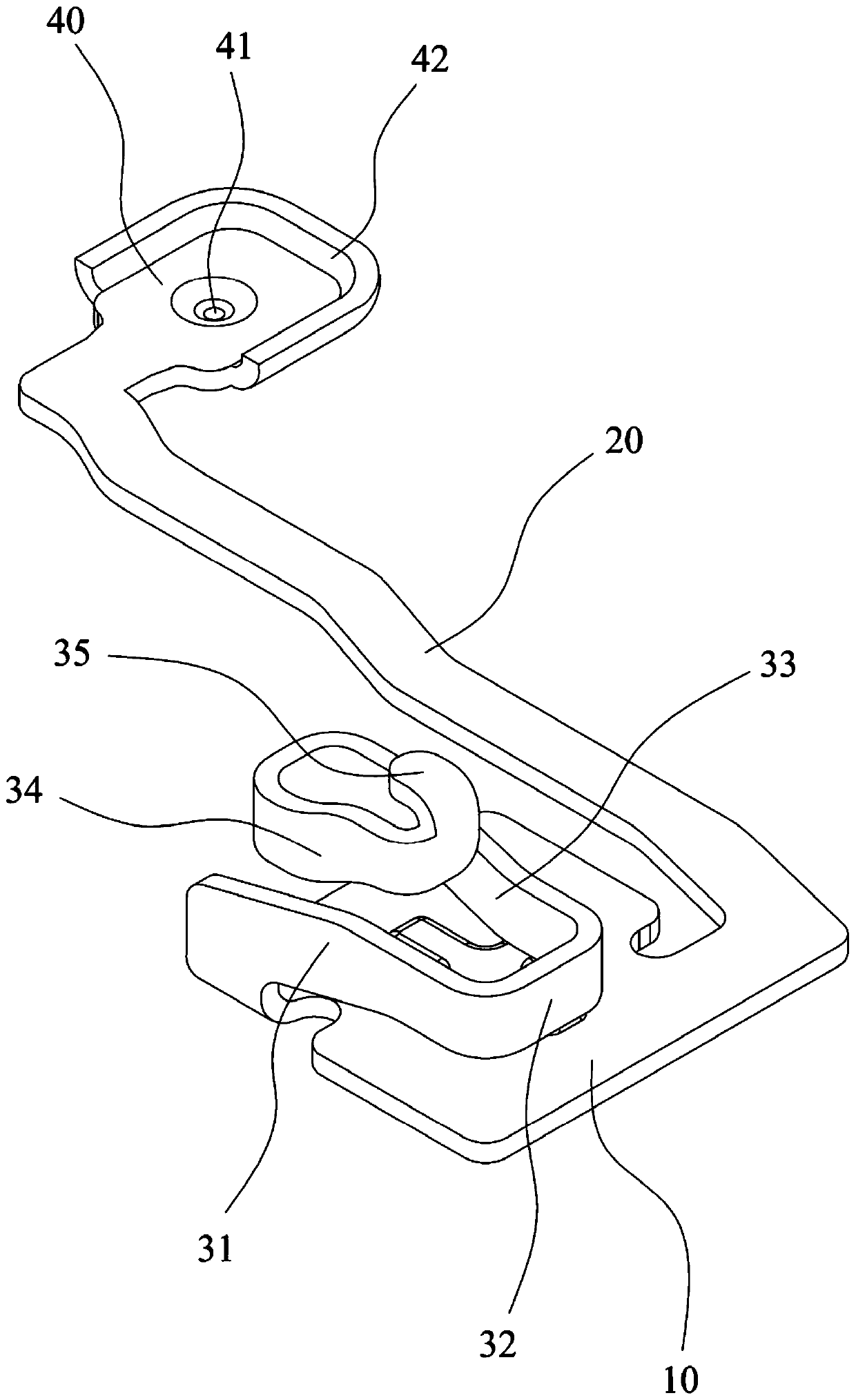

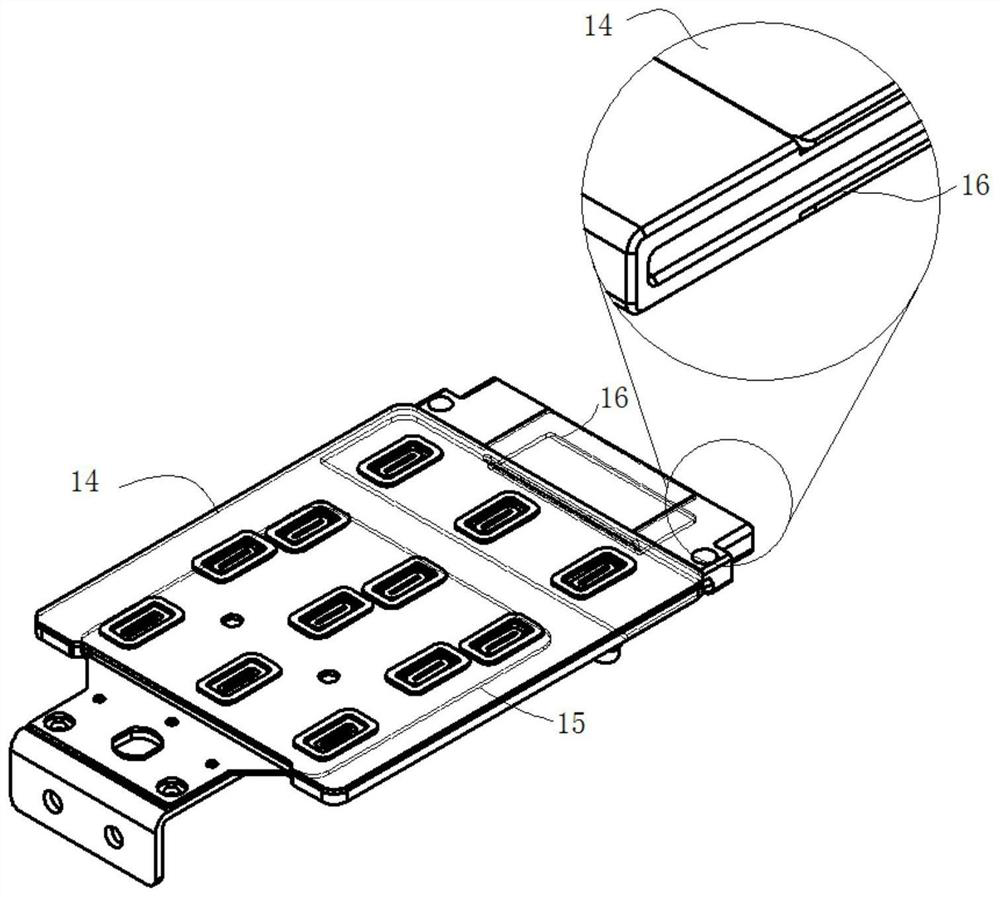

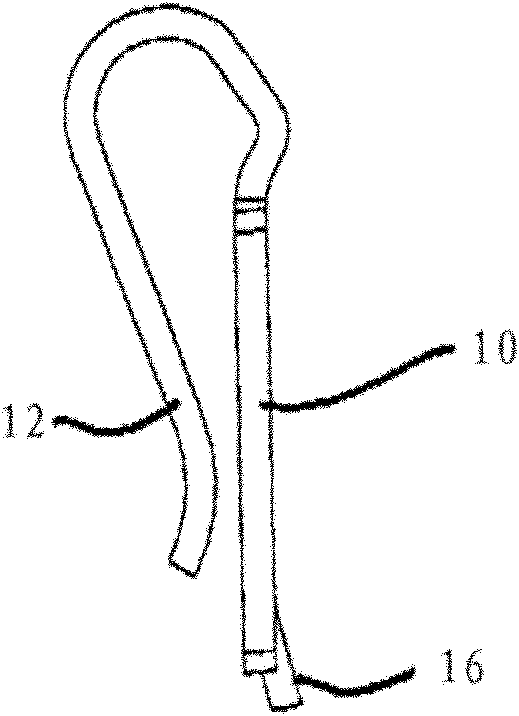

Electrical connection elastic sheet, connector and electronic equipment

PendingCN110534941AReduce volumeSmall footprintCoupling contact membersElectrical connectionEngineering

The invention discloses an electrical connection elastic sheet, a connector and electronic equipment. The electrical connection elastic sheet comprises a flat-plate-shaped welding part. A first elastic part and a second elastic part respectively extend upwards from two opposite sides of the welding part along the height direction of the welding part; the first elastic part and the second elastic part are formed by bending for multiple times; one end, far away from the welding part, of the first elastic part extends to form a contact part; the contact part is parallel to the welding part; one end, far away from the welding part, of the second elastic part is propped against a bottom surface of the contact part; the first elastic part and the second elastic part are arranged on the welding part so as to support the contact part, projections of the first elastic part and the second elastic part on the plane where the welding part is located fall on the welding part, the first elastic partand the second elastic part are both in a double-U-shaped runway shape, and the contact part moves back and forth in the height direction of the welding part when being pressed. The electrical connection elastic sheet is advantaged in that the occupied area can be reduced, and the contact stability is improved.

Owner:SHENZHEN KRCONN IND TECH

Manufacturing method of semiconductor device and semiconductor device

ActiveCN112447845ANot easy to concentrateShort current pathSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

The invention provides a semiconductor device manufacturing method and a semiconductor device, and the method comprises the steps: providing a semiconductor substrate, and forming a gate structure onthe semiconductor substrate; executing a lightly doped source-drain ion implantation process to form lightly doped source-drain regions in the semiconductor substrate on two sides of the gate structure; executing bag region ion implantation to form a bag type ion implantation region at the bottom of the lightly doped source-drain region; and executing source-drain ion implantation to form a source-drain region in the semiconductor substrate on two sides of the gate, the lightly doped source-drain region, the bag type ion implantation region and the source-drain region jointly forming a source-drain electrode with an inclined morphology below the gate structure. According to the manufacturing method of the semiconductor device, under the condition that the area of the semiconductor device is the same as that of the semiconductor device, higher current capacity (the current capacity of transmission line pulse testing) can be achieved, and therefore higher robustness is achieved comparedwith a conventional process.

Owner:CSMC TECH FAB2 CO LTD

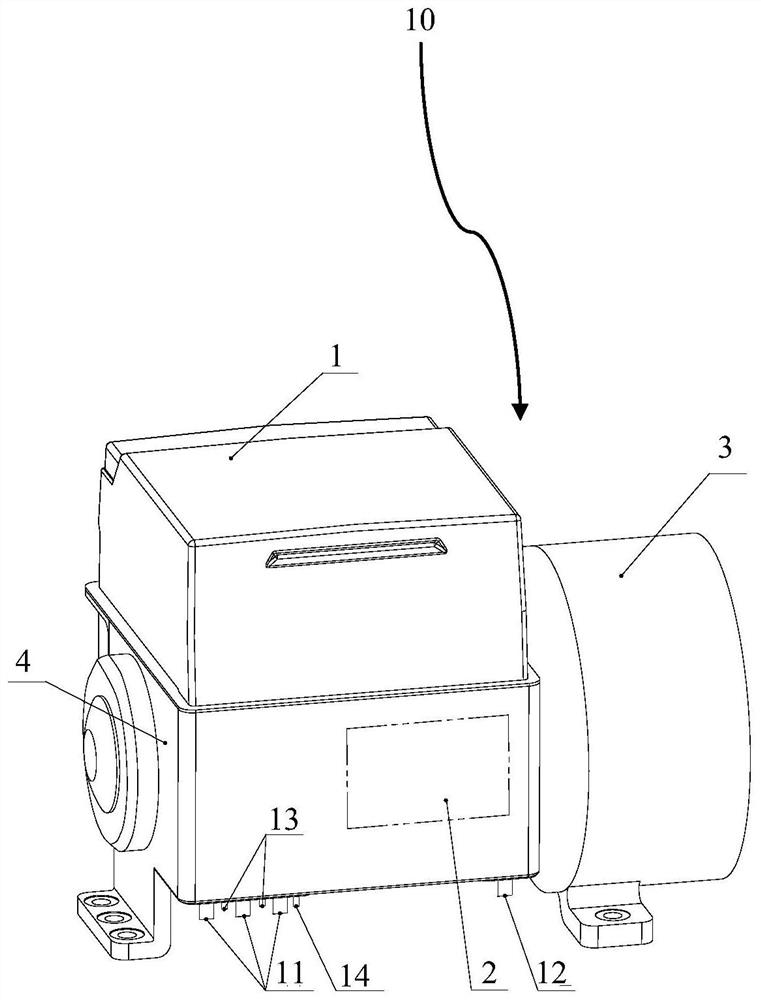

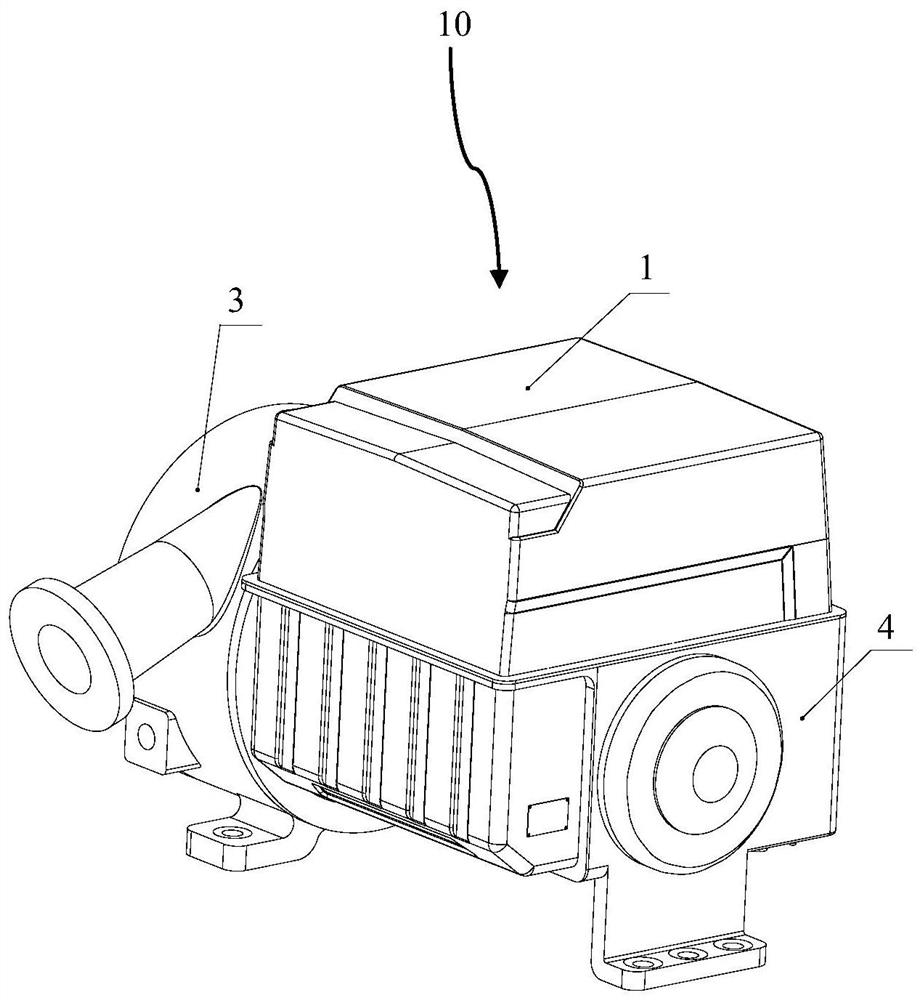

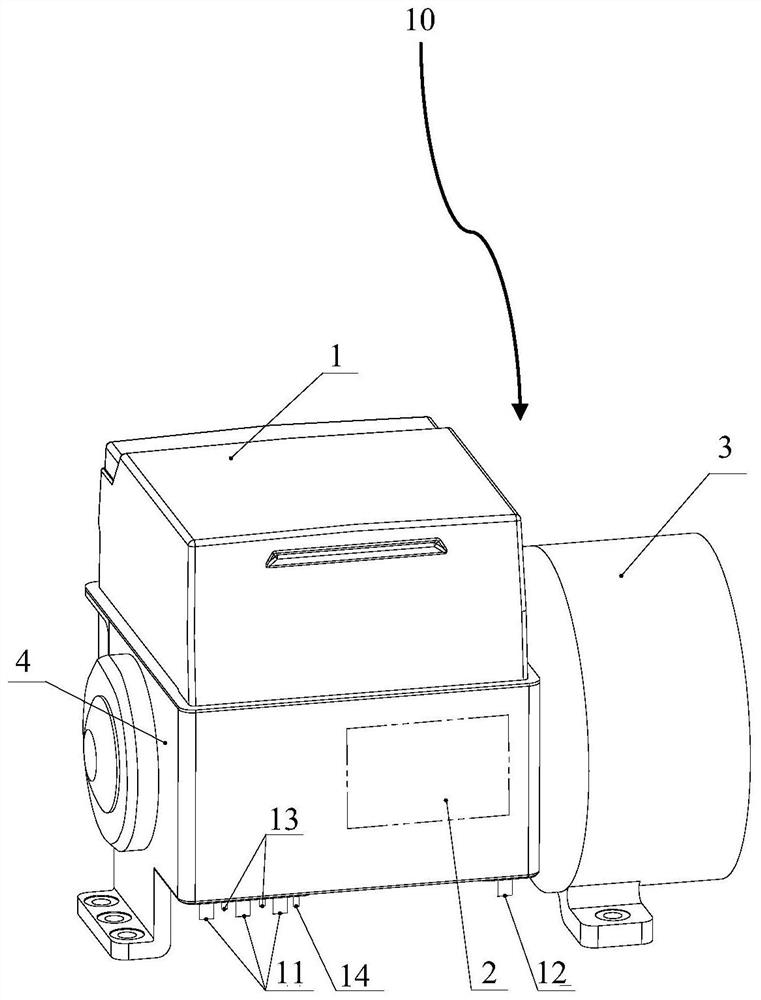

a converter

ActiveCN112448595BCompact structureEasy wiringConversion constructional detailsModifications for power electronicsElectric machineControl theory

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

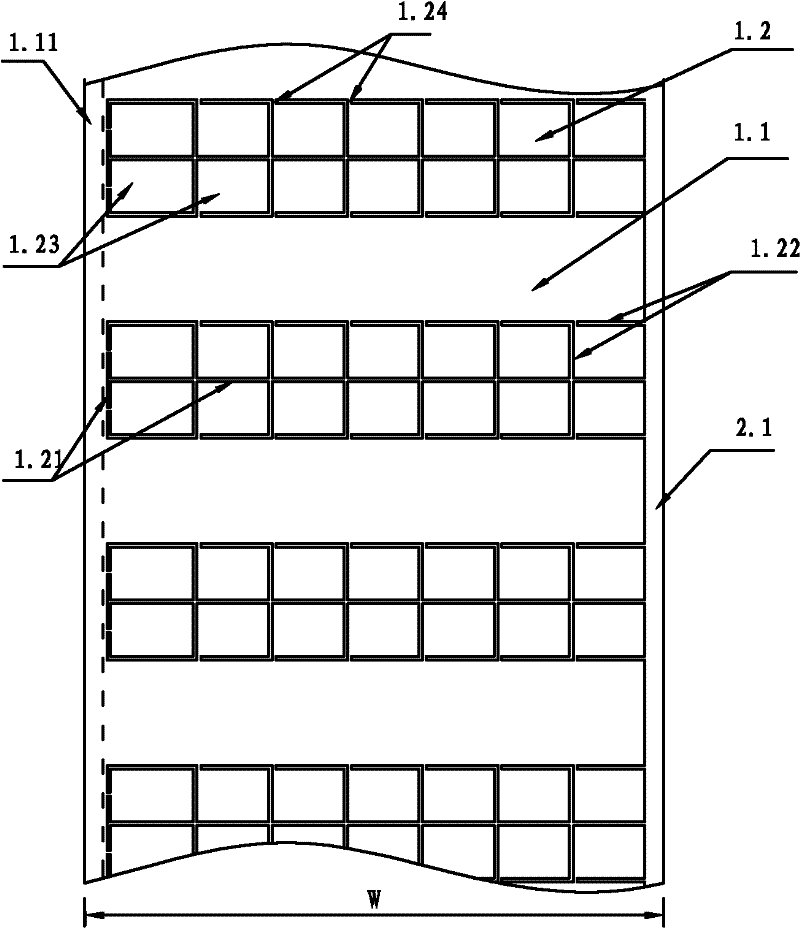

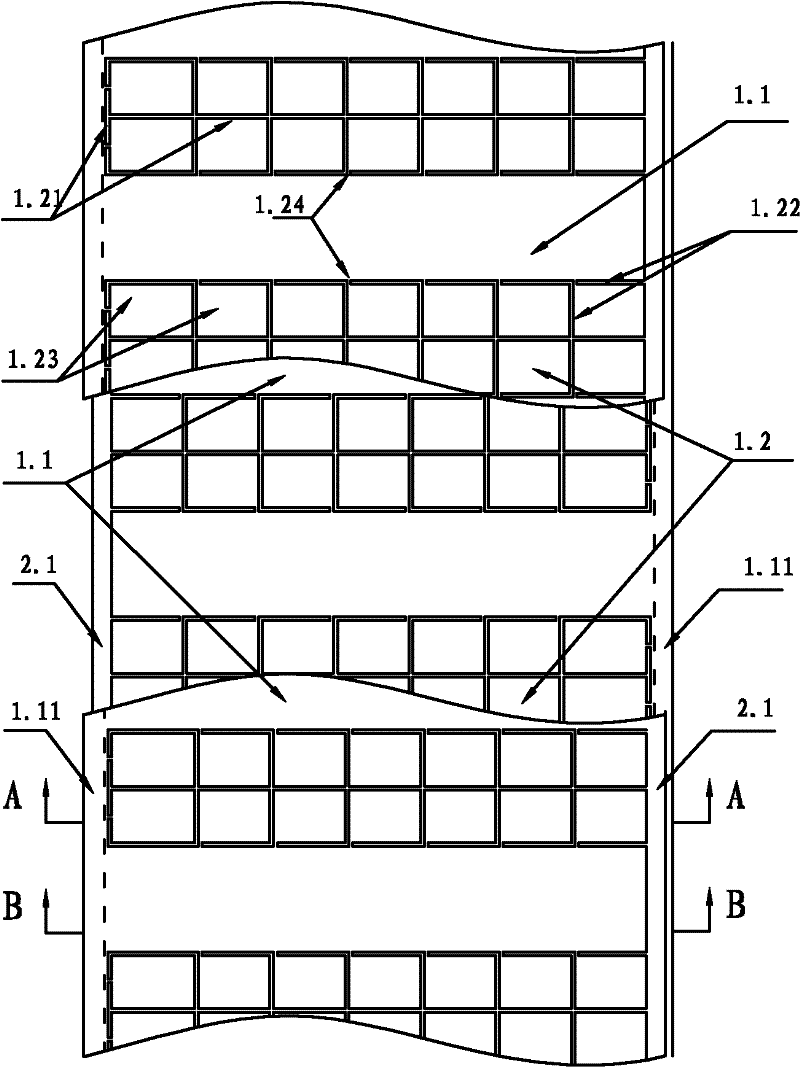

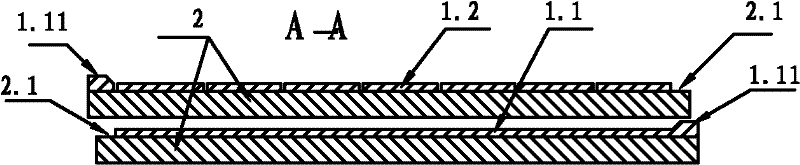

Vertically-partitioned metallized grid safe film electrode structure

The invention relates to a vertically-partitioned metallized grid safe film electrode structure, which comprises an upper layer metallized safe film and a lower layer metallized safe film. One side of each layer of the metallized safe films is a clad layer-free residual side, and the other side of each layer of the metallized safe films is a clad layer-thickened side; continuous clad layer zones and grid pattern zones which have roughly equal width are vertically distributed on a clad layer between the residual side and thickened side at intervals and alternately; small electrodes in the gridpattern zones do not interconnect directly; when two layers of the metallized safe films are overlaid for wrapping a capacitor, the residual sides and the clad layer-thickened sides of the upper and lower layers correspond to each other alternately; and the continuous clad layer zones and the grid pattern zones of the upper and lower layers correspond to each other alternately at the same time. The vertically-partitioned metallized grid safe film electrode structure has small overall heat productivity, is suitable for manufacturing alternating-current capacitors and high-frequency capacitors,increases safe reliability and service life, reduces the loss rate of the effective area of the film due to the gap stripes of an pattern, and reduces the manufacturing cost of a safe film capacitor.

Owner:浙江南洋华诚科技有限公司

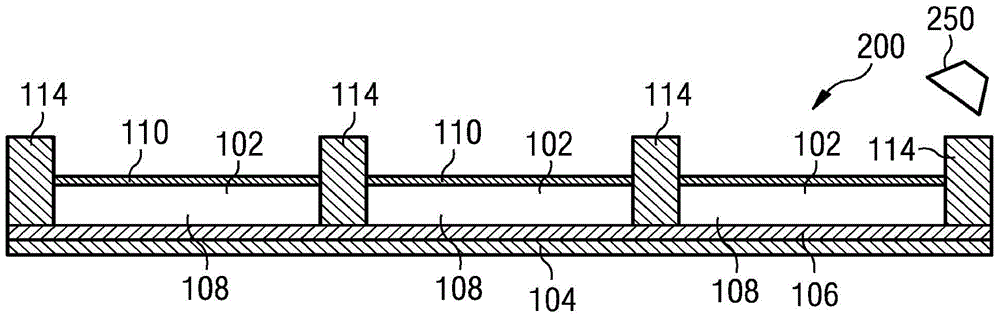

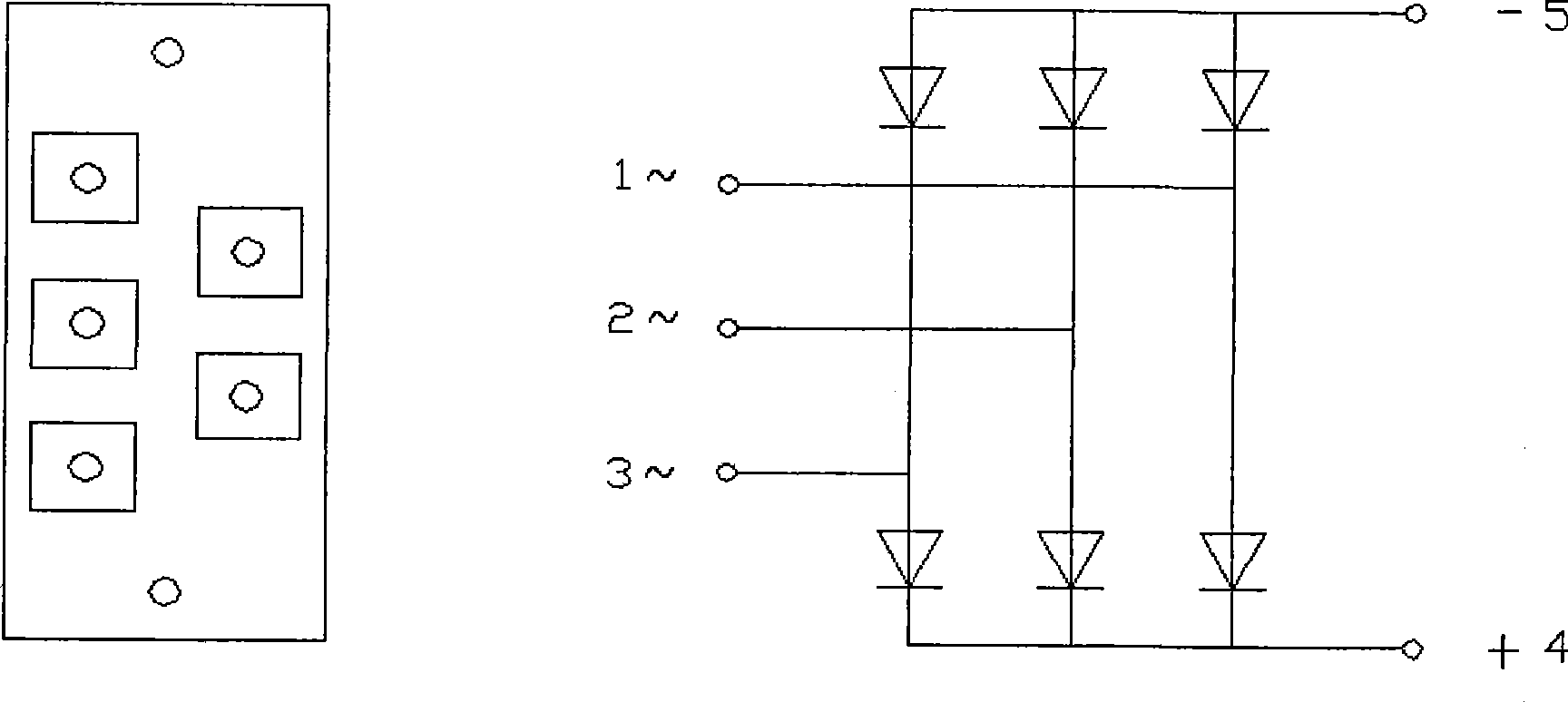

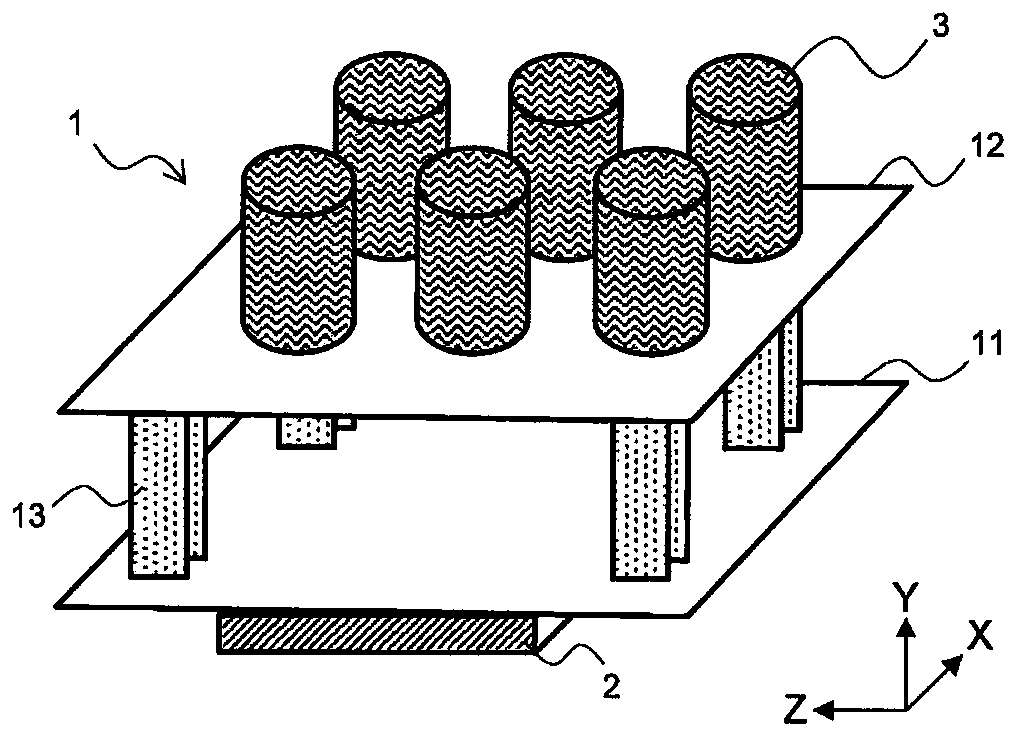

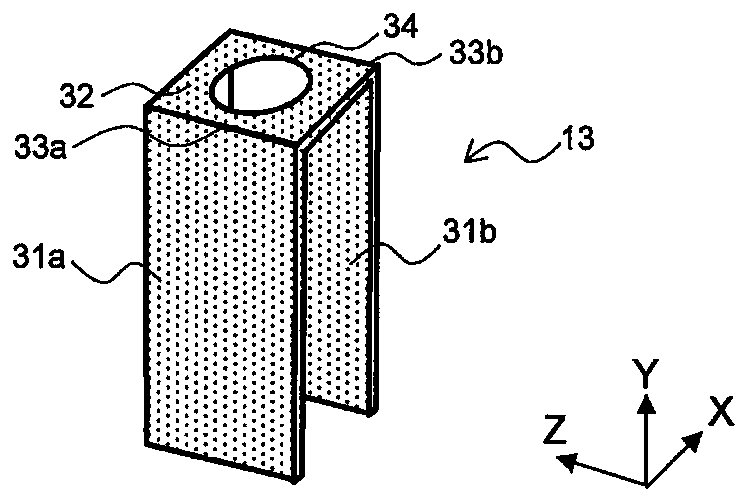

Power conversion device and air conditioning device using same

ActiveCN110063010AShort current pathLower impedanceCompressorAC motor controlComputer moduleEngineering

Provided is a power conversion device that includes the following: a first substrate on which a module that includes a switching element is mounted; a second substrate on which a smoothing capacitor is mounted; and a terminal block that connects the first substrate and the second substrate which are disposed so as to face each other, and that is provided with a current pathway through which flowsat least the current that flows from the module to the smoothing capacitor or the current that flows from the smoothing capacitor to the module.

Owner:MITSUBISHI ELECTRIC CORP

Current transformer

ActiveCN112448595AReduce volumeCompact structureConversion constructional detailsModifications for power electronicsElectric machineControl theory

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

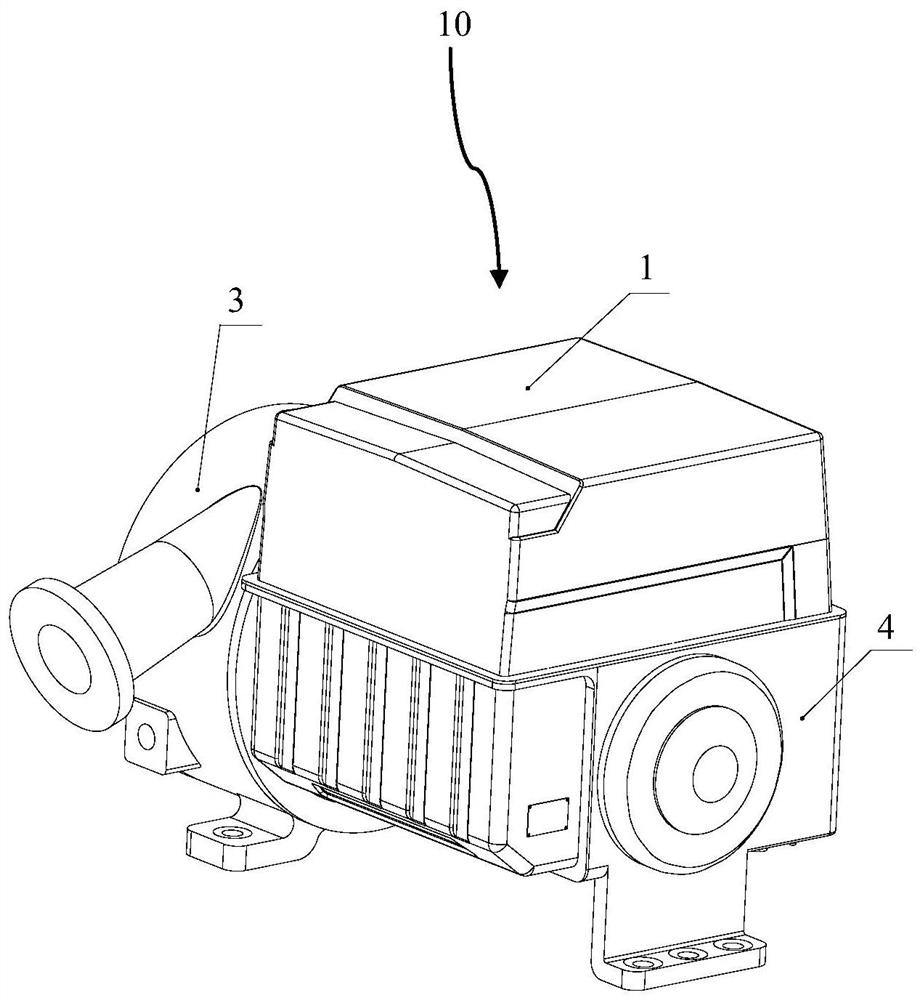

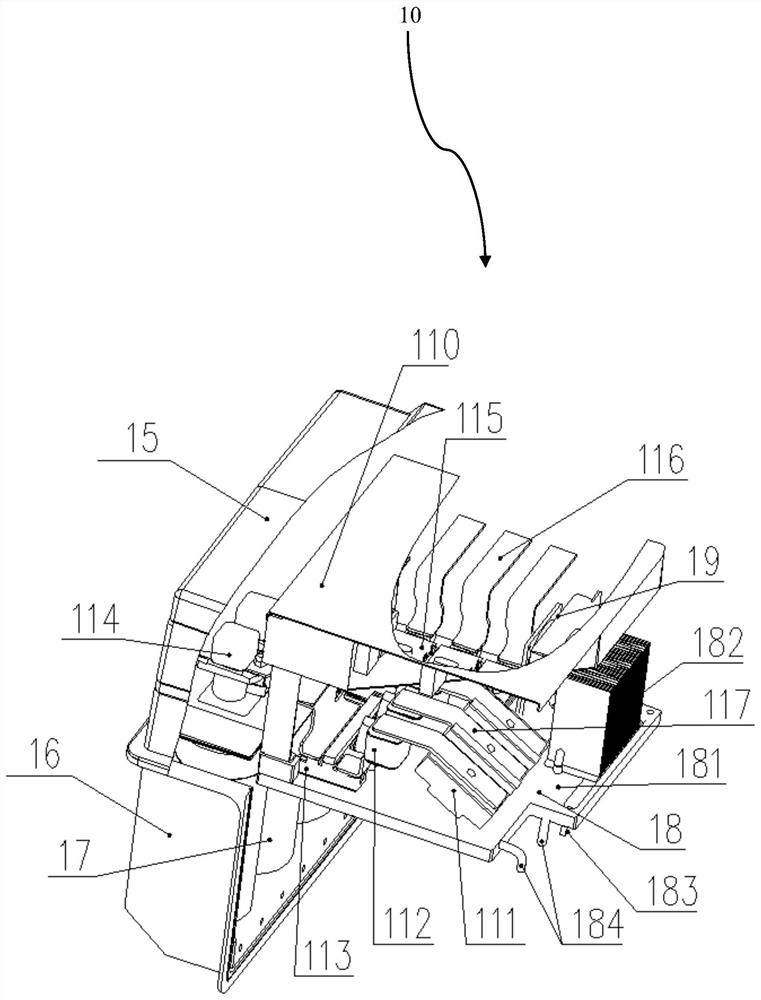

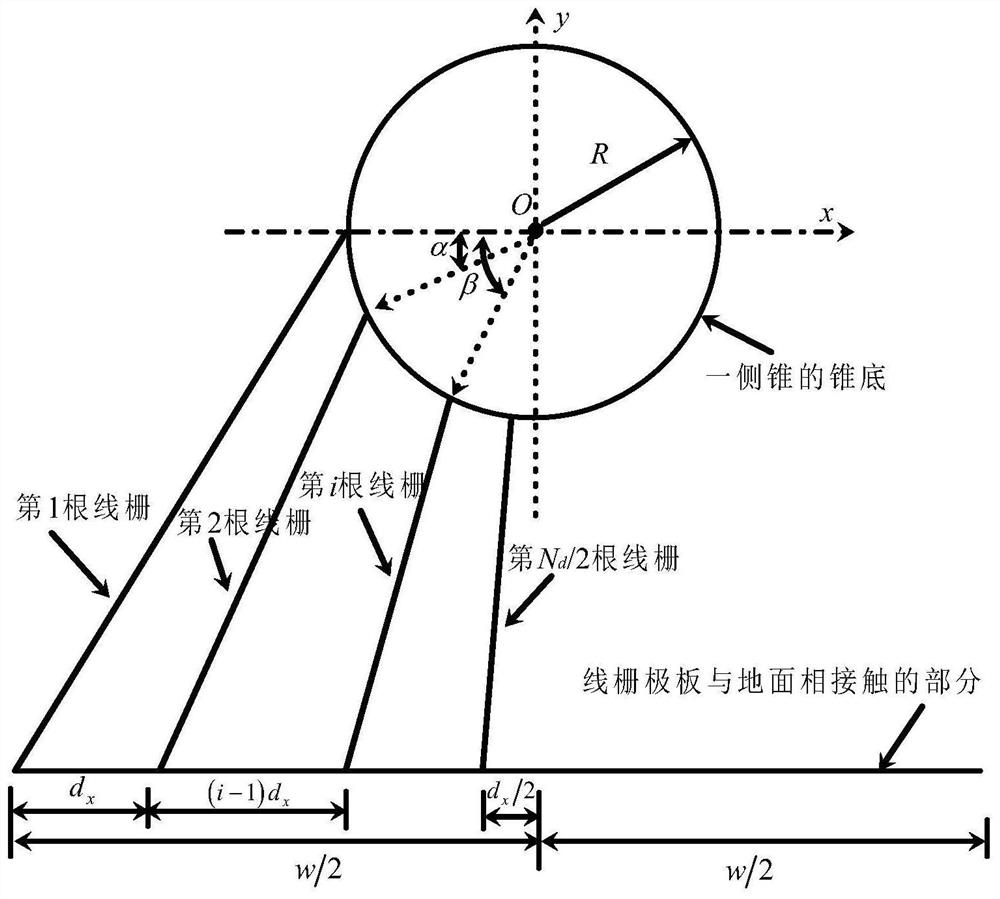

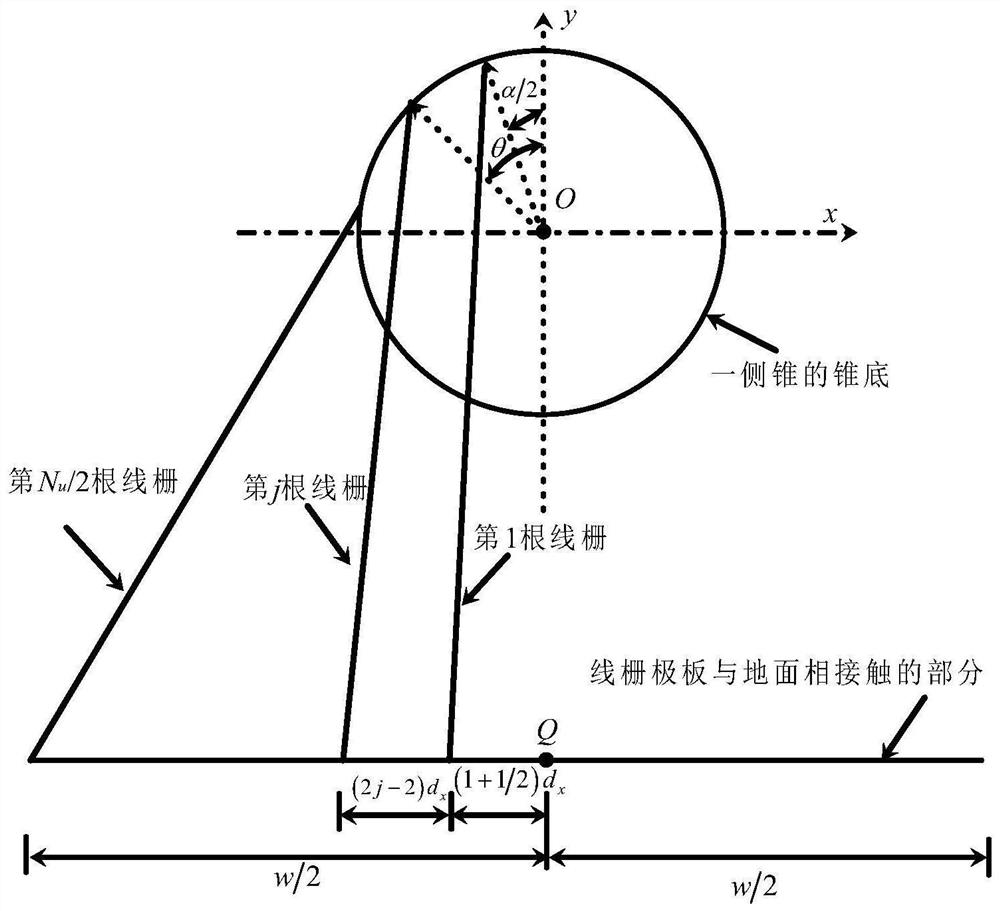

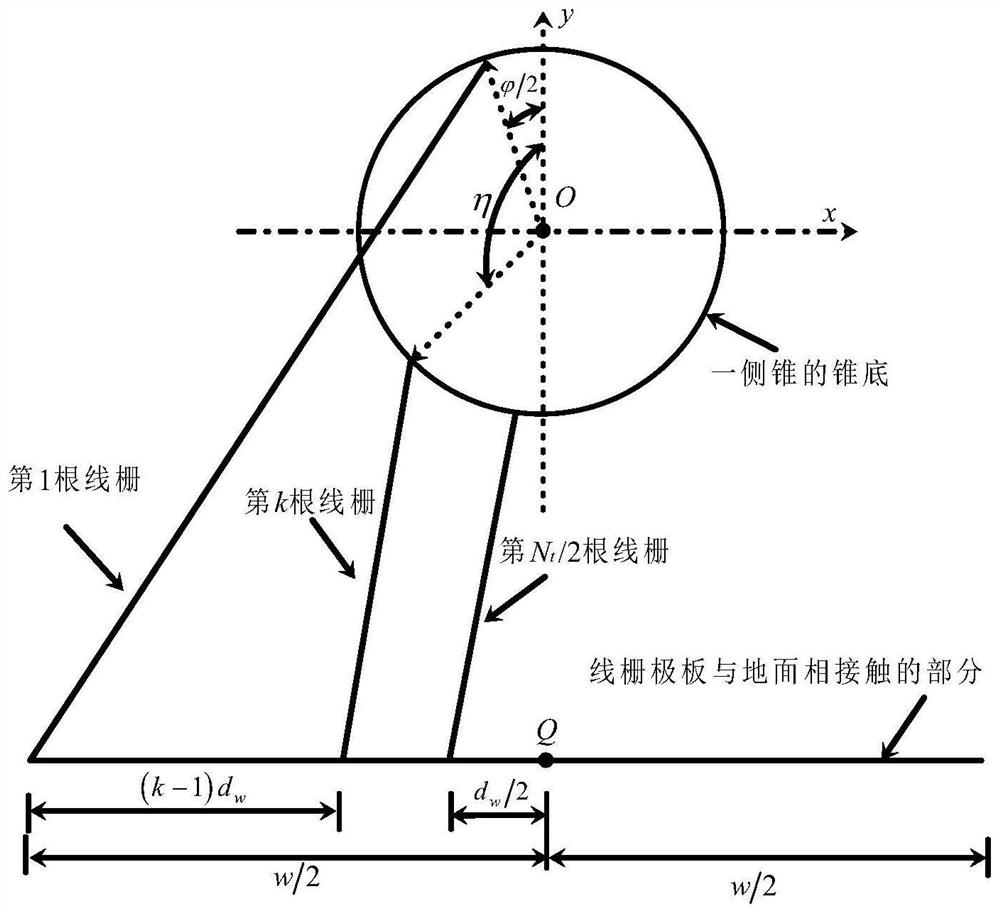

A horizontally polarized bounded wave electromagnetic pulse simulator, a wire grid plate and a wire grid arrangement method

ActiveCN111337769BReduce usageShorten the lengthElectromagentic field characteristicsMeasuring interference from external sourcesWire gridSimulation

Owner:NORTHWEST INST OF NUCLEAR TECH

Light-emitting diode chip and manufacturing method thereof

ActiveCN105322068BMake sure the area stays the sameShort current pathSemiconductor devicesOhmic contactEngineering

The present invention provides a light emitting diode chip, which comprises: a first type semiconductor layer, a second semiconductor layer and an active layer sandwiched between them; a dielectric layer located on the lower surface of the light emitting epitaxial stack, It has an array of conductive vias; a metal conductive layer is located on the lower surface of the dielectric layer, fills the conductive vias, and forms an ohmic contact with the light-emitting epitaxial stack; a conductive substrate is located on the metal conductive layer The lower surface is used to support the light-emitting epitaxial stack; the first electrode is located on the upper surface of the light-emitting epitaxial stack, including pad electrodes and finger electrodes; between the conductive via array and the finger electrodes There is a rotation angle between them, the rotation angle is selected such that a preferred number of conductive vias are not blocked by the pad electrodes and finger electrodes. The invention also provides a method for manufacturing the foregoing light-emitting diode chip.

Owner:TIANJIN SANAN OPTOELECTRONICS

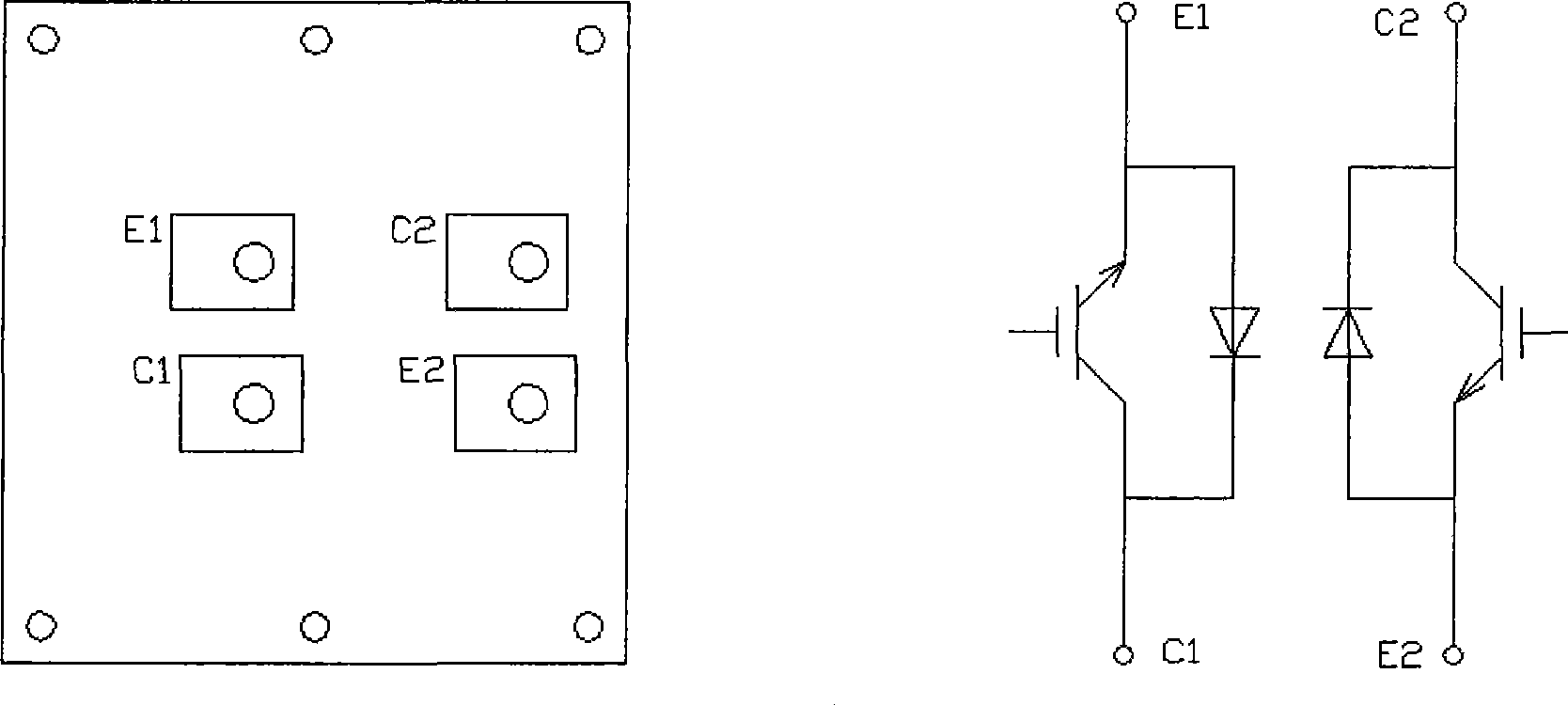

Integrated radiator IGBT power device with low-inductance composite busbar structure

PendingCN112687644AReduce thermal contact resistanceLower resistanceElectrically conductive connectionsSemiconductor/solid-state device detailsElectrical resistance and conductanceBusbar

The invention provides an integrated radiator IGBT power device with a low-inductance composite busbar structure, which comprises a radiator, a lining plate, a PCB circuit, a terminal and a low-inductance composite busbar, the lining plate is interconnected with the radiator, the PCB circuit and the terminal are arranged on the lining plate, and the low-inductance composite busbar is connected with the terminal; the low-inductance composite busbar comprises a DC + stage of a half-bridge IGBT device, a DC - stage of the half-bridge IGBT device and an AC stage of the half-bridge IGBT device, wherein the DC + stage of the half-bridge IGBT device and the DC - stage of the half-bridge IGBT device are oppositely arranged, and the AC stage of the half-bridge IGBT device is arranged on one side of the DC + stage of the half-bridge IGBT device and the DC - stage. According to the invention, the low-inductance composite busbar is integrated, so that the IGBT device is more compact, the occupied space is small, and the contact thermal resistance and resistance of the device caused by connection can be effectively reduced; the design freedom degree of the low-inductance composite busbar is high, and parasitic parameters are small; a power assembly formed by assembling the device is large in spatial arrangement freedom degree, and parasitic parameters can also be reduced. The stray inductance is low, the current path is short, the stress borne by the chip can be effectively reduced, and the reliability of the device can be improved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

plug connector

ActiveCN102195175BShort current pathReduce contact resistanceCoupling contact membersClamped/spring connectionsElectrical conductorSpring force

The invention relates to a plug-in connector (1), wherein at least a part of a busbar element (10) is arranged in such a way on the boundary between an associated conductor socket (3) and an associated contact pin receiving opening (8) In the region, so that this part of the contact rail element (10) is located between the contact pin (14) and the electrical conductor (5) and is in contact with the contact pin (14) and the electrical conductor (5) in a conductive manner superior. The busbar element (10) has an elastic contact area in the contact pin receptacle (8) for connecting the busbar element (10) with a contact pin (14) which can be introduced into the associated contact pin receptacle (8) by spring force ) in conductive contact.

Owner:WAGO VERW GMBH

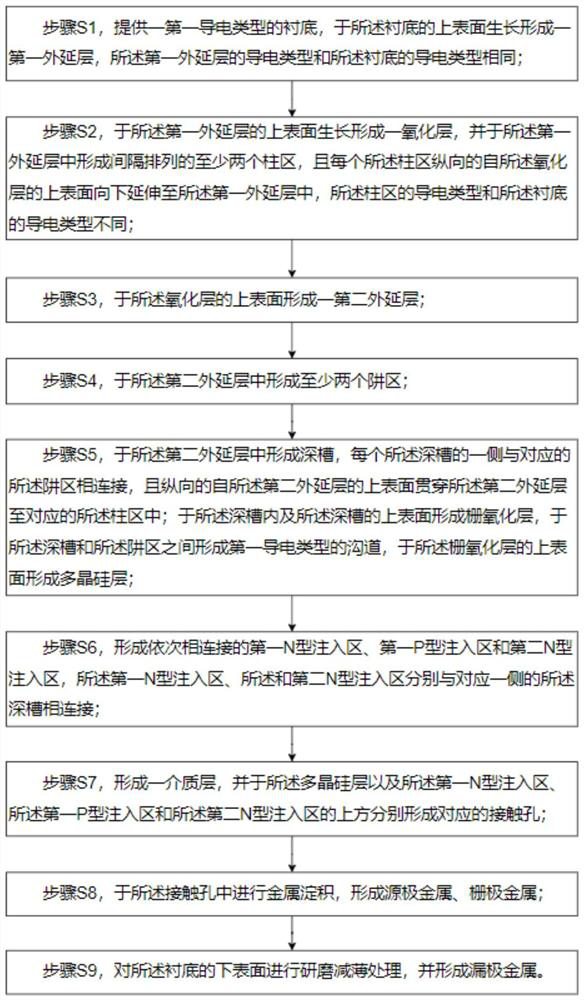

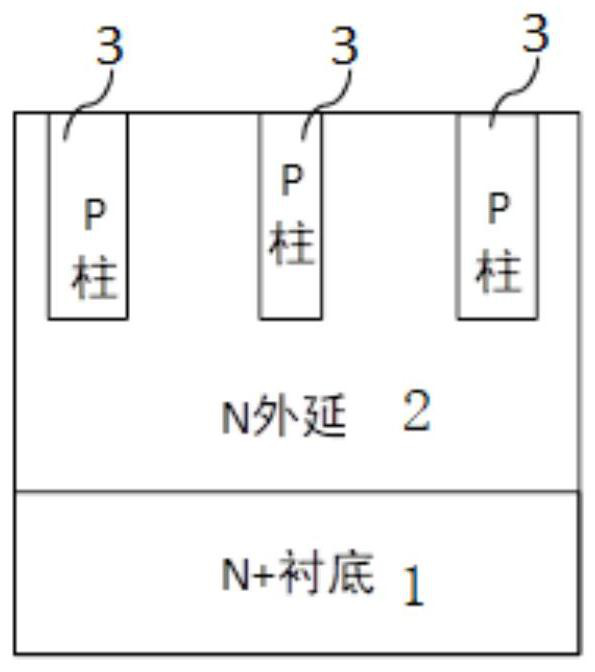

Depletion mode field effect transistor device and preparation method thereof

PendingCN113140463AShort current pathLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesField effectField-effect transistor

The invention discloses a preparation method of a depletion mode field effect transistor device, which belongs to the field of semiconductor protection devices, and comprises the following steps: S1, forming a first epitaxial layer on a substrate; S2, growing an oxide layer, and forming at least two column regions in the first epitaxial layer; S3, forming a second epitaxial layer; S4, forming at least two well regions; S5, forming a deep groove, forming a gate oxide layer in the deep groove and on the upper surface of the deep groove, forming a channel between the deep groove and the well region, and forming a polycrystalline silicon layer on the upper surface of the gate oxide layer; S6, forming a first N-type injection region, a first P-type injection region and a second N-type injection region which are connected in sequence; S7, forming a dielectric layer, and forming a corresponding contact hole; S8, depositing source electrode metal and grid electrode metal; and S9, carrying out grinding and thinning treatment, and forming drain electrode metal. The beneficial effects of the technical scheme are that on resistance is low, withstand voltage is high during turn-off, and leakage current is small.

Owner:SHANGHAI CHANGYUAN WAYON MICROELECTRONICS

Silicon carbide MOS device

The invention discloses a silicon carbide MOS device which comprises a metal drain electrode. A drain electrode is arranged on the upper end face of the metal drain electrode, an N+ type silicon carbide substrate is arranged on the upper end face of the drain electrode, and an N type silicon carbide drift region is arranged on the upper end face of the N+ type silicon carbide substrate. A siliconcarbide N-epitaxial layer grows on the upper end face of the N type silicon carbide drift region, source trenches are formed at the left upper side and the right upper side of the silicon carbide N-epitaxial layer, and a silicon carbide P+ doped region and a silicon carbide P-type doped region are arranged below the source trenches from top to bottom. Source metal is arranged on the upper end faceof the silicon carbide N-epitaxial layer, and through grooves are formed in the silicon carbide N-epitaxial layer and the source metal. Gate oxide layers are arranged on the inner walls and the outersurfaces of the grooves, gate low-resistance deposits are arranged in the grooves, and a gate oxide layer, a gate low-resistance deposit and gate metal are sequentially arranged at the top ends of the grooves from bottom to top. According to the invention, the gate oxide layer is arranged to be longitudinal and is embedded into the silicon carbide body, and the current path is shorter during conduction, so that the conduction resistance is lower, and the current capability is stronger.

Owner:江西万年芯微电子有限公司