Method for manufacturing a semiconductor device and semiconductor device

A manufacturing method and semiconductor technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problem of low overcurrent protection capability, and achieve the effect of high current capability and high robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0030] In order to solve the problems in the prior art, the present invention provides a method for fabricating a semiconductor device and a semiconductor device, including:

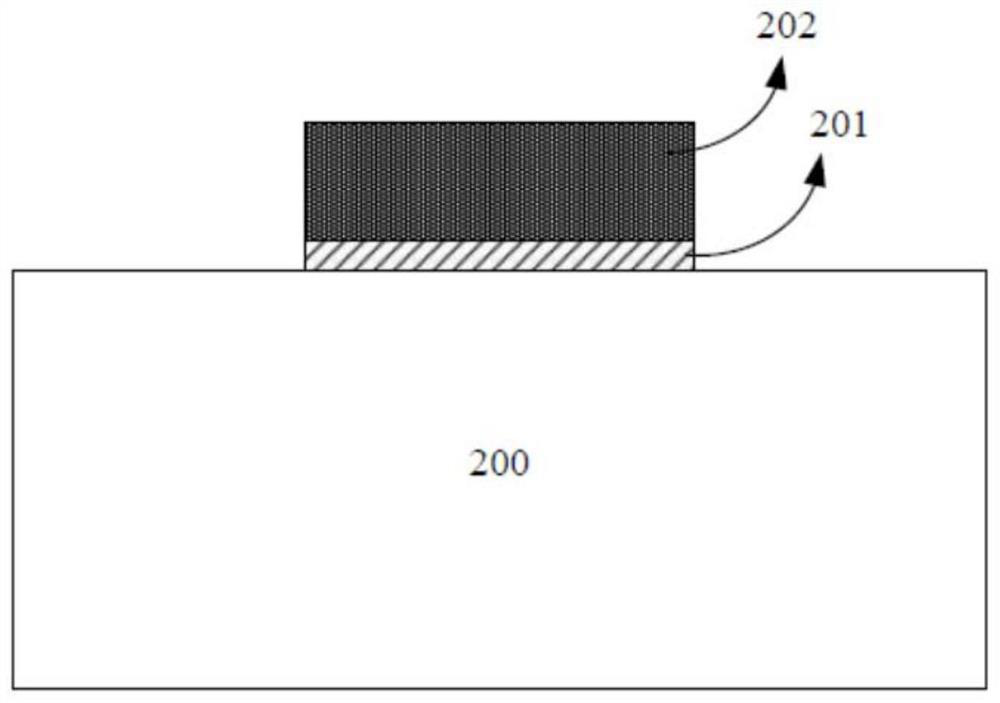

[0031] providing a semiconductor substrate on which a gate structure is formed;

[0032] performing a lightly doped source and drain ion implantation process to form lightly doped source and drain regions in the semiconductor substrate on both sides of the gate structure;

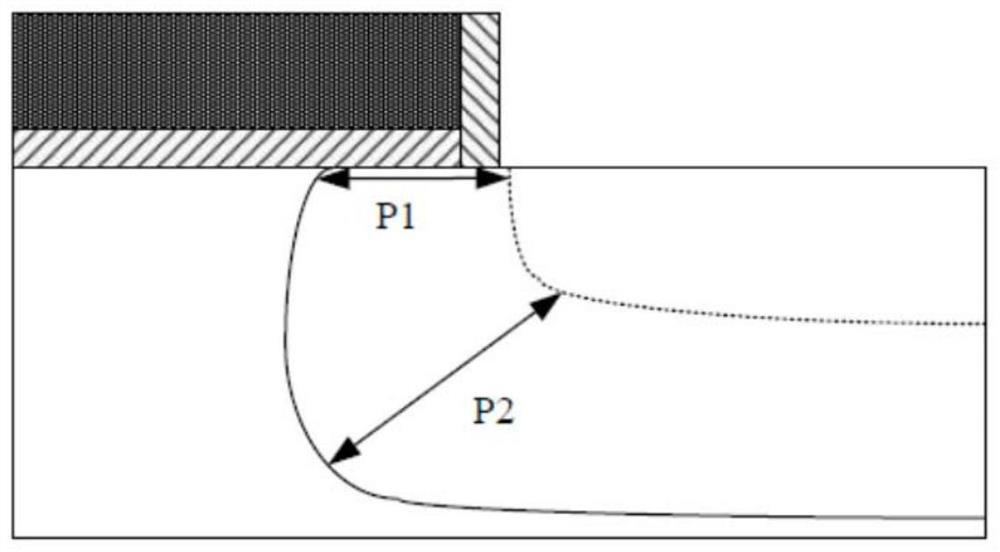

[0033] performing pocket ion implantation to form a pocket ion implantation region at the bottom of the lightly doped source and drain regions;

[0034] performing source and drain ion implantation to form source and drain regions in the semiconductor substrate on both sides of the gate, wherein the lightly doped source and drain regions, the pocket ion implantation region and the source and drain regions Together, a source and a drain having an inclined topography under the gate structure are formed.

[0035] Reference below Figu...

Embodiment 2

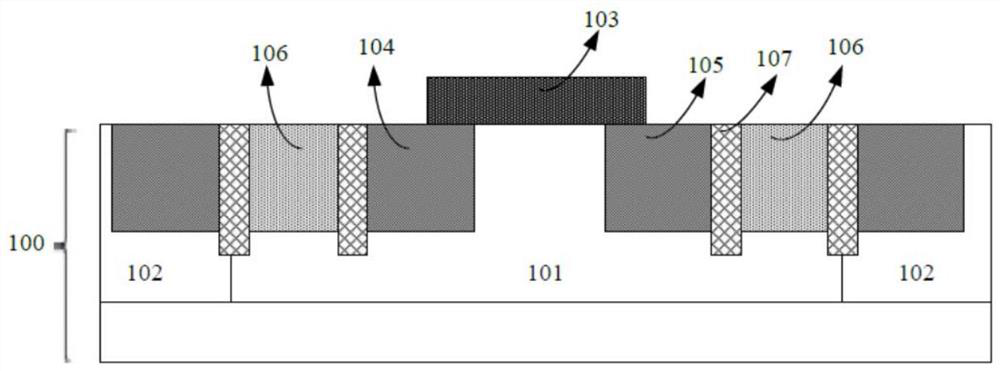

[0068] The present invention also provides a semiconductor device, manufactured by the method described in Embodiment 1, comprising a semiconductor substrate, a gate structure located on the semiconductor substrate, and the semiconductor device located on both sides of the gate structure. The source and drain in the substrate are composed of lightly doped source and drain regions, pocket-type ion implantation regions and source and drain regions, and have an inclined morphology under the gate structure.

[0069] Exemplarily, the semiconductor substrate is a P-type semiconductor substrate, and the semiconductor device is a GGNMOS device.

[0070] Since the source-drain has a source-drain with a sloped topography under the gate structure, the current path at the bottom of the drain is smaller during the electrostatic discharge, so that more current passes through the bottom of the drain during the electrostatic discharge At this time, the surface current is less likely to be con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More