Semiconductor device and process for fabricating the same

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of increased impedance, high cost, and thinning limitations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

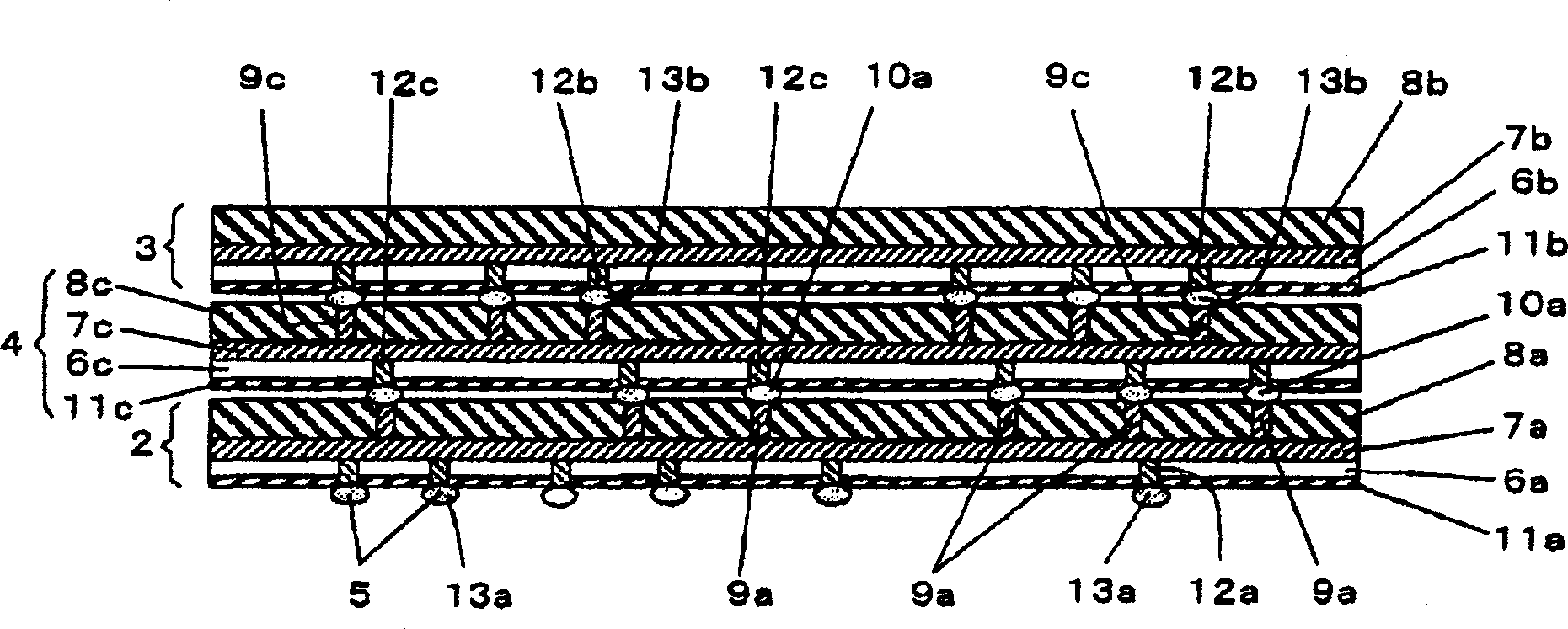

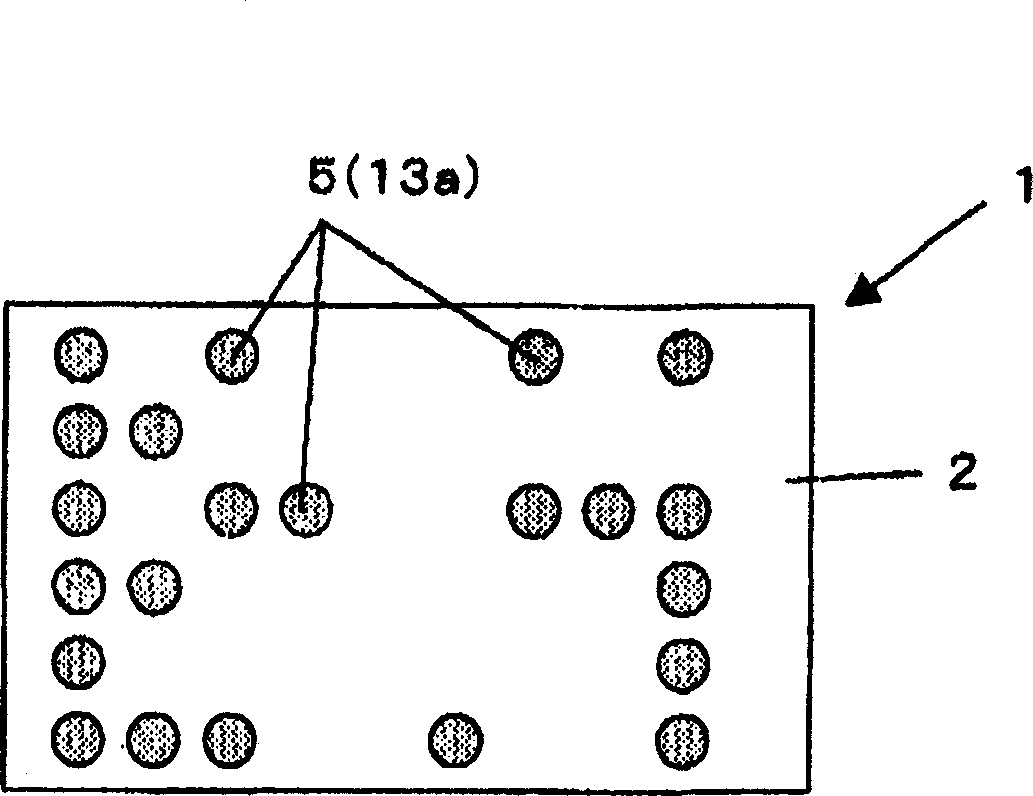

[0157] Figure 1 to Figure 20 It is a diagram related to the stacked semiconductor device according to the first embodiment of the present invention. Figure 1 to Figure 3 is a diagram related to the structure of a stacked semiconductor device, Figure 4 to Figure 19 is a diagram related to the manufacture of a stacked semiconductor device, Figure 20 It is a diagram showing a mounted state of a stacked semiconductor device.

[0158] As shown in FIG. 2 , the stacked semiconductor device 1 manufactured by the manufacturing method of the present invention includes: a quadrilateral first semiconductor device 2 positioned at the next level, positioned at an intermediate level and fixedly stacked on the first semiconductor device 2 The third semiconductor device 4 on the surface, and the second semiconductor device 3 positioned on the upper surface and fixedly stacked on the upper surface of the third semiconductor device 4 . In the stacked semiconductor device 1 of the first em...

Embodiment 2

[0226] Figure 21 It is a cross-sectional view schematically showing a stacked semiconductor device according to Embodiment 2 of the present invention. In the second embodiment, in the gap between the first semiconductor device 2 and the third semiconductor device 4 and in the gap between the third semiconductor device 4 and the second semiconductor device 3 in the stacked semiconductor device 1 of the first embodiment An insulating resin is filled to form underfill layers 50 and 51 . The voids are buried by the underfill layers 50 , 51 , so that short-circuit failures due to foreign matter contamination or the like can be prevented. For example, polyimide resin is filled in the cavity as an insulating resin in a vacuum environment, and then baked to cure it.

Embodiment 3

[0228] Figure 22 (a) and (b) are schematic cross-sectional views of a two-stage stacked fixed type stacked semiconductor device 1 according to Embodiment 3 of the present invention. Figure 22 In both (a) and (b), the semiconductor substrates 6a, 6b are placed on top, and the first insulating layers 8a, 8b are placed on the bottom to perform lamination and fixing. Both bump electrodes 10 a on the lower surface of the first semiconductor device 2 serve as external electrode terminals 5 . In addition, the bump electrodes 13a on the upper surface of the first semiconductor device 2 form a bonding body, and the second semiconductor device 3 is laminated and fixed. That is, the bump electrodes 13 a mounted on the penetration electrodes 12 a on the upper surface side of the first semiconductor device 2 are connected to the columnar electrodes 9 a on the lower surface of the second semiconductor device 3 .

[0229] In addition, in Figure 22 In (a), no electrodes are exposed on t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More