Patents

Literature

64results about How to "Shorten the current path" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

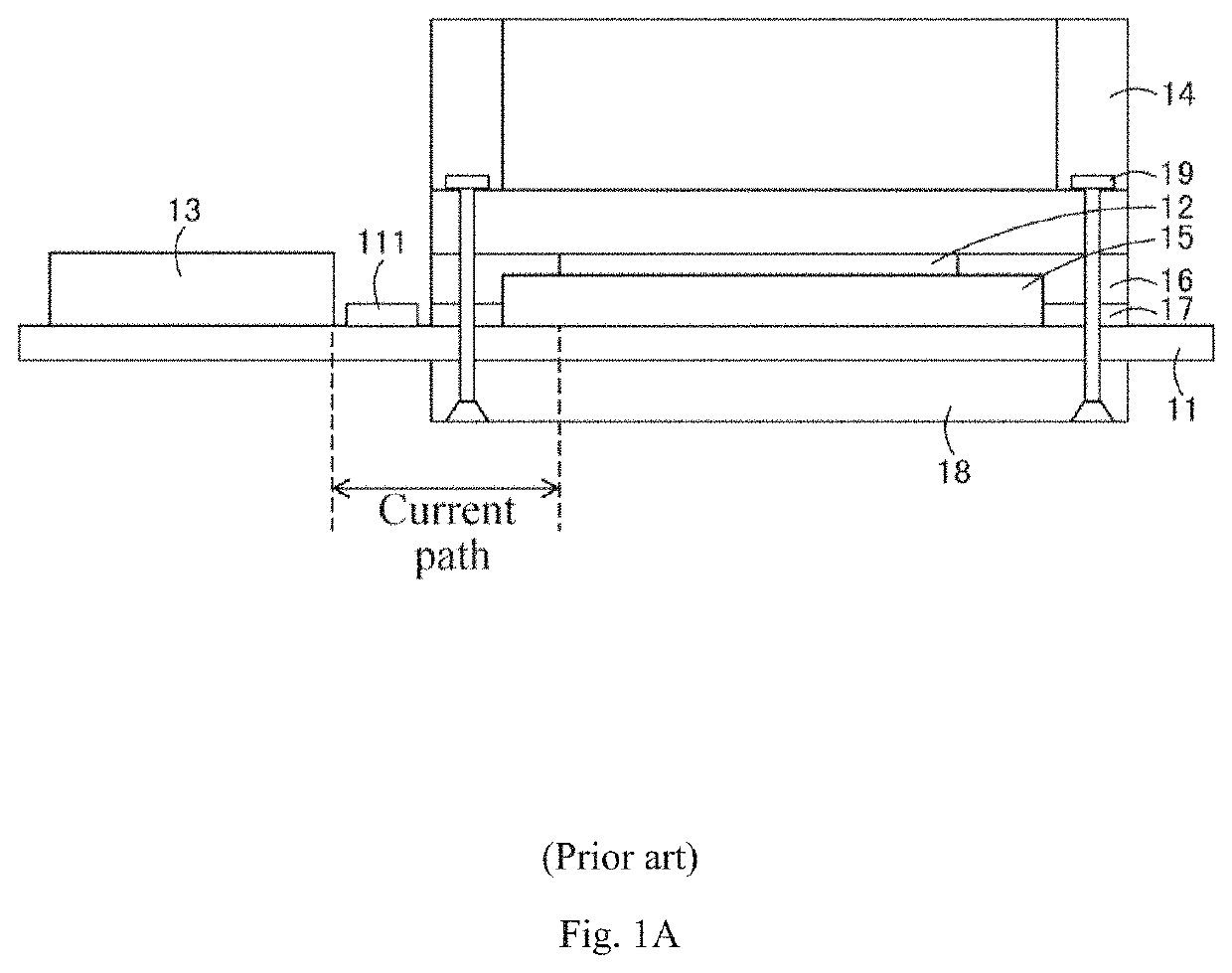

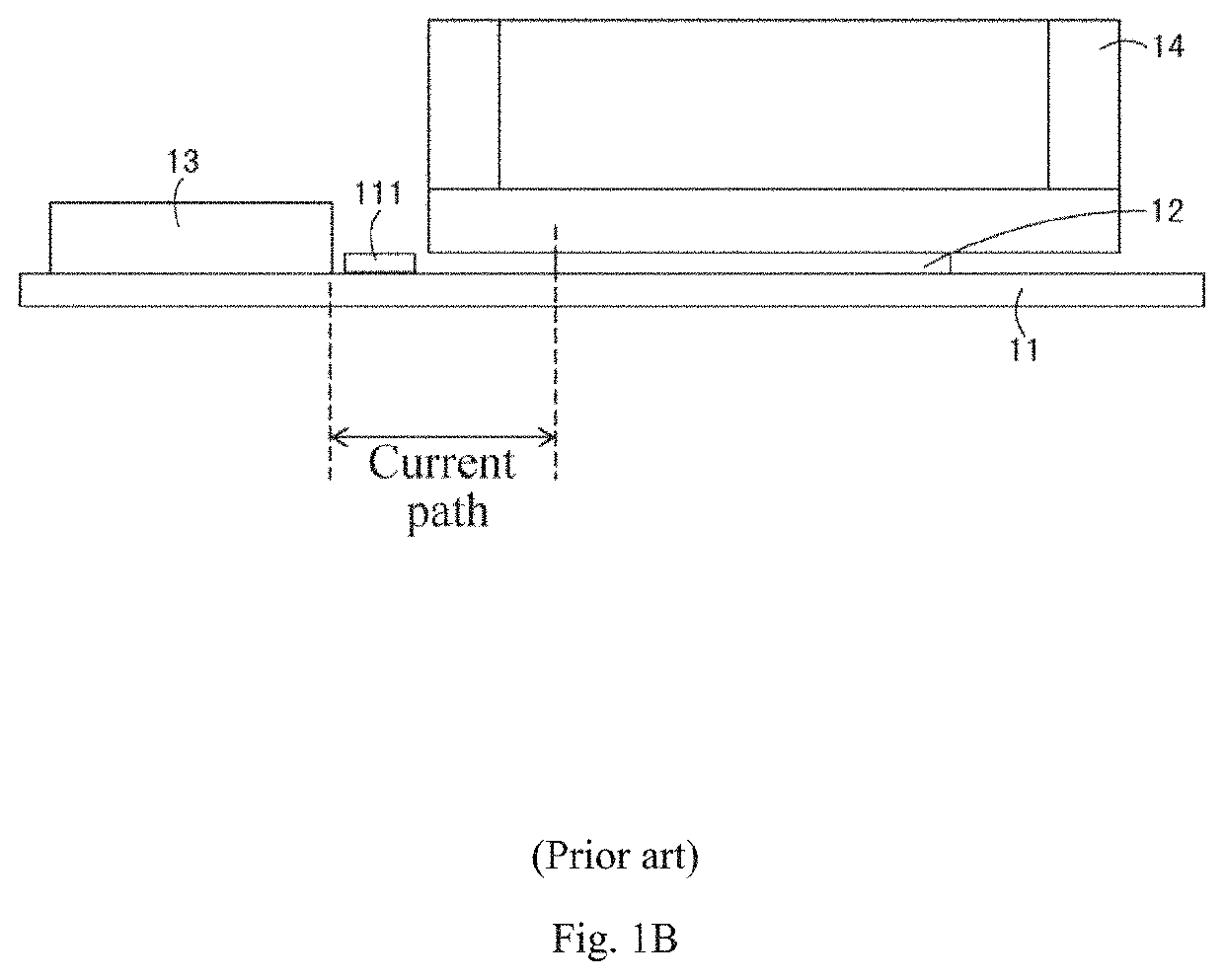

Semiconductor device

InactiveCN1776911ALower resistanceShorten the current pathTransistorSolid-state devicesMOSFETElectrical resistance and conductance

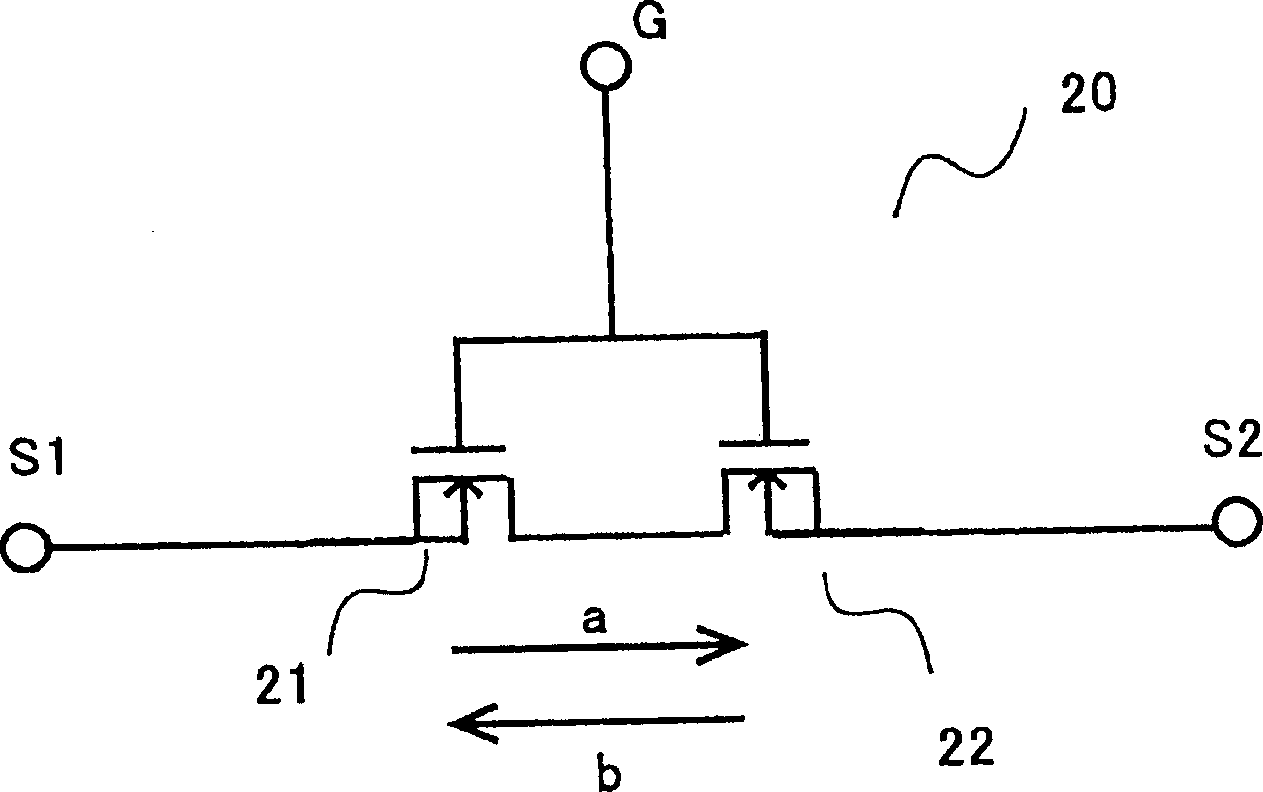

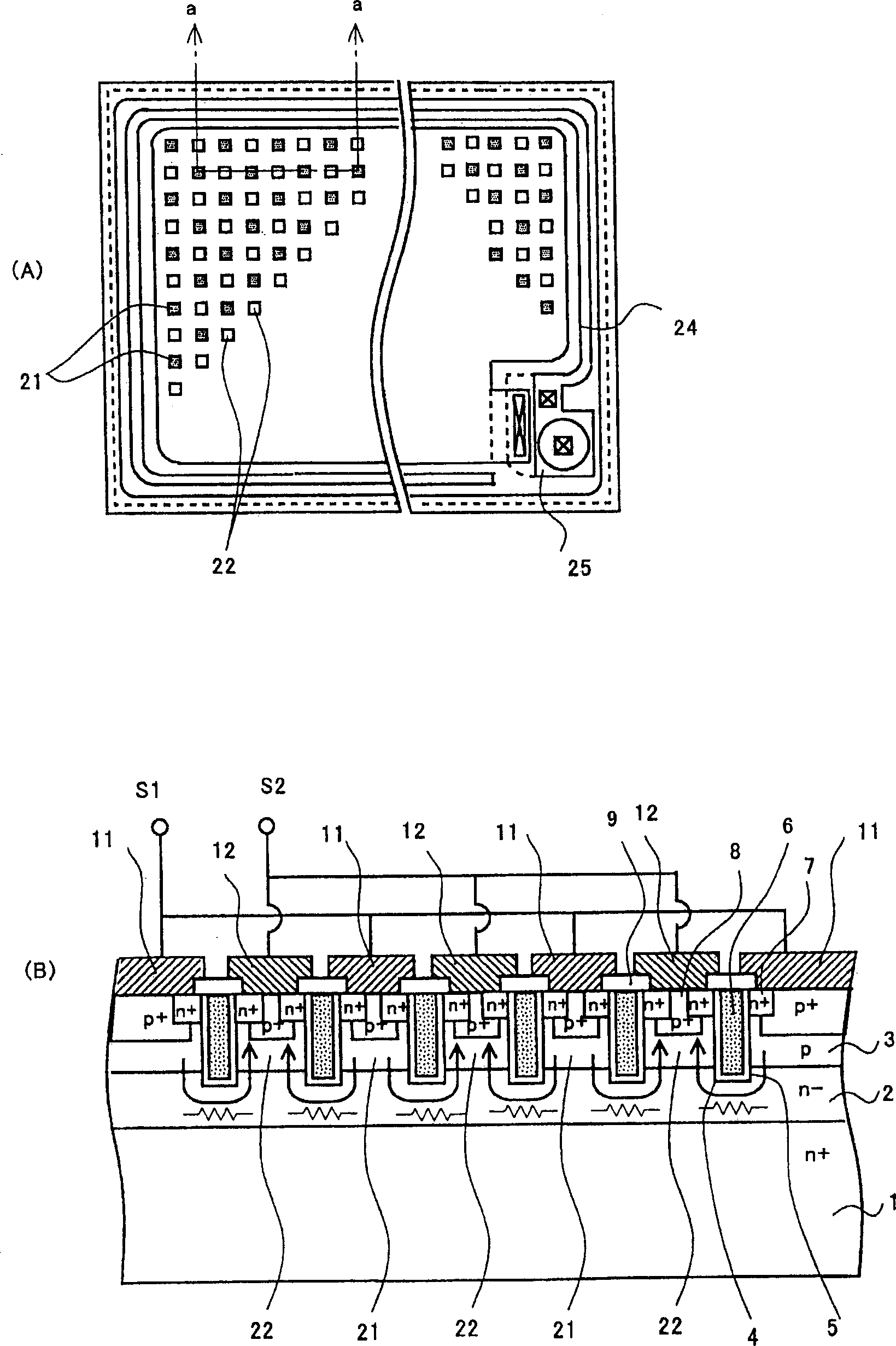

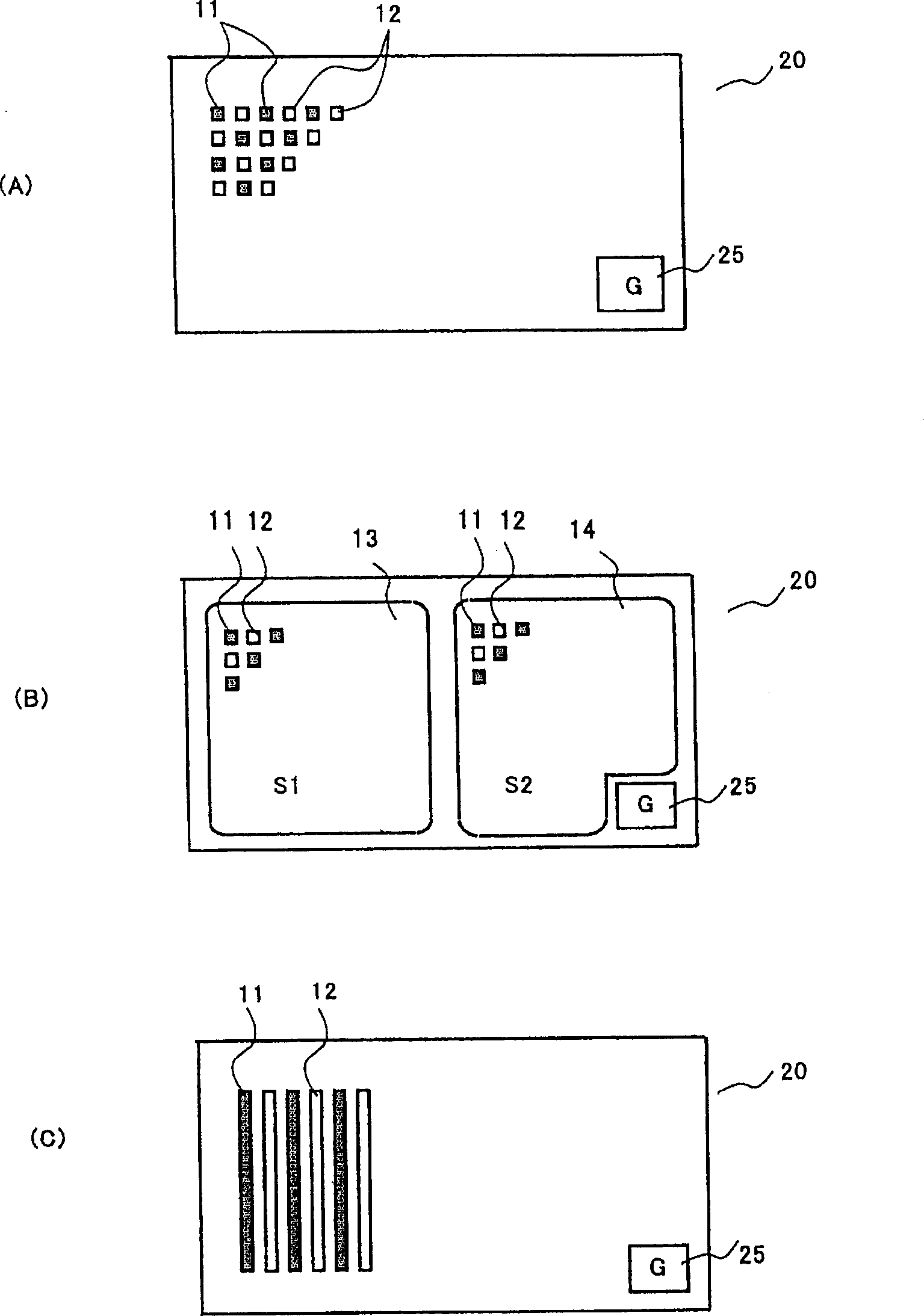

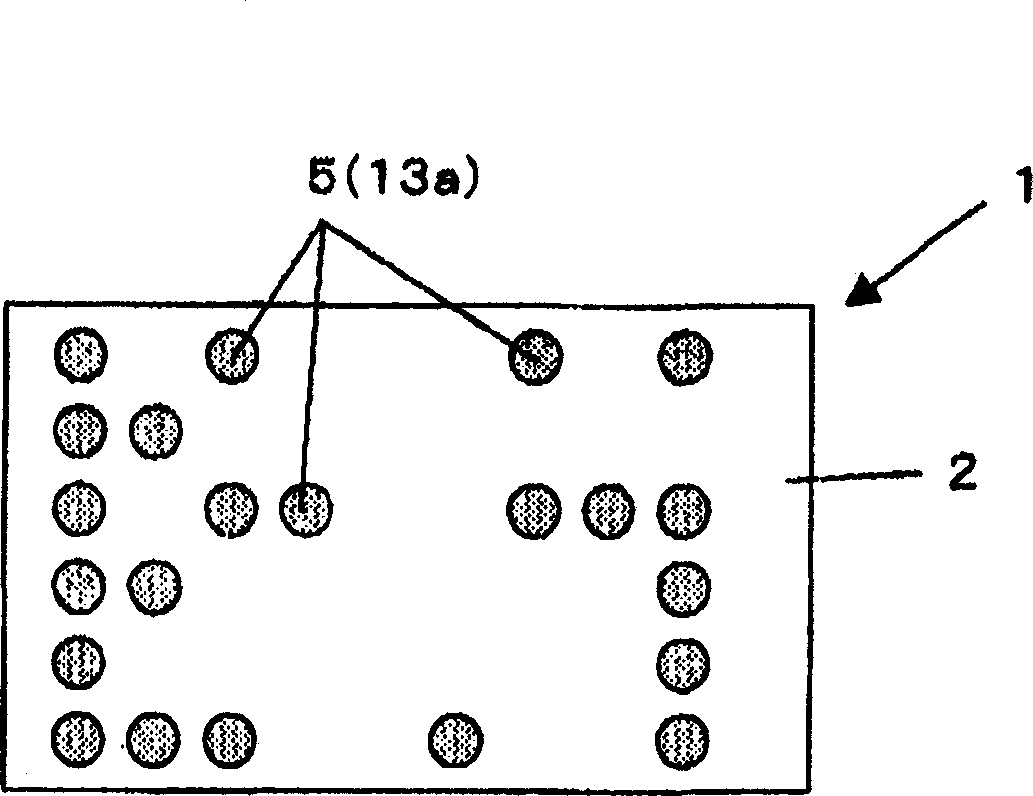

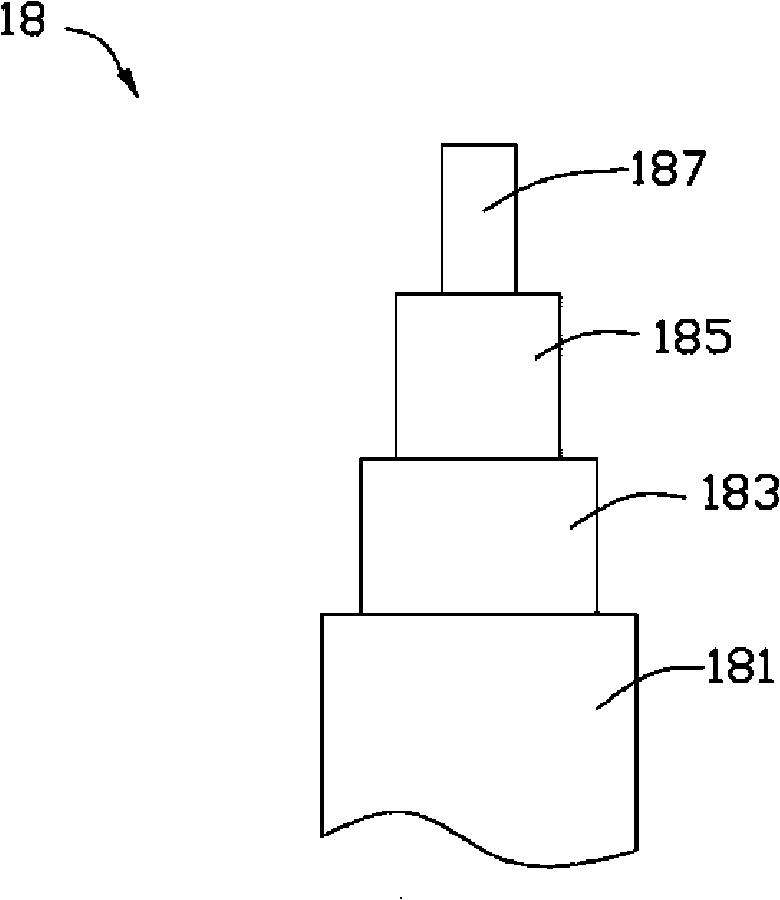

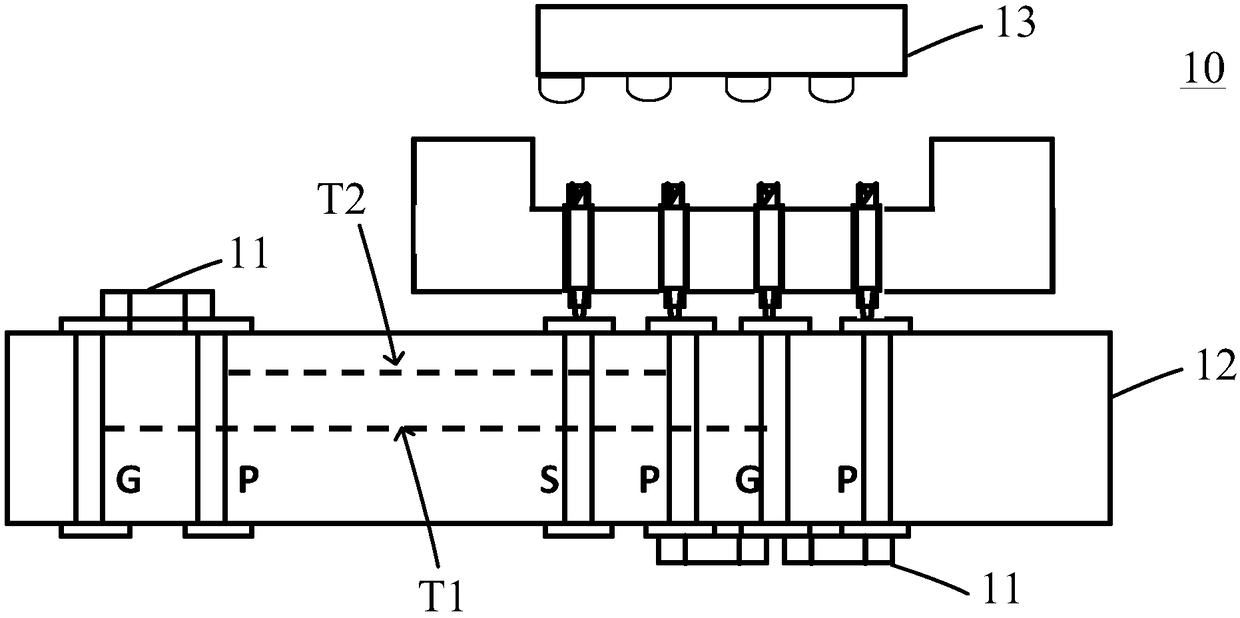

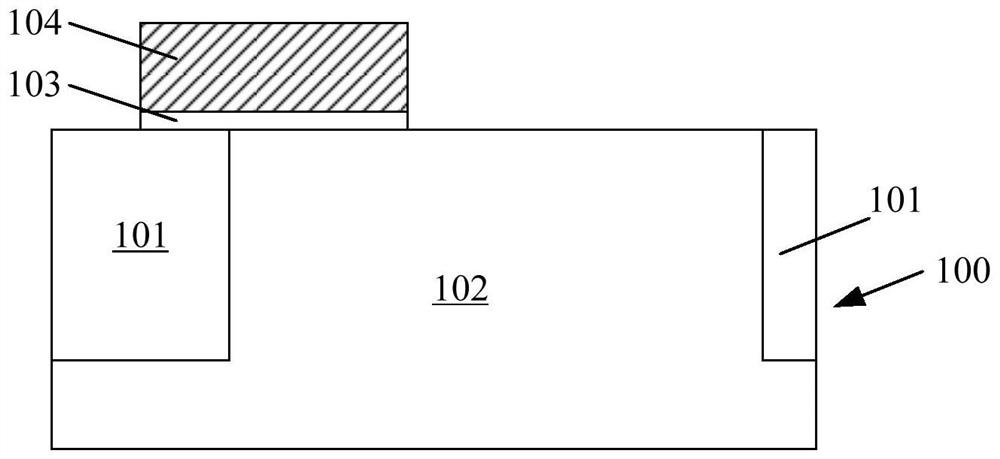

In a semiconductor device, the conventional monolithic dual MOSFET has a structure in which two MOSFET chips sharing a common drain region are arranged side by side, so the resistance value of the drain region is high, and the reduction of the on-resistance of the device is limited. In the semiconductor device of the present invention, the first MOS transistors connected to the first source electrode and the second MOS transistors connected to the second source electrode are alternately arranged adjacent to each other on one chip. Different potentials are respectively applied to the first source electrode and the second source electrode, and the switching control of the two MOS transistors is performed through one gate terminal. On-resistance can be reduced because current flows around the trench.

Owner:SANYO ELECTRIC CO LTD

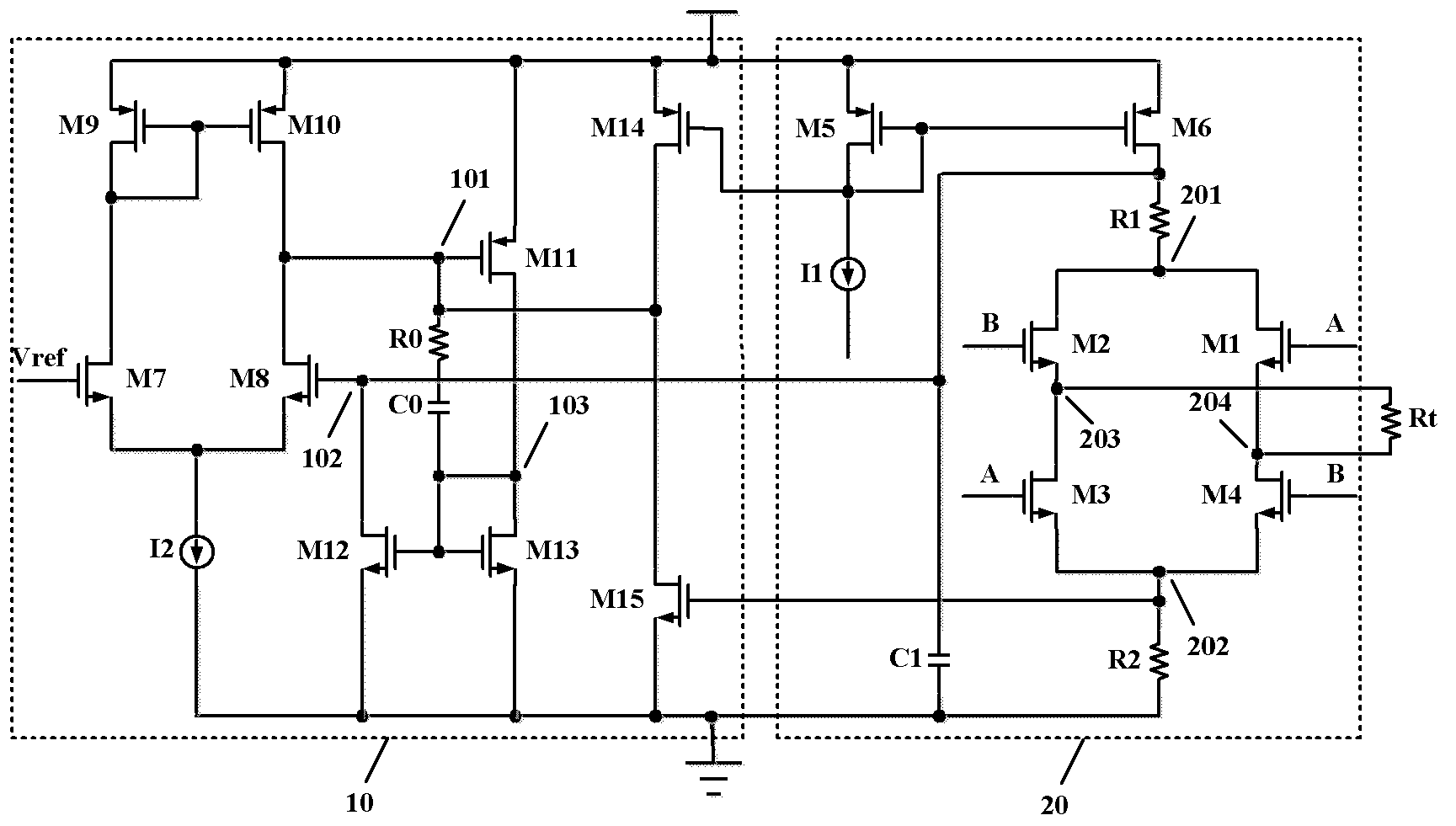

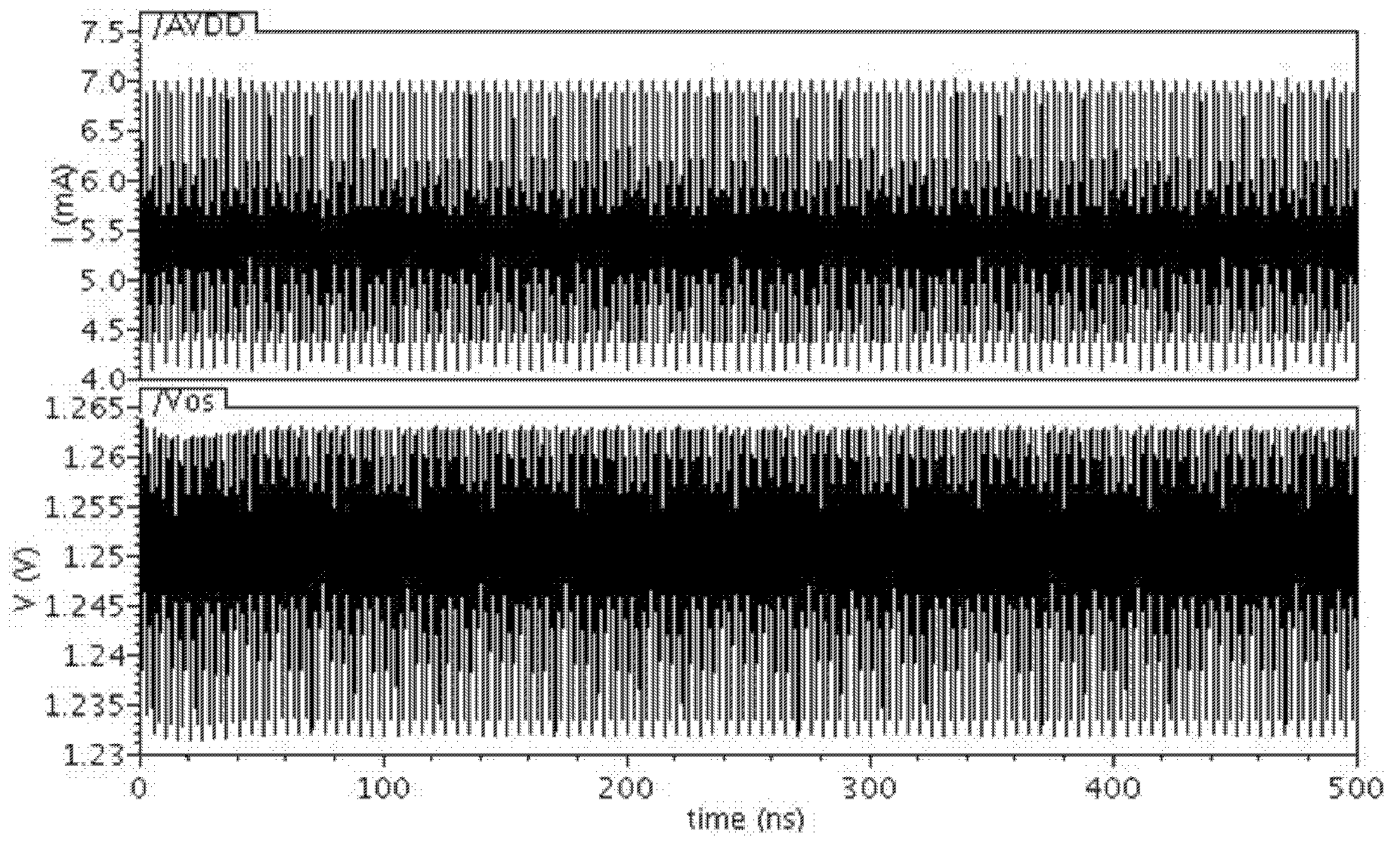

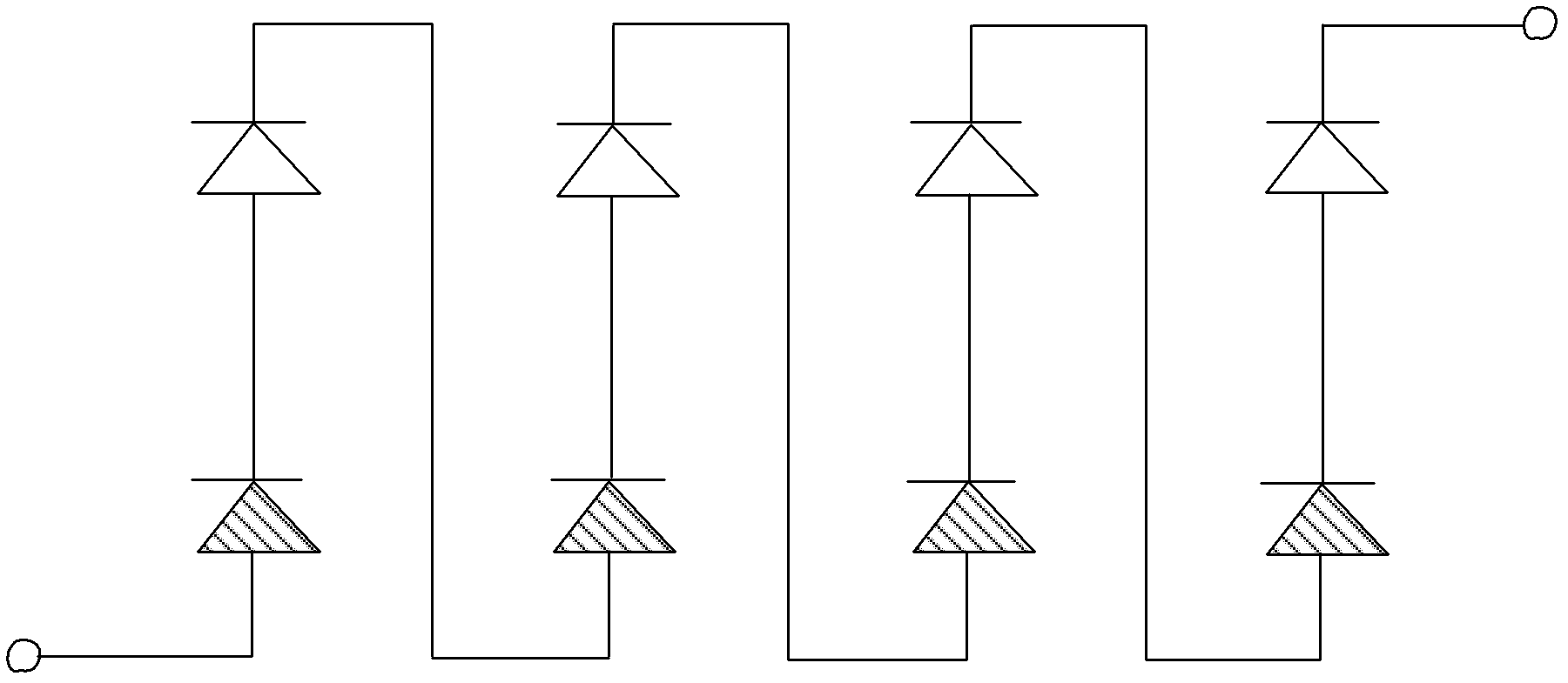

Low voltage differential signal driver provided with common-mode feedback

ActiveCN103166627AIncrease power consumptionReduce power consumptionLogic circuits coupling/interface using field-effect transistorsDriver circuitLow voltage

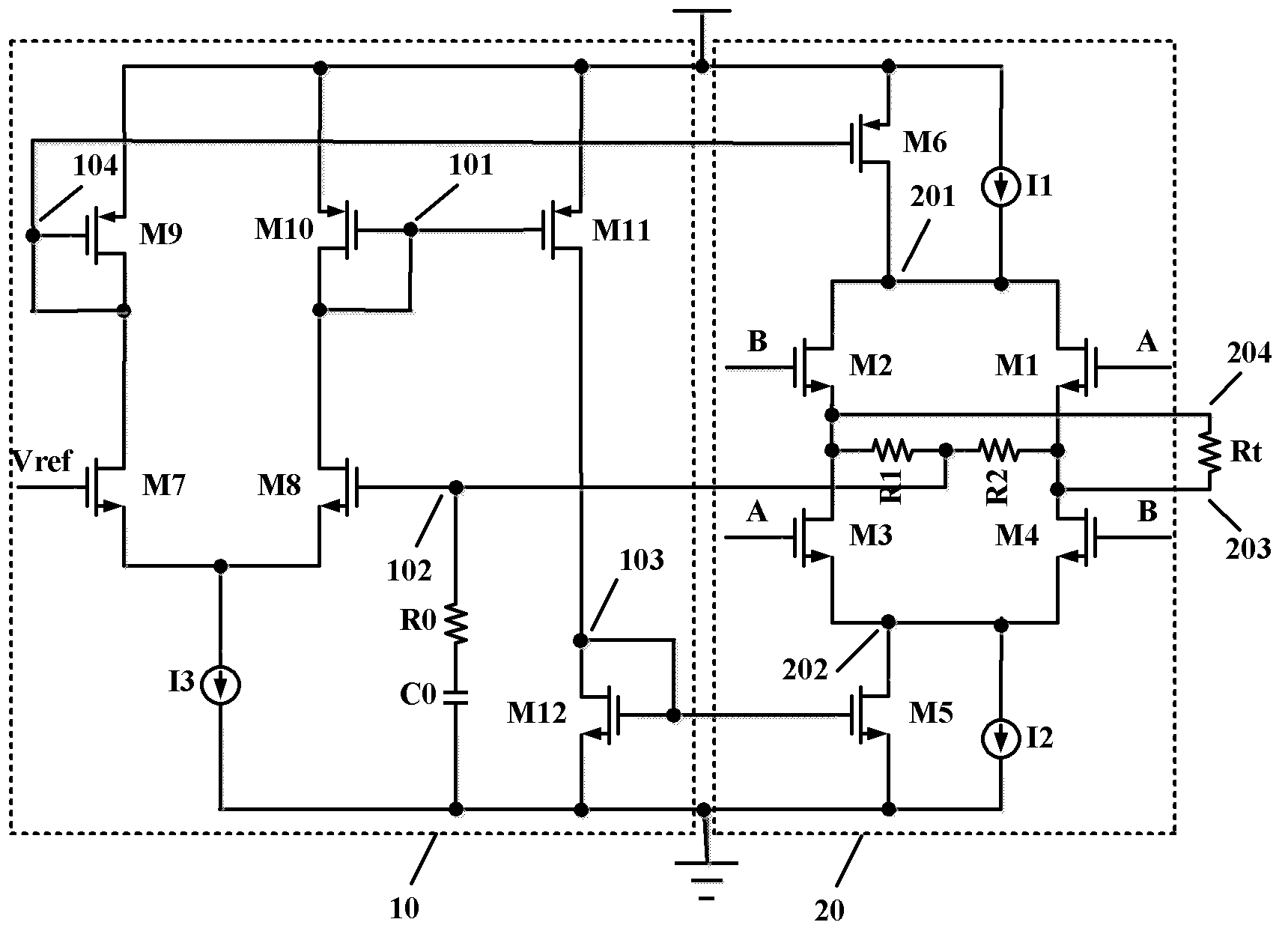

The invention discloses a low voltage differential signal driver provided with common-mode feedback. The driver comprises a common-mode feedback circuit (10) and a driving circuit (20), wherein the common-mode feedback circuit (10) is used for stabilizing common-mode voltage of outputted low voltage differential signals, and the driving circuit (20) is sued used for generating the low voltage differential signals. The low voltage differential signal driver provided with common-mode feedback utilizes the mode of cancelling extraction of large resistance of common mode points, and achieves the low voltage differential signaling (LVDS) driver provided with the common-mode feedback. The driver is simple in biasing circuit, is improved in performances including power consumption, area and the like, and solves the problems that existing LVDS drivers are complicated in biasing circuit, large in power consumption and large in occupied area of the large resistance of the extracted common mode points.

Owner:SOI MICRO CO LTD

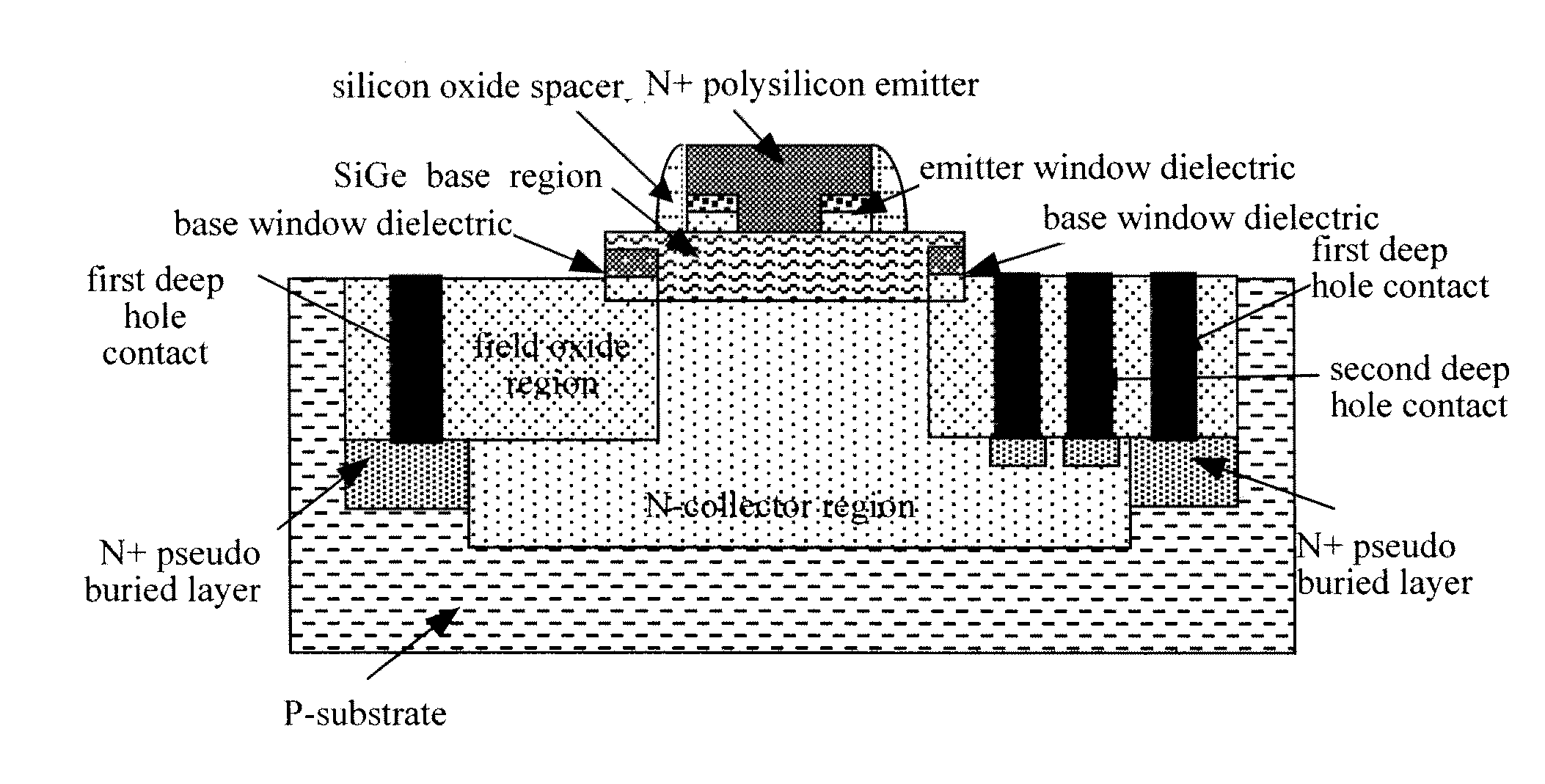

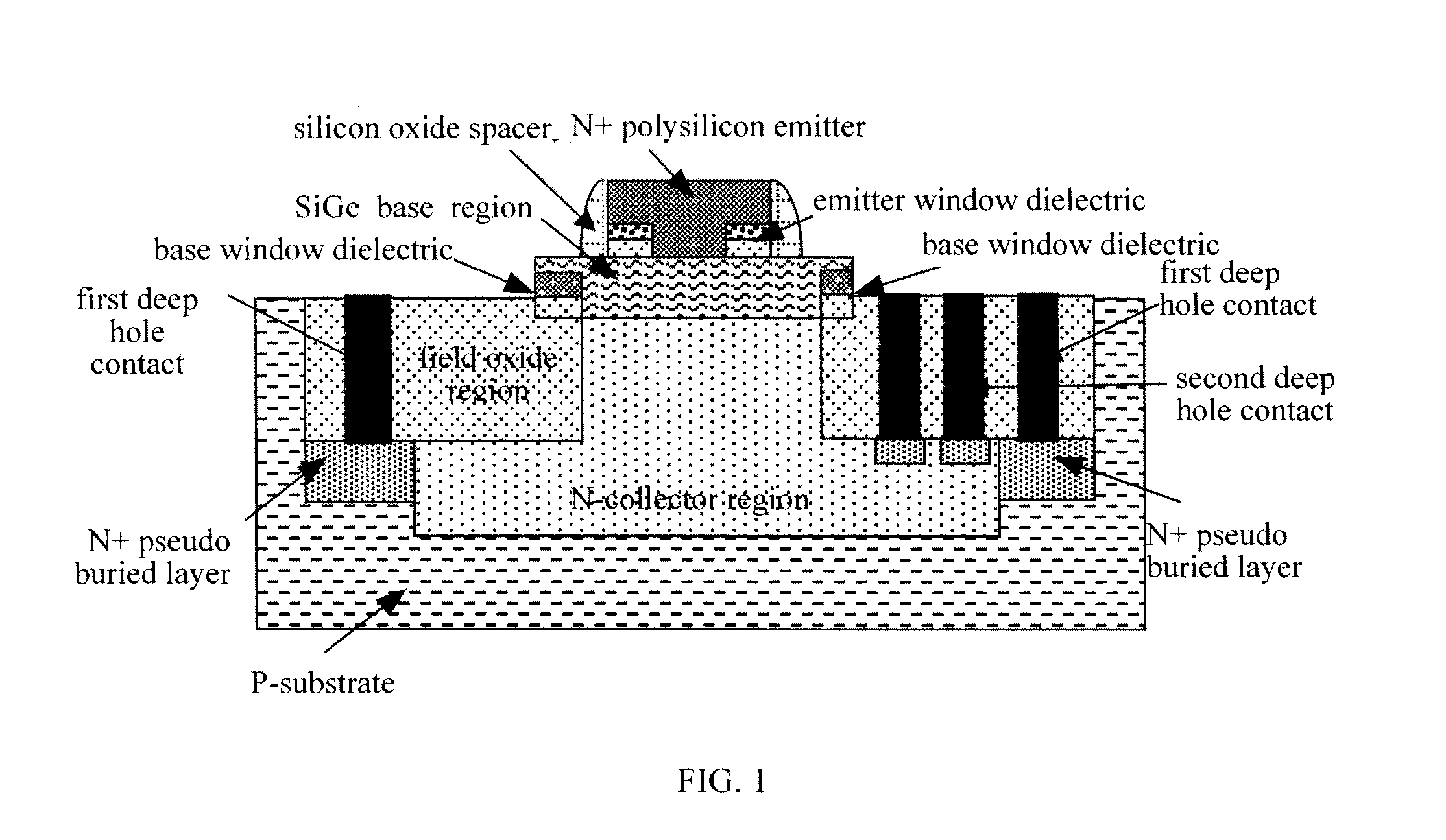

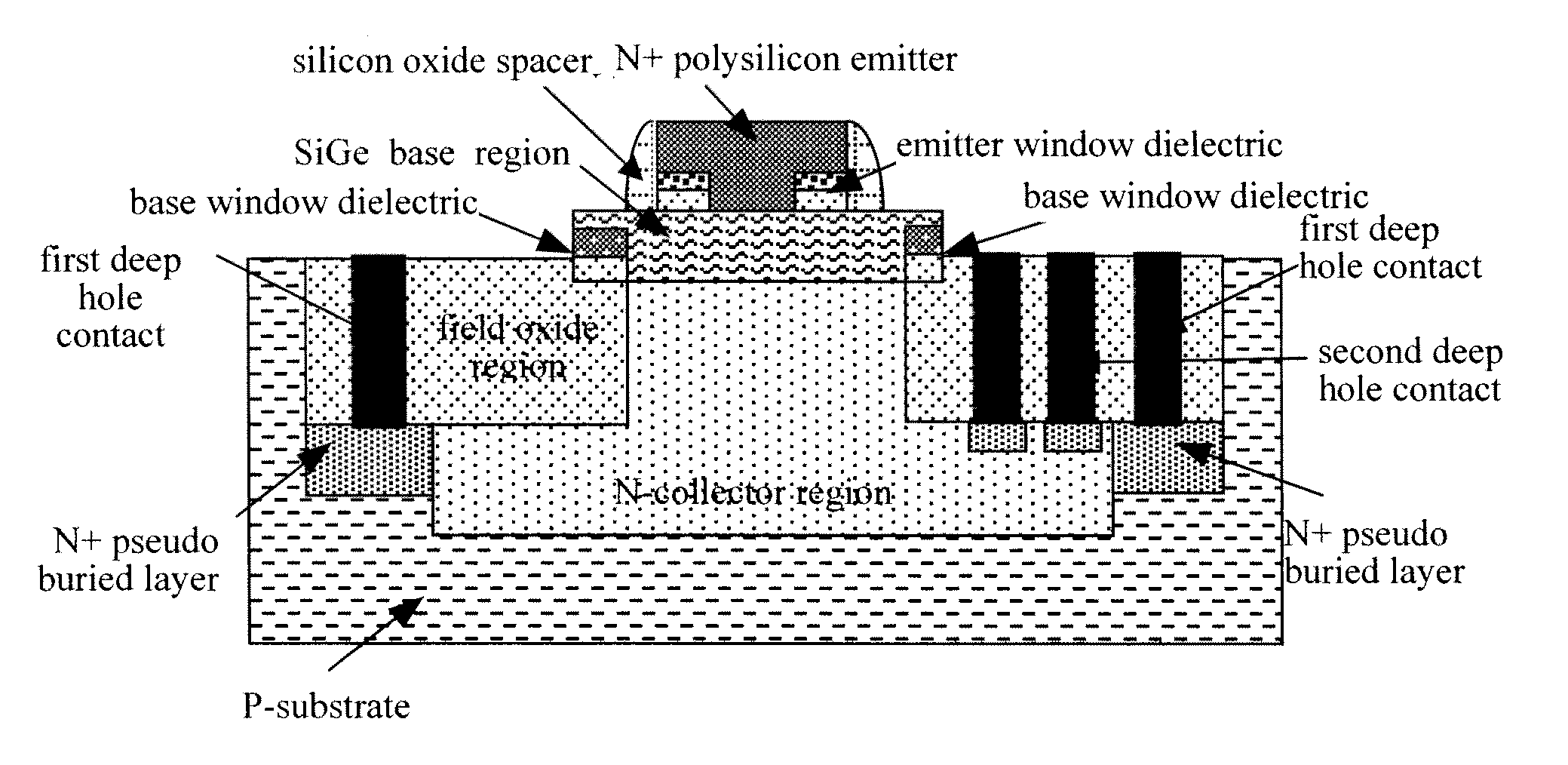

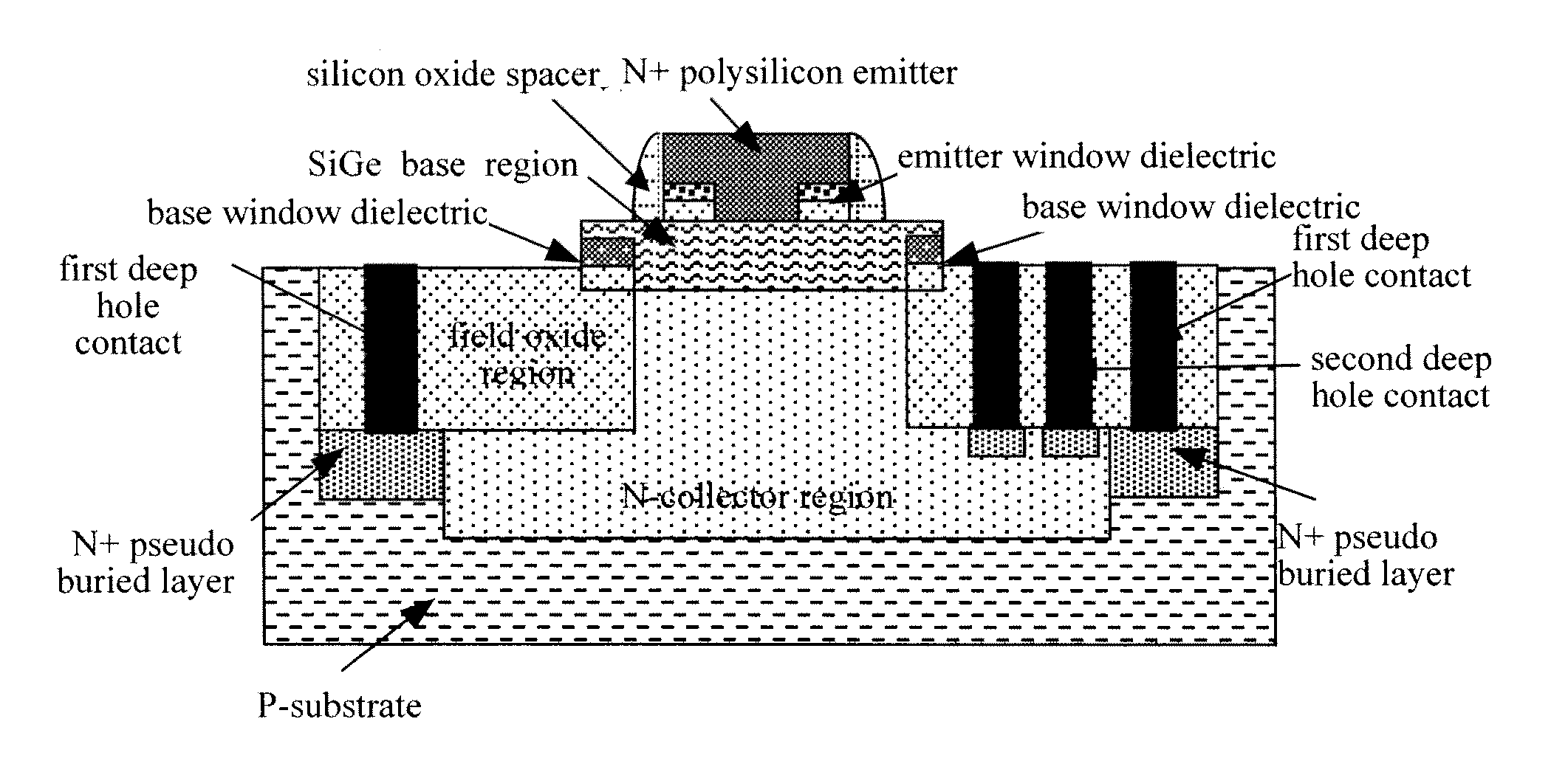

Silicon-germanium heterojunction bipolar transistor

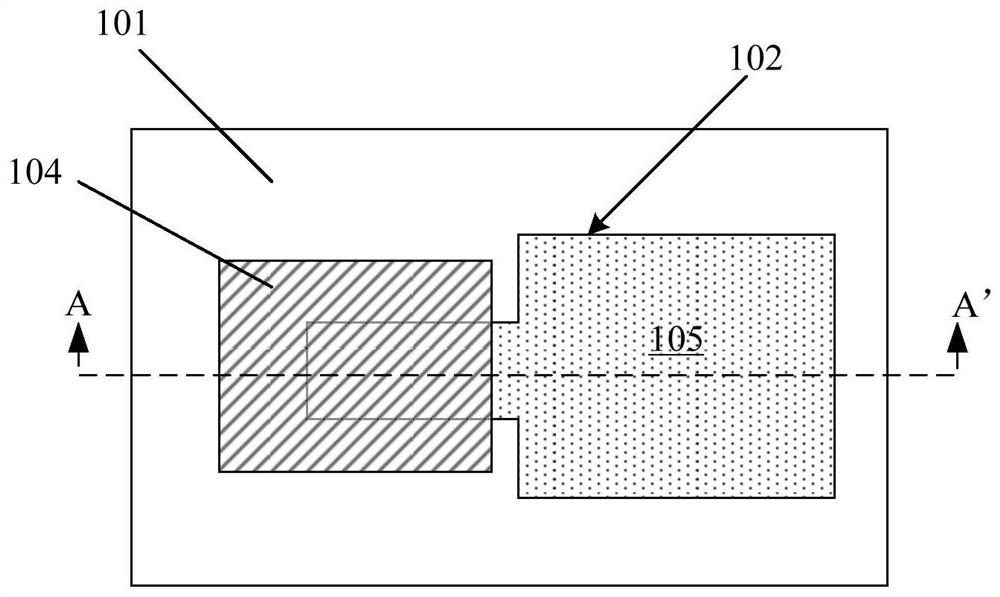

ActiveUS20120074465A1Improve breakdown voltageShorten the current pathSemiconductor/solid-state device manufacturingSemiconductor devicesLateral extensionField oxide

A SiGe HBT formed on a silicon substrate is disclosed. An active area is isolated by field oxide regions; a collector region is formed in the active area and extends into the bottom of the field oxide regions; pseudo buried layers are formed at the bottom of the field oxide regions, wherein each pseudo buried layer is separated by a lateral distance from the active area and connected to a lateral extension part of the collector region; first deep hole contacts are formed on top of the pseudo buried layers in the field oxide regions to pick up collector electrodes; a plurality of second deep hole contacts with a floating structure, are formed in the field oxide region on top of a lateral extension part of the collector region, wherein N-type implantation regions are formed at the bottom of the second deep hole contacts.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

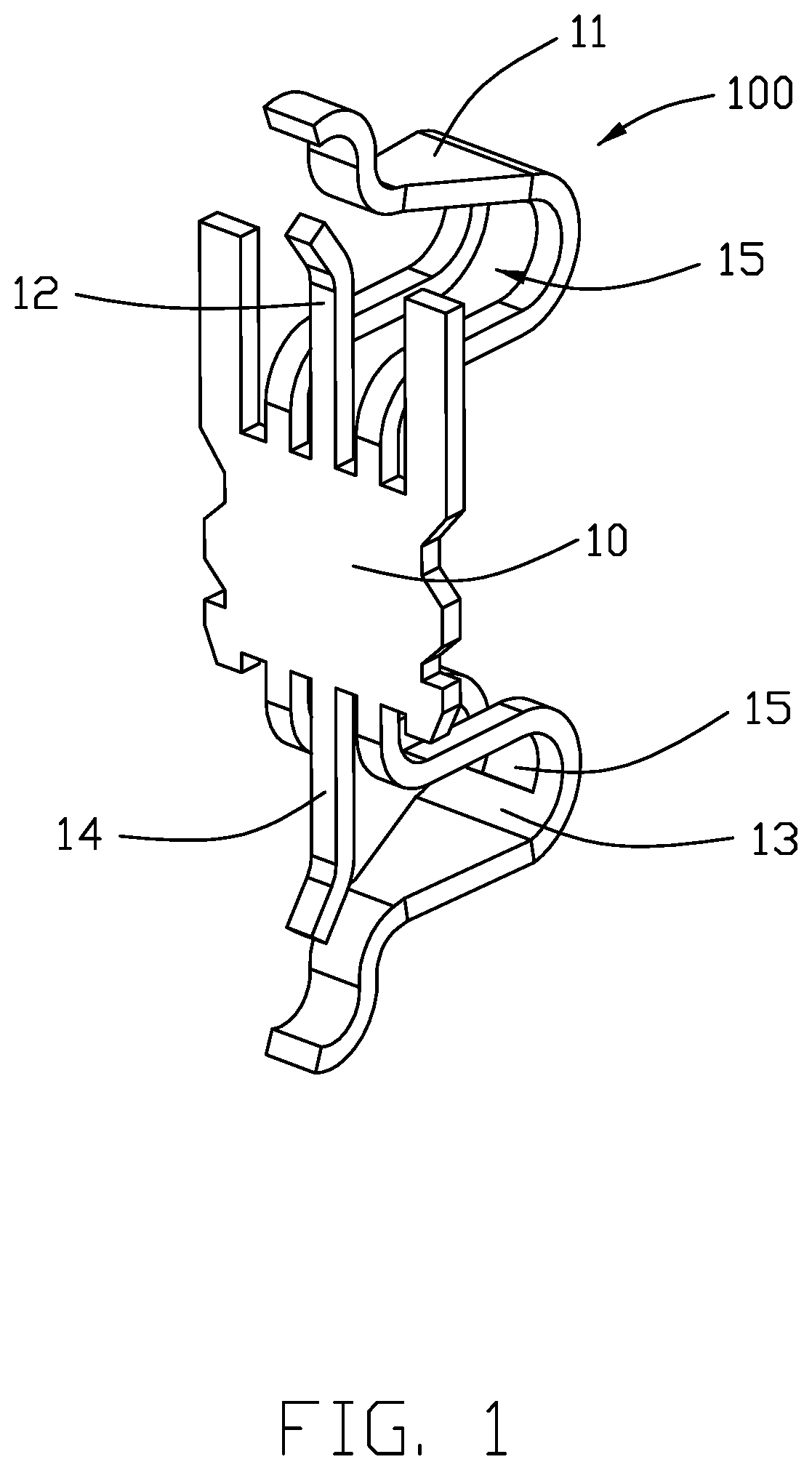

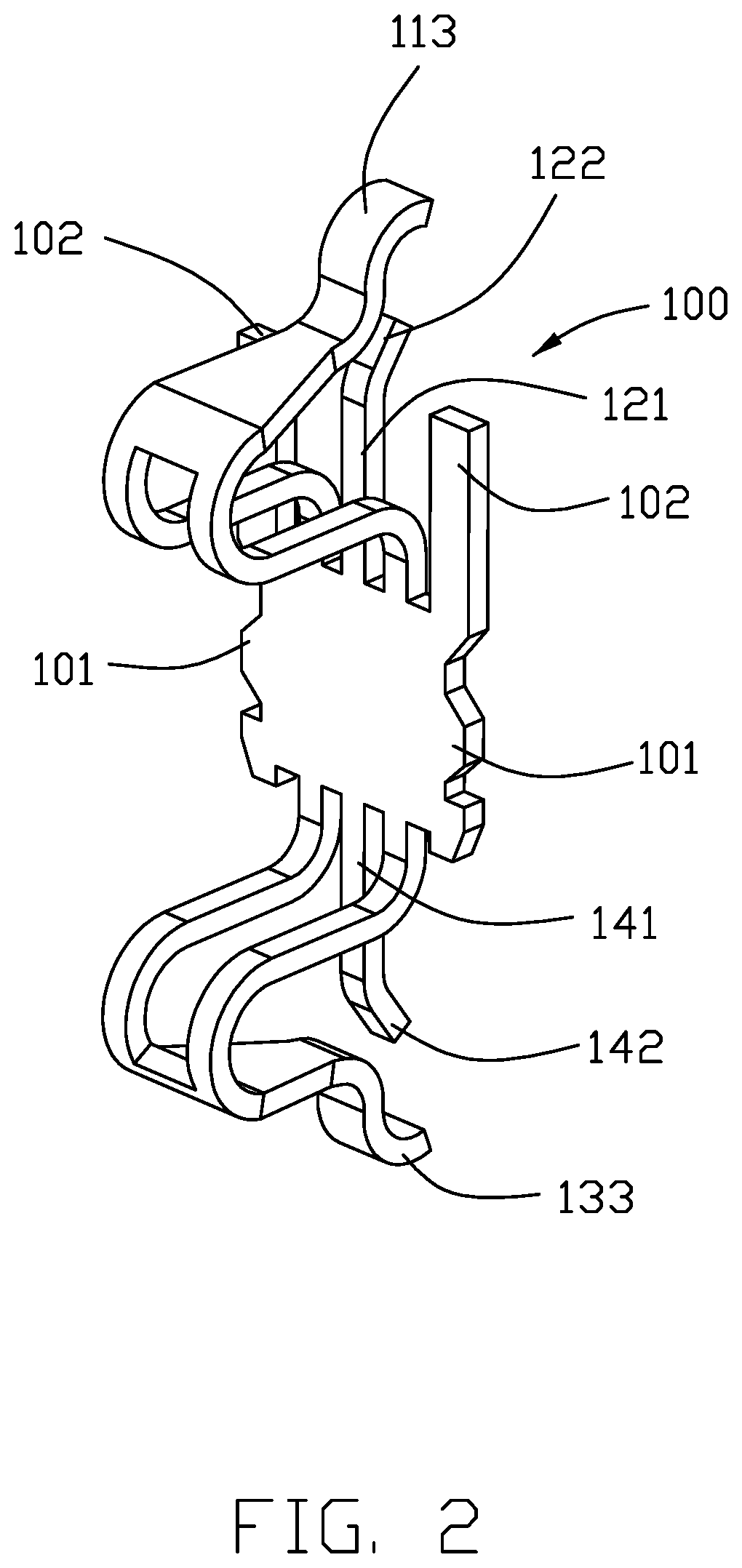

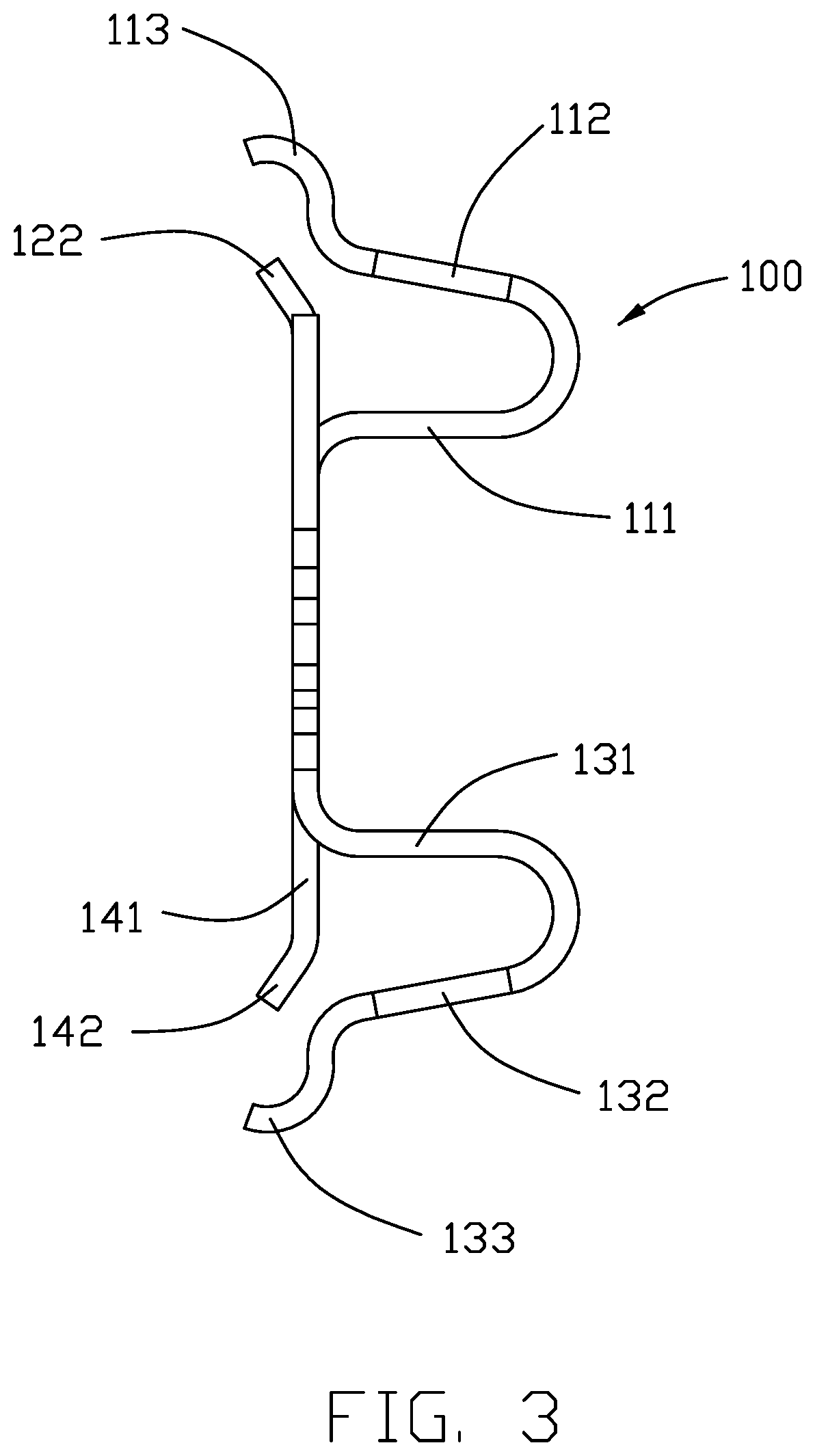

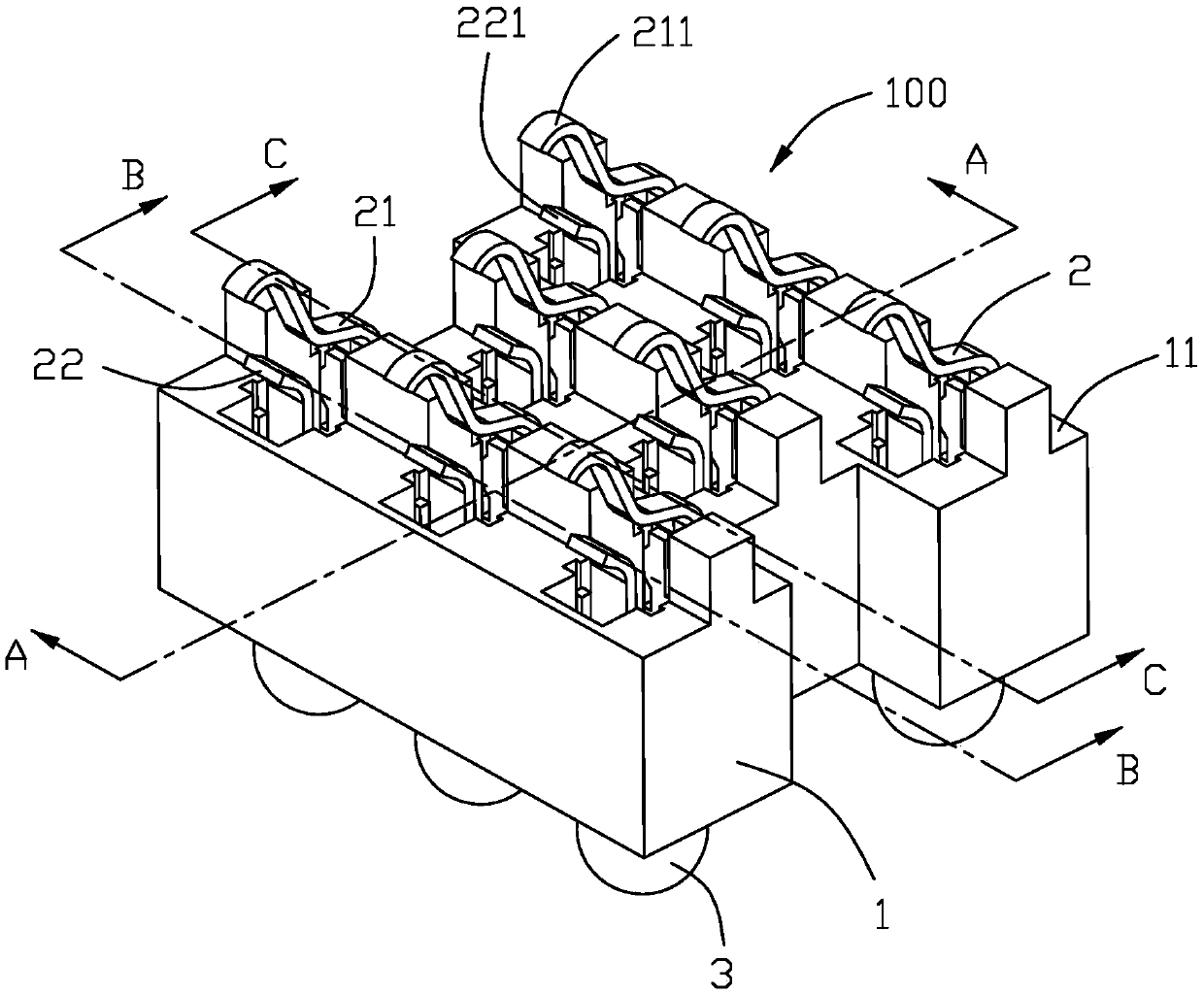

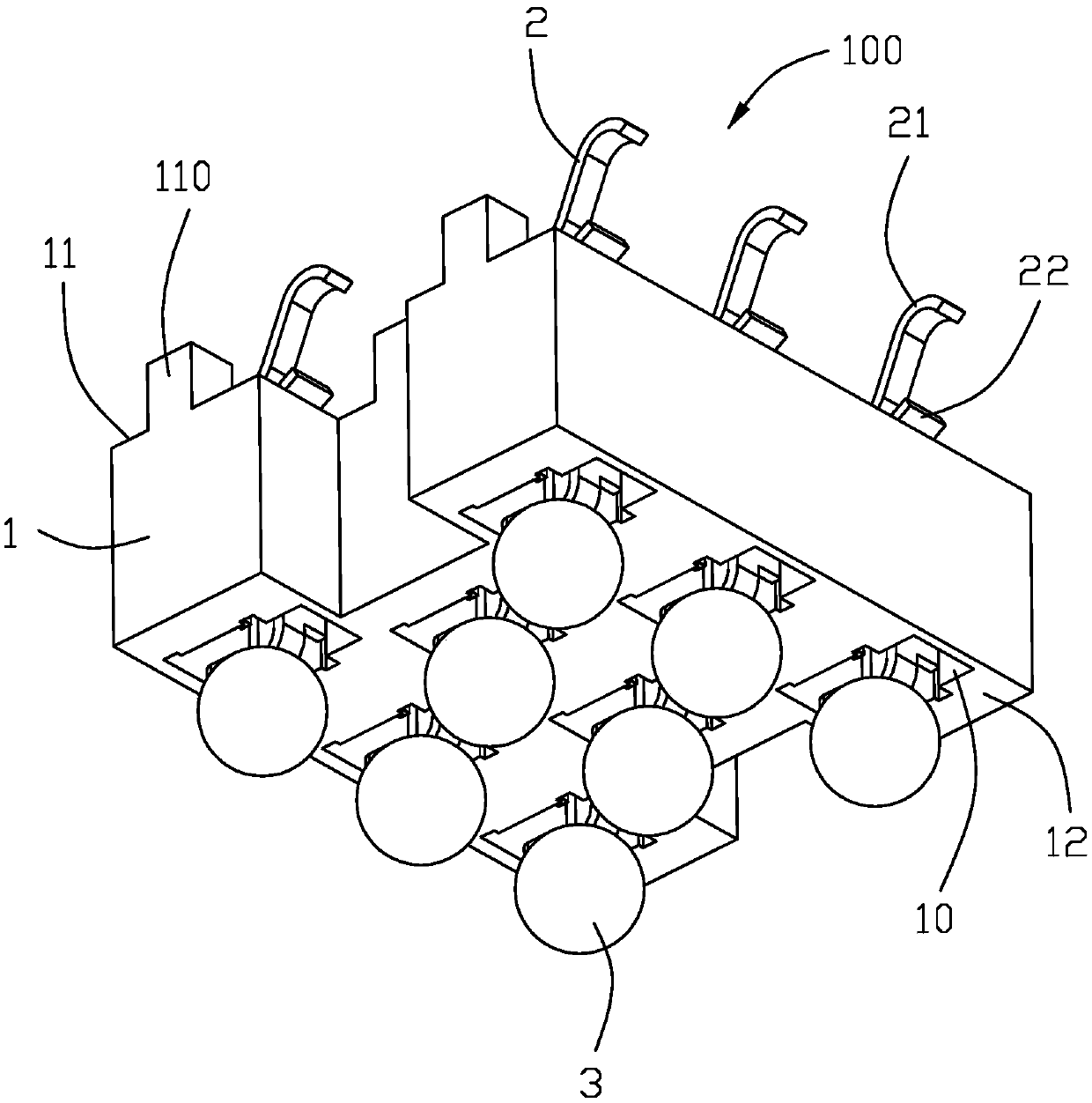

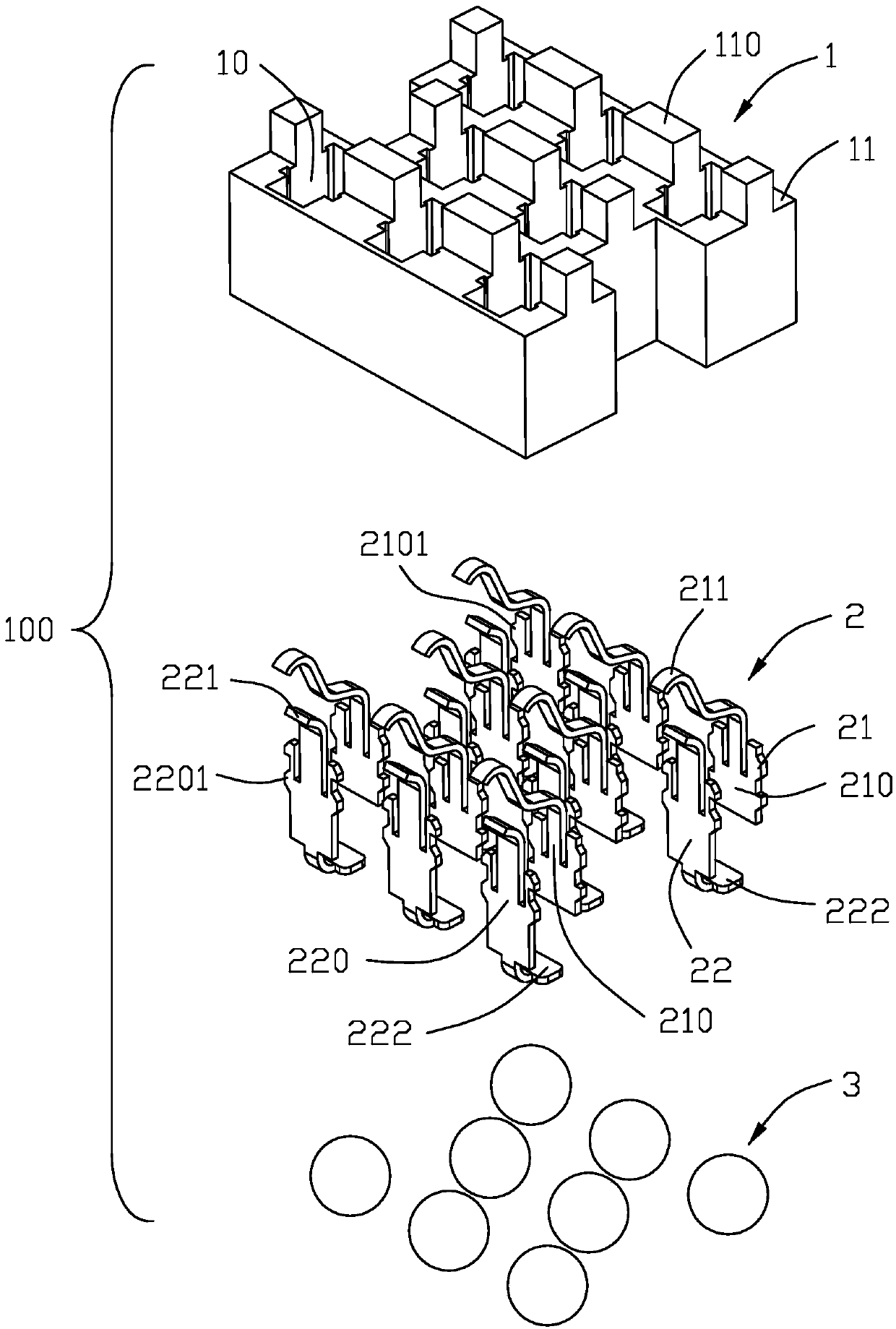

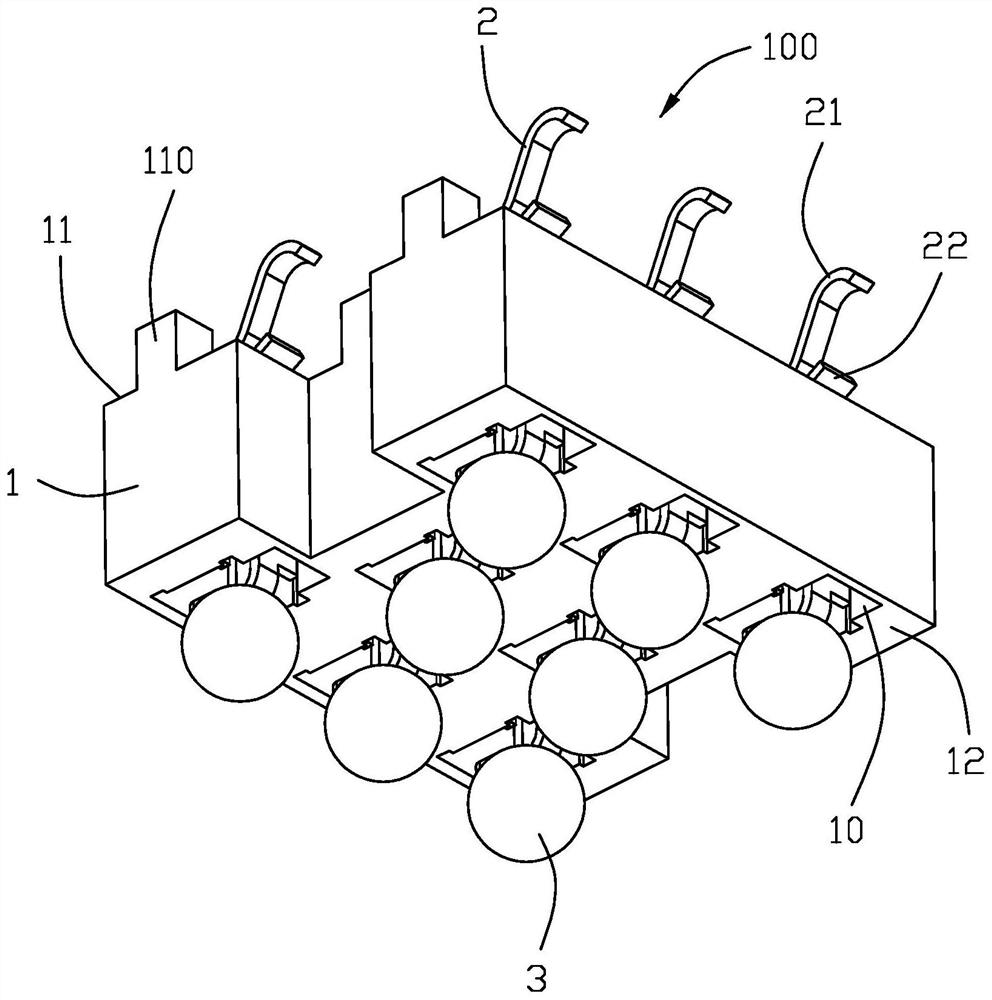

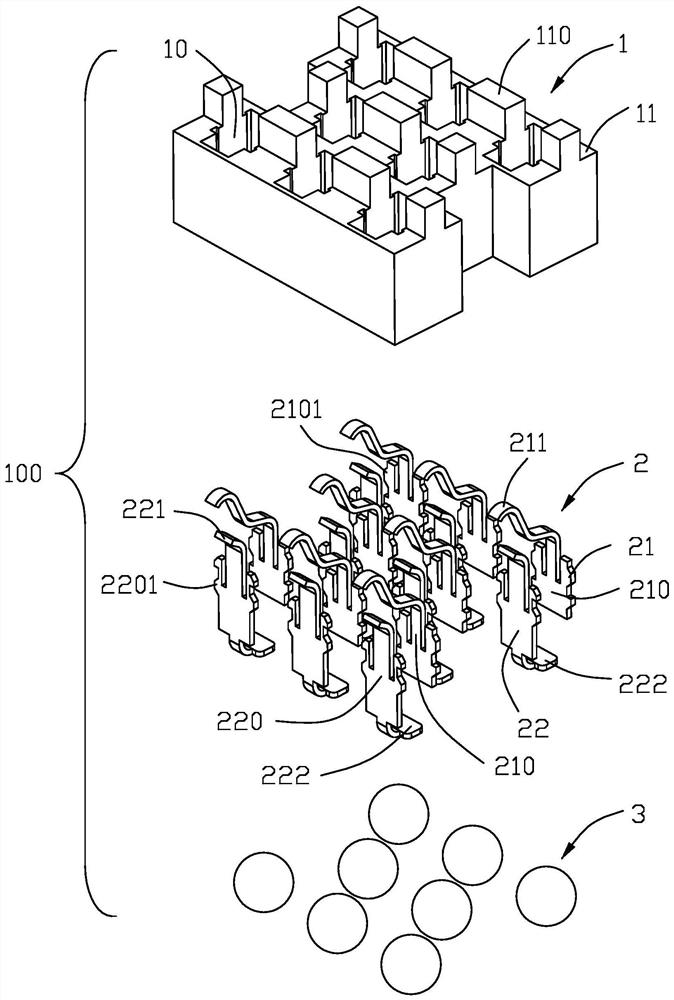

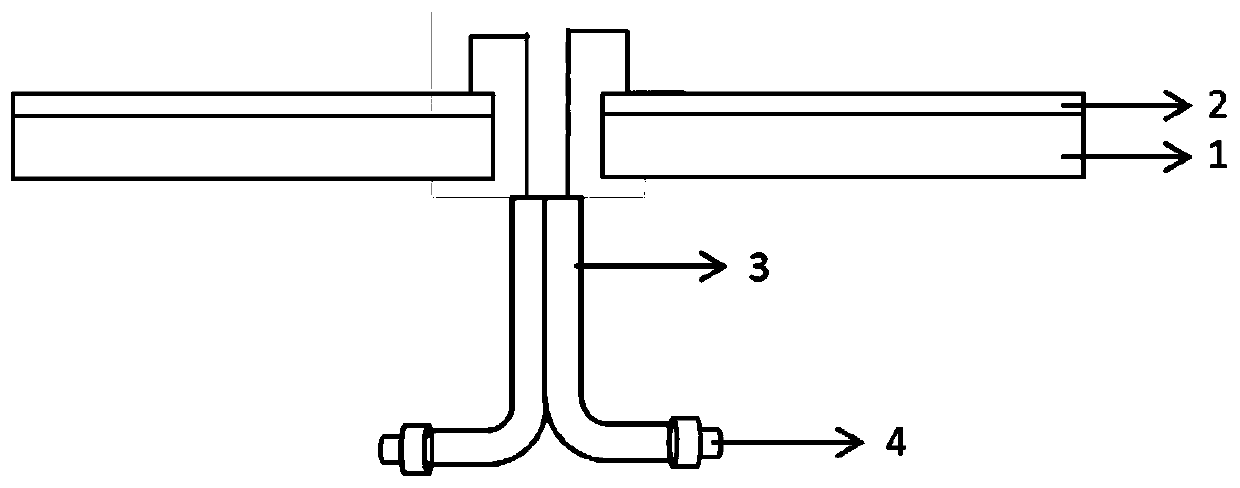

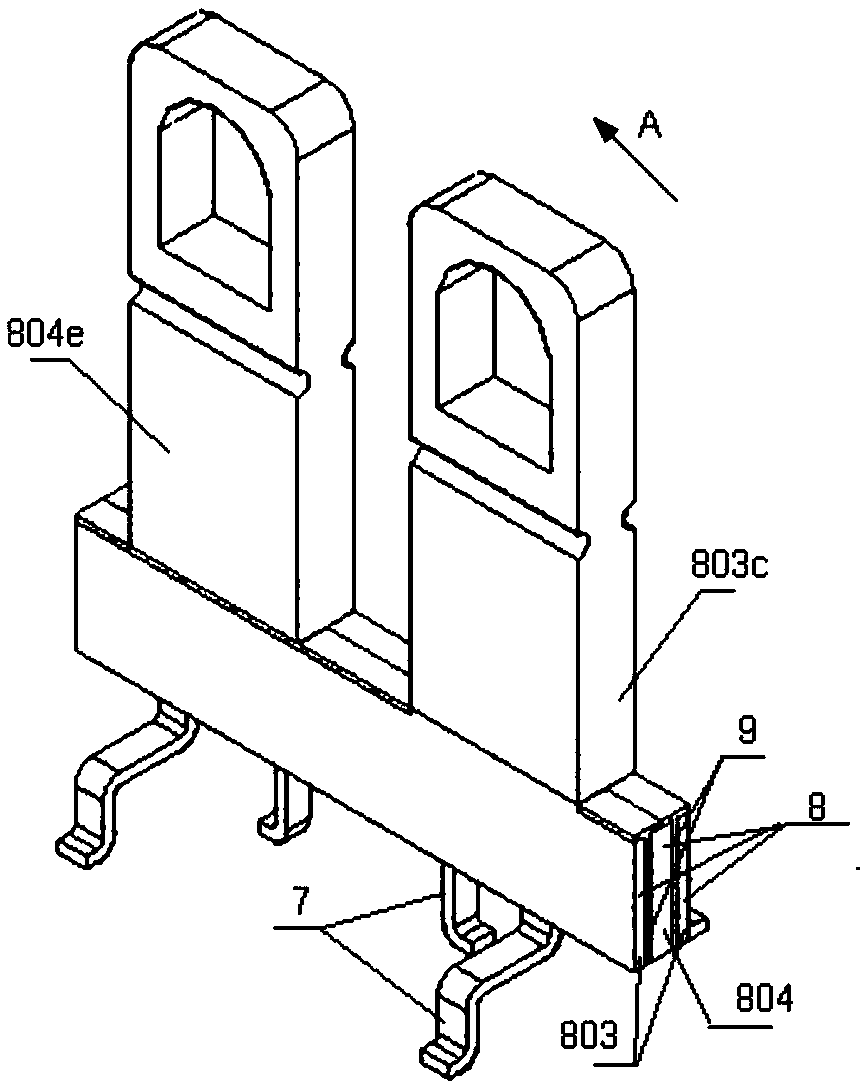

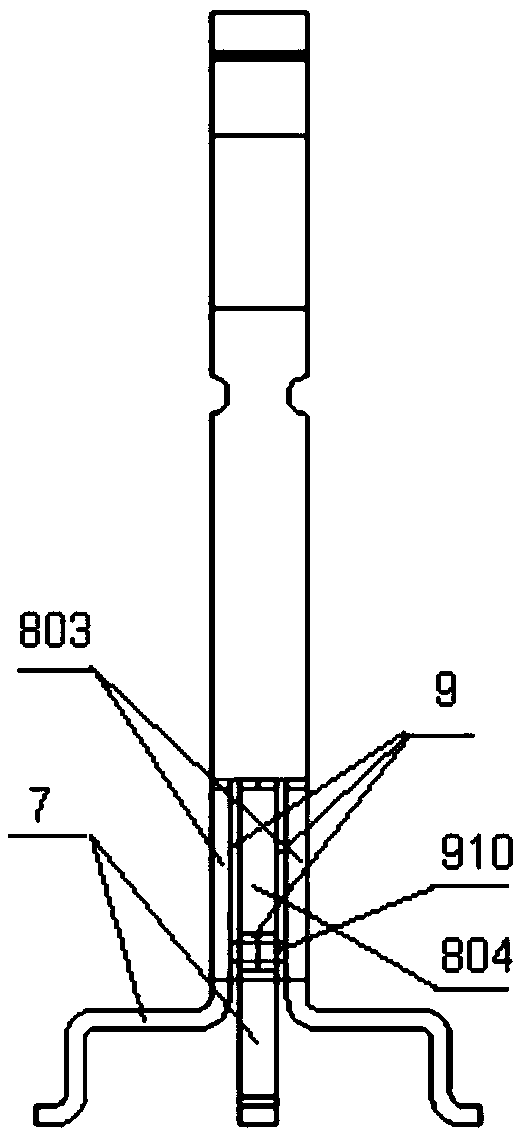

Electrical contact

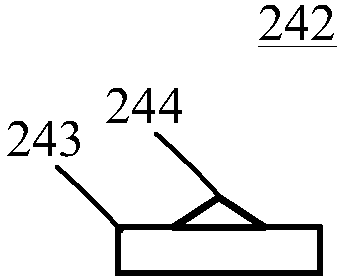

ActiveUS10797424B2Shorten the current pathImprove electrical performanceElectric discharge tubesSecuring/insulating coupling contact membersElectrical connectionEngineering

An electrical contact for connecting a chip module to a print circuit board, the electrical contact comprises a main body, an upper elastic arm and a lower mounting arm extending upwardly from the main body, and a lower elastic arm and a lower mounting arm extending downwardly from the main body. The upper mounting arm is disposed at the downside of the upper elastic arm and forms a space therebetween; the lower mounting arm is disposed at the downside of the lower elastic arm and forms a space therebetween. The upper elastic arm and the lower elastic arm are respectively deformed by the chip module and print circuit board to resist to the upper mounting arm and lower mounting arm, thereby shortening the current path between the chip module and the print circuit board for improving the high frequency performance of an electrical connector.

Owner:FUDING PRECISION COMPONENTS SHENZHEN +1

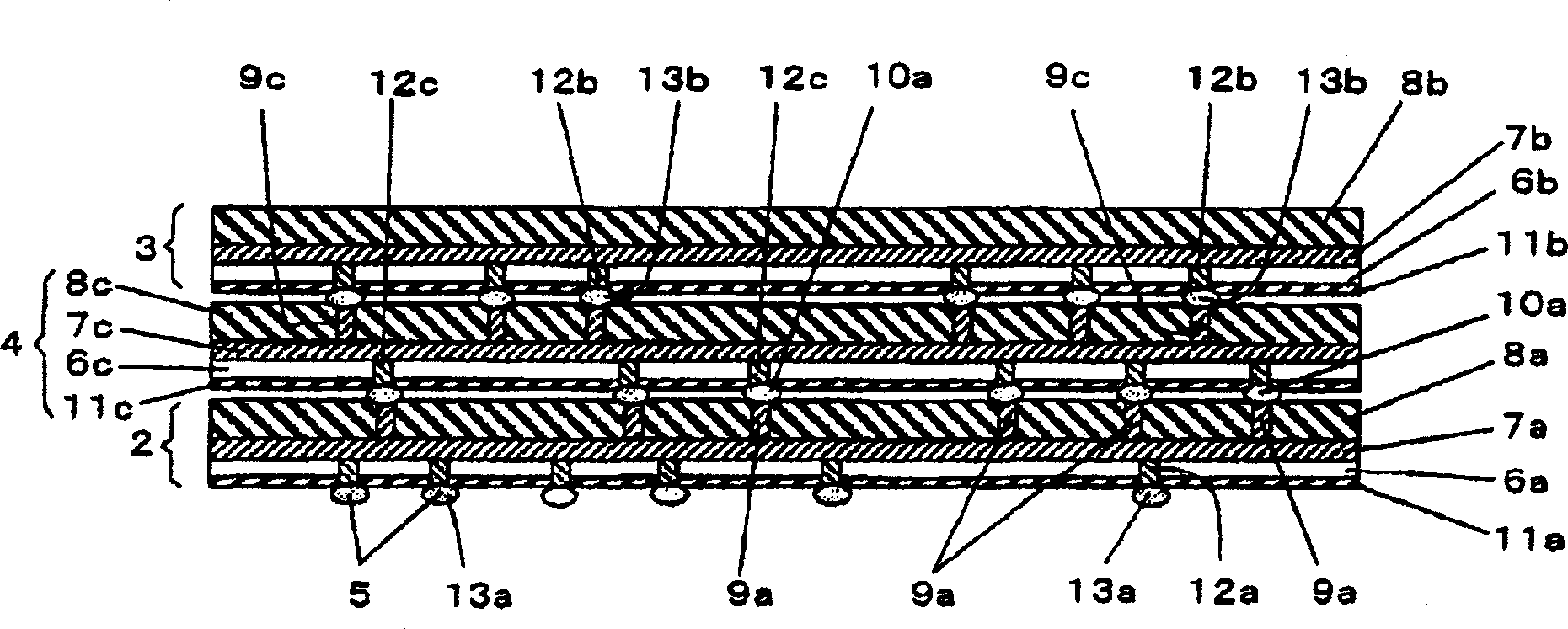

Semiconductor device and process for fabricating the same

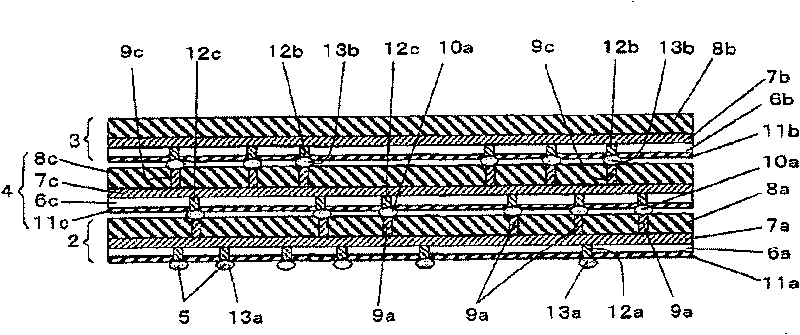

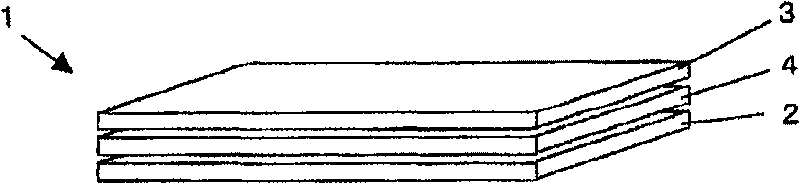

ActiveCN1875481AAchieve thinningExcellent electrical propertiesSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

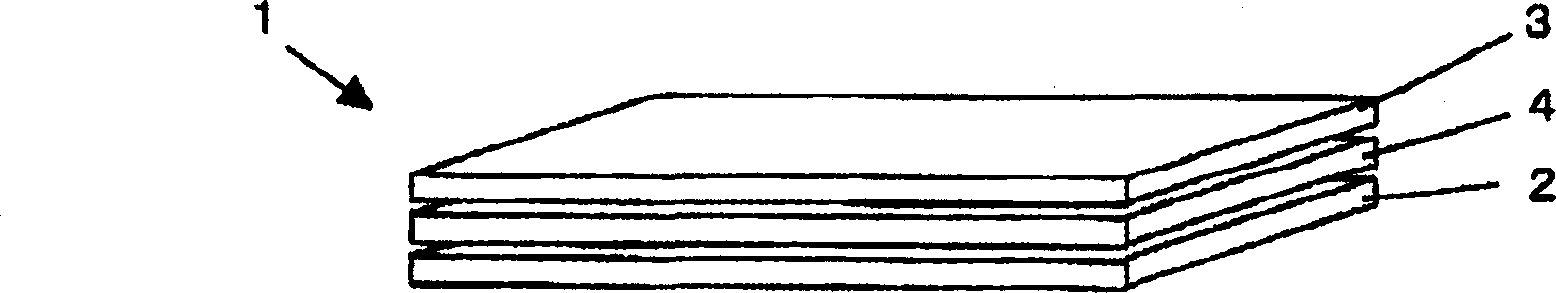

A thin stacked semiconductor device suitable for high speed operation. A plurality of specified circuits are formed on one surface of a semiconductor substrate while being arranged, and wiring and insulating layers being connected electrically with the circuits are laminated and formed sequentially in a specified pattern to form a multilayer wiring part. At the stage for forming the multilayer wiring part, a filling electrode is formed on the semiconductor substrate such that the surface is covered with an insulating film, a post electrode is formed on specified wiring at the multilayer wiring part, a first insulating layer is formed on one surface of the semiconductor substrate, the surface of the first insulating layer is removed by a specified thickness to expose the post electrode, the other surface of the semiconductor substrate is ground to expose the filling electrode and to form a through-type electrode, forward end of the through-type electrode is projected by etching one surface of the semiconductor substrate, a second insulating layer is formed on one surface of the semiconductor substrate while exposing the forward end of the through-type electrode, bump electrodes are formed on both electrodes and then the semiconductor substrate is divided to form a semiconductor device. A plurality of semiconductor devices thus obtained are stacked and secured at the bump electrodes thus manufacturing a stacked semiconductor device.

Owner:阿奇里斯科技公司

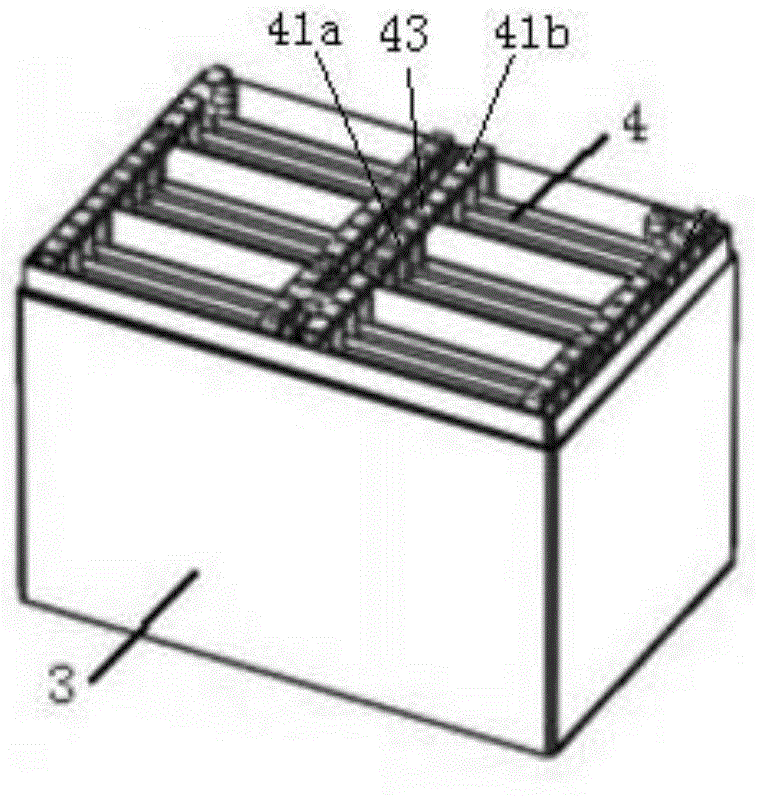

Lead-acid storage battery and electric car using such lead-acid storage battery

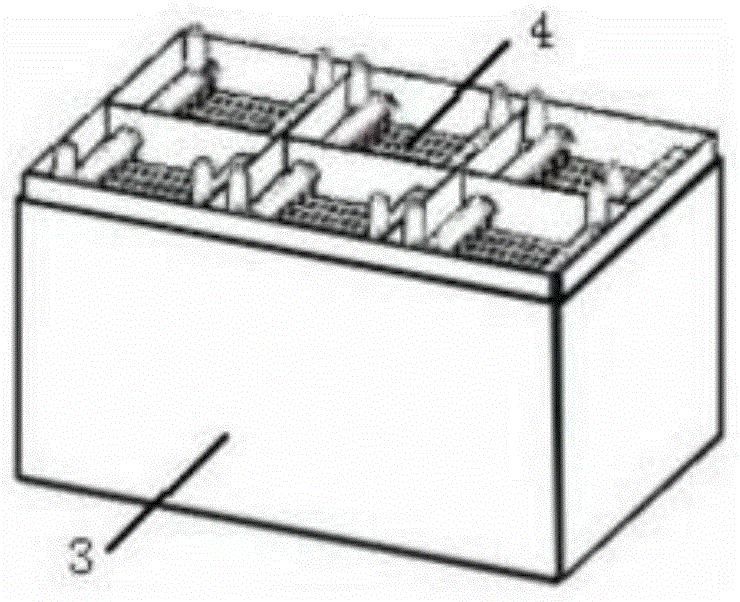

InactiveCN105024036AEasy to wear offQuick wear offFinal product manufactureCell sealing materialsPower flowElectrical battery

The invention discloses a lead-acid storage battery and an electric car using such a lead-acid storage battery, and aims at providing a lead-acid storage battery capable of effectively shortening a current path between bus bars and reducing internal resistance, heat value, and temperature and current collection property fluctuation among single batteries, and an electric car. The lead-acid storage battery comprises a plurality of single batteries arranged side by side, each single battery comprises a single battery jar and a polar group, the polar group is composed of a plurality of positive plates and a plurality of negative plates which are arranged alternatively in a manner of being separated by separators, positive lugs on the positive plates of the same polar group are connected through a positive bus bar, and negative lugs on the negative plates of the same polar group are connected through a negative bus bar; the positive bus bar and the negative bus bar of the single battery are directly connected with the negative bus bar and the positive bus bar in the single battery jar adjacent to the single battery through metal connectors, the single batteries are connected in series, and the positive bus bars, the negative bus bars and the metal connectors are located at the same height.

Owner:CHAOWEI POWER CO LTD

Silicon-germanium heterojunction bipolar transistor

ActiveUS8378457B2Improve breakdown voltageShorten the current pathTransistorSemiconductor/solid-state device manufacturingLateral extensionField oxide

A SiGe HBT formed on a silicon substrate is disclosed. An active area is isolated by field oxide regions; a collector region is formed in the active area and extends into the bottom of the field oxide regions; pseudo buried layers are formed at the bottom of the field oxide regions, wherein each pseudo buried layer is separated by a lateral distance from the active area and connected to a lateral extension part of the collector region; first deep hole contacts are formed on top of the pseudo buried layers in the field oxide regions to pick up collector electrodes; a plurality of second deep hole contacts with a floating structure, are formed in the field oxide region on top of a lateral extension part of the collector region, wherein N-type implantation regions are formed at the bottom of the second deep hole contacts.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

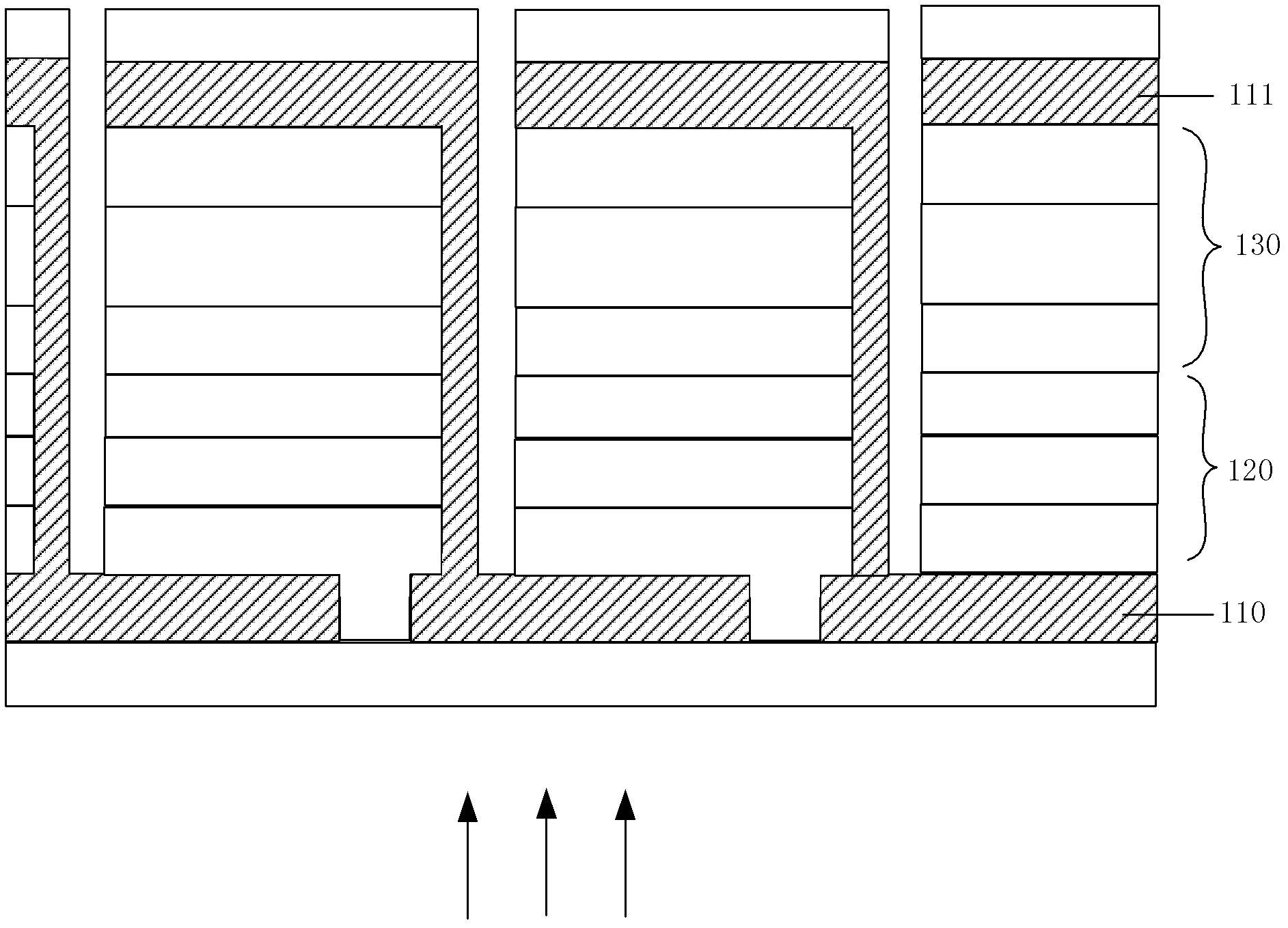

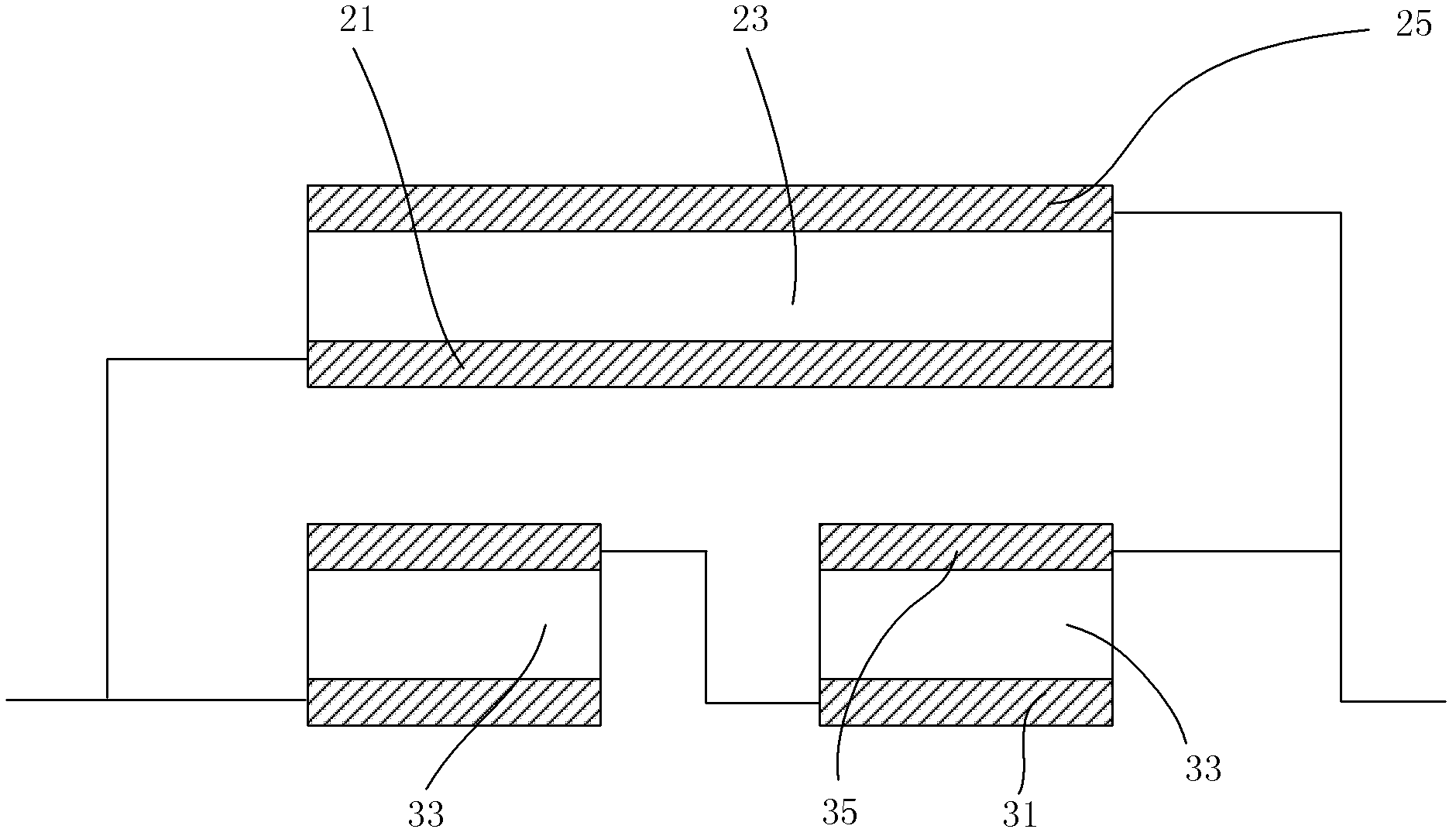

Solar cell and manufacturing method of solar cell

InactiveCN103258889AImprove photoelectric conversion rateReduce consumptionFinal product manufacturePhotovoltaic energy generationPower flowConductive materials

The invention provides a solar cell and a manufacturing method of the solar cell. The solar cell comprises a first solar cell layer, a second solar cell layer and a transparent insulating layer. The first solar cell layer comprises a first solar cell set which is formed by connecting one or more first-type solar cells in series, and the second solar cell layer comprises a second solar cell set which is formed by connecting one or more second-type solar cells in series. The transparent insulating layer is located between the first solar cell layer and the second solar cell layer, through holes or channels are formed in the transparent insulating layer, conductive materials are filled into the through holes or the channels, and then the first solar cell set and the second solar cell set are connected in parallel. The maximum power voltage at two ends of the first solar cell set is equal to the maximum power voltage at two ends of the second solar cell set. The solar cell is a mechanically-stacked multi-section laminated cell, so that current matching is unnecessary among the first-type solar cells and the second-type solar cells, a high photoelectric conversion rate is provided, monolithic integration can be automatically formed in the technological process, the manufacturing method is easy and convenient to use and low in cost.

Owner:DU PONT APOLLO

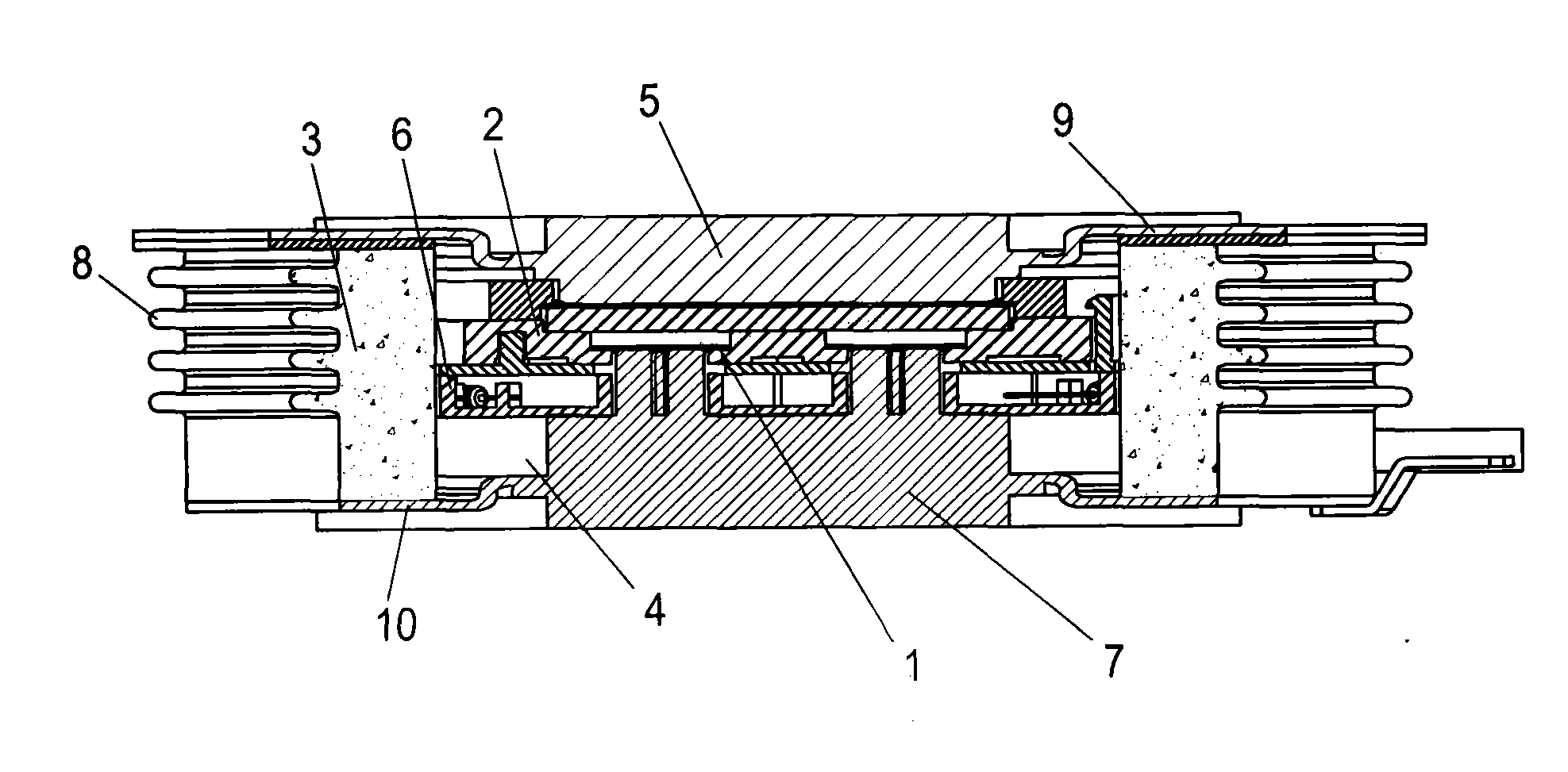

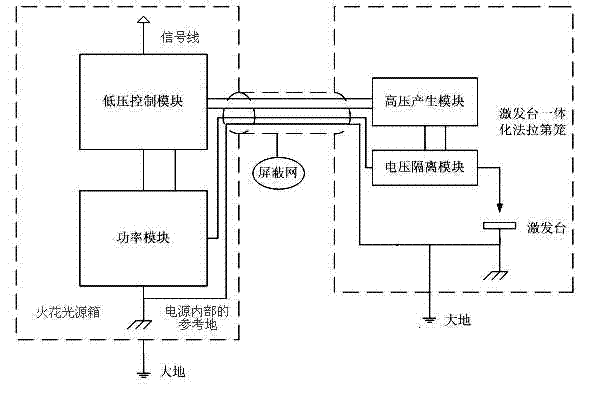

Flat package crimping type extraction electrode insulated gate bipolar transistor element

InactiveCN103681547AShorten the heat conduction pathReduce heat conduction resistanceSemiconductor/solid-state device detailsSolid-state devicesMetallic materialsTransistor

The invention provides a flat package crimping type extraction electrode insulated gate bipolar transistor element. The flat package crimping type extraction electrode insulated gate bipolar transistor element comprises an IGBT chip. The flat package crimping type extraction electrode insulated gate bipolar transistor element further comprises a chip mode carrier and a housing made from ceramic. The housing is provided with a chip installation hole in the vertical direction. The chip mode carrier is provided with a chip clamping groove. The IGBT chip is fixed in the chip clamping groove in the chip mode carrier. The chip mode carrier is fixed in the chip installation hole at the middle portion. An upper extraction electrode plate used as the IGBT emitter is arranged above the chip mode carrier. The upper extraction electrode is made from a metal material. The upper extraction electrode plate is installed in the chip installation hole at the upper portion. The lower end surface of the upper extraction electrode plate is attached to the circuit port of the emitter on the IGBT chip. The objective of the invention is to provide a flat package crimping type extraction electrode insulated gate bipolar transistor element having advantages of small size, compact structure, good heat dissipation performance, long service life, low failure occurrence rate, high reliability and convenient utilization.

Owner:BEIJING XINCHUANG CHUNSHU RECTIFIER

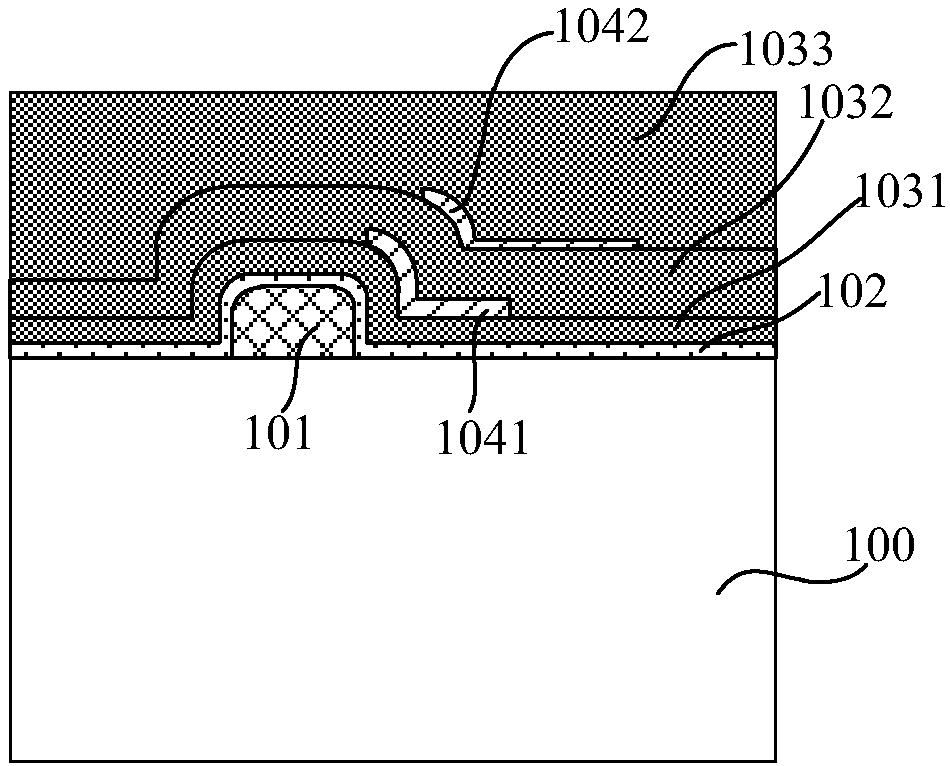

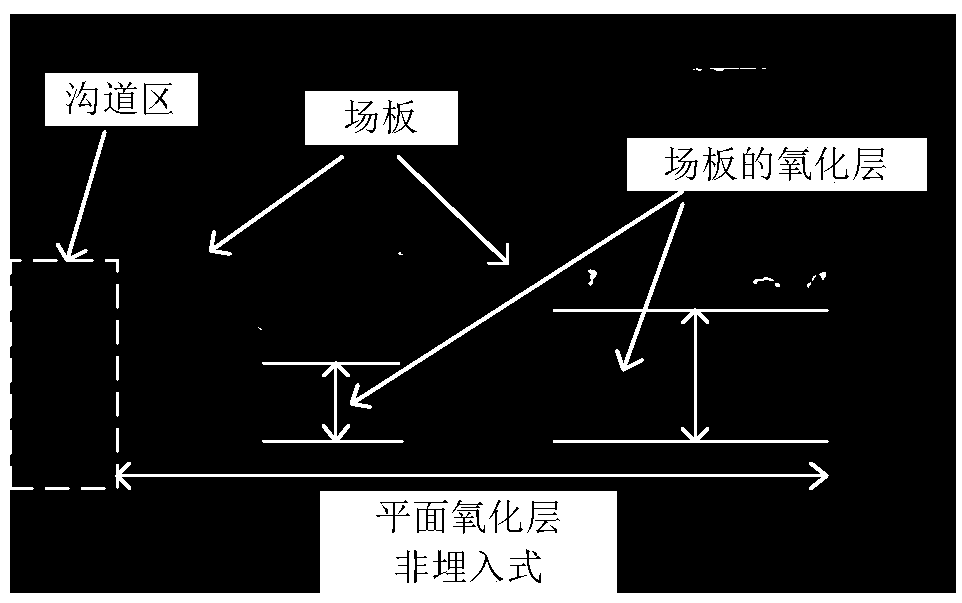

Semiconductor device with separated planar field plate structure and manufacturing method thereof

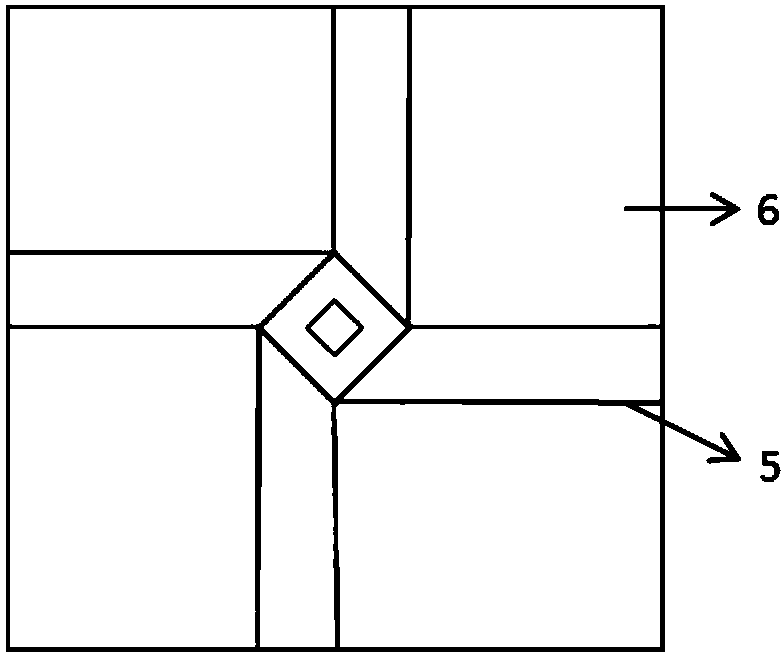

InactiveCN107785428AImprove compatibilityShorten the current pathTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor device modeling

The invention provides a semiconductor device with a separated planar field plate structure and a manufacturing method thereof. The method comprises: step 1, providing a semiconductor substrate, forming a source, a drain and a gate on the semiconductor substrate, and forming a drift region in the semiconductor substrate between the gate and the drain; step 2, forming a first dielectric layer to cover the surface of the semiconductor substrate, the source, the drain and the gate; and step 3, forming a first field plate layer on the first dielectric layer, at least part of the first field platelayer being located above the drift region and close to the gate. According to the manufacturing method, the steps of depositing the dielectric layer and forming the field plate layer are alternatelyperformed to form a separated planar field plate structure comprising one, two or more field plate layers to achieve the advantage of compatibility between process platforms. The formed separated planar field plate structure shortens the current path of the drift region and improves the performance of the device.

Owner:CSMC TECH FAB2 CO LTD

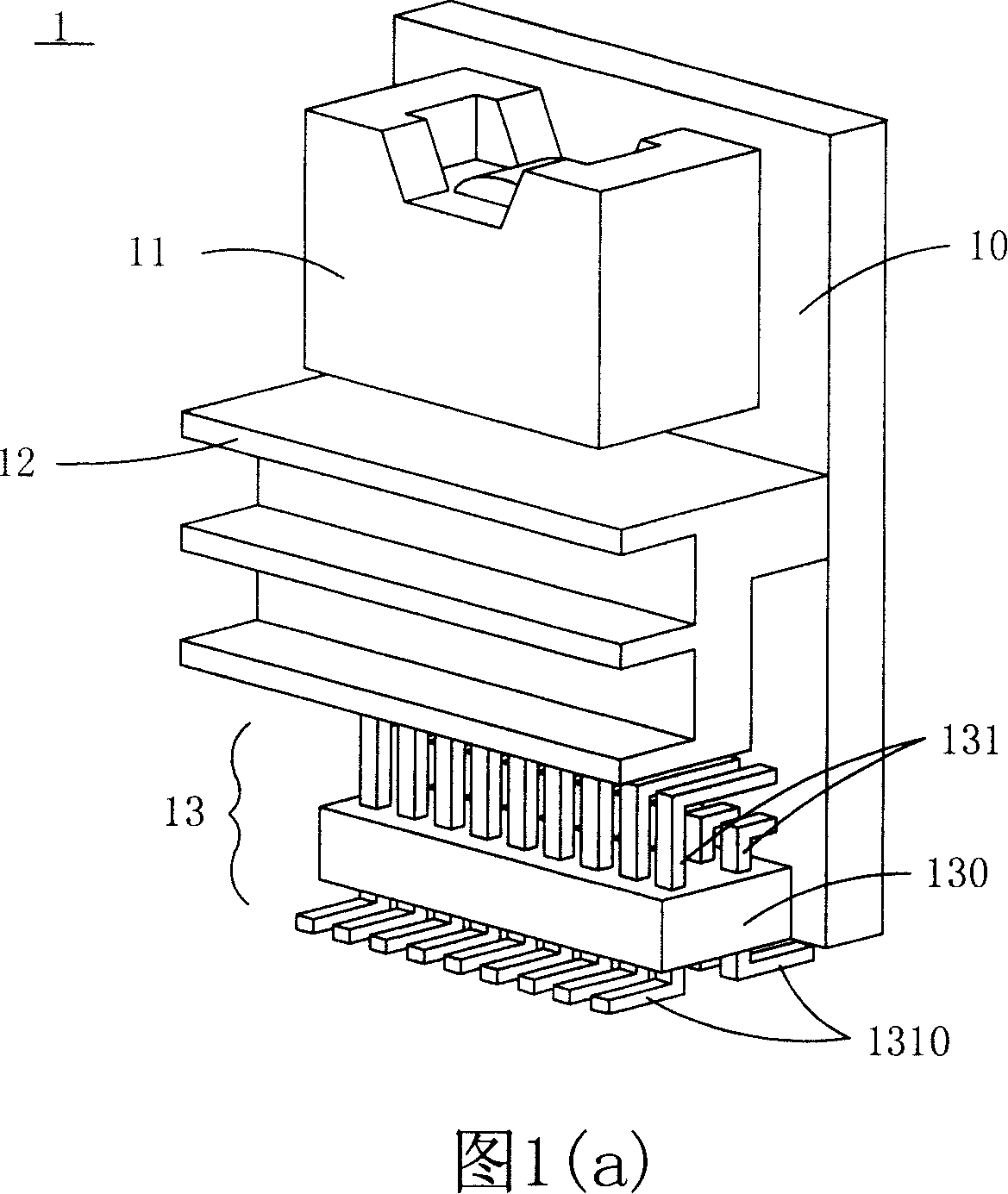

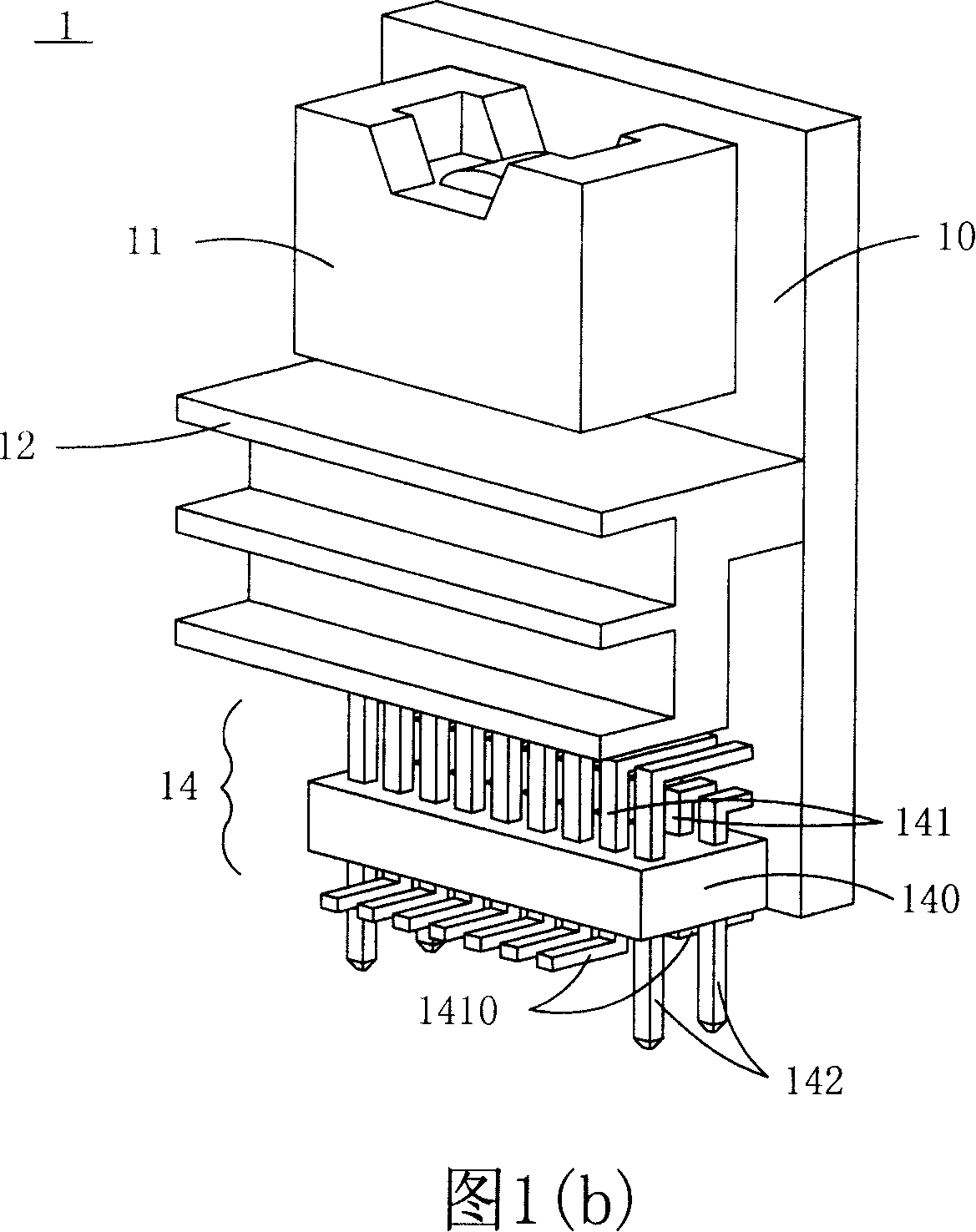

Circuit module and its making method

InactiveCN101123848AReduce energy consumptionLow costPrinted circuit manufactureElectrical componentsEngineeringElectronic component

The invention discloses a circuit module and the manufacture method of the circuit module applied to be connected with a first contact zone of a system circuit board. The circuit module at least includes a printed wiring board and at least one electronic component arranged on the surface of the electronic component. The printed wiring board is provided with a base board and a circuit pattern; wherein, the base board is provided with at least a surface and a plurality of sides. The circuit pattern is formed on the base board and at least one side of the base board is also provided with a plurality of second contact zones. The a plurality of second contact zones are connected with the circuit pattern and corresponding to the first contact zone of the system circuit board. The invention omits the using of a connector and is contacted with a welding cushion on the system circuit board by the edge of the printed wiring board and thus the invention can save cost and shorten the circuit route thereby reducing the energy consumption of power transmission. Besides, the manufacture mode of the edge jointing zone of the printed wiring board is accomplished by making use of the widely-known plated through hole technique and cutting technique. The method is very easy and can save manufacture time.

Owner:DELTA ELECTRONICS INC

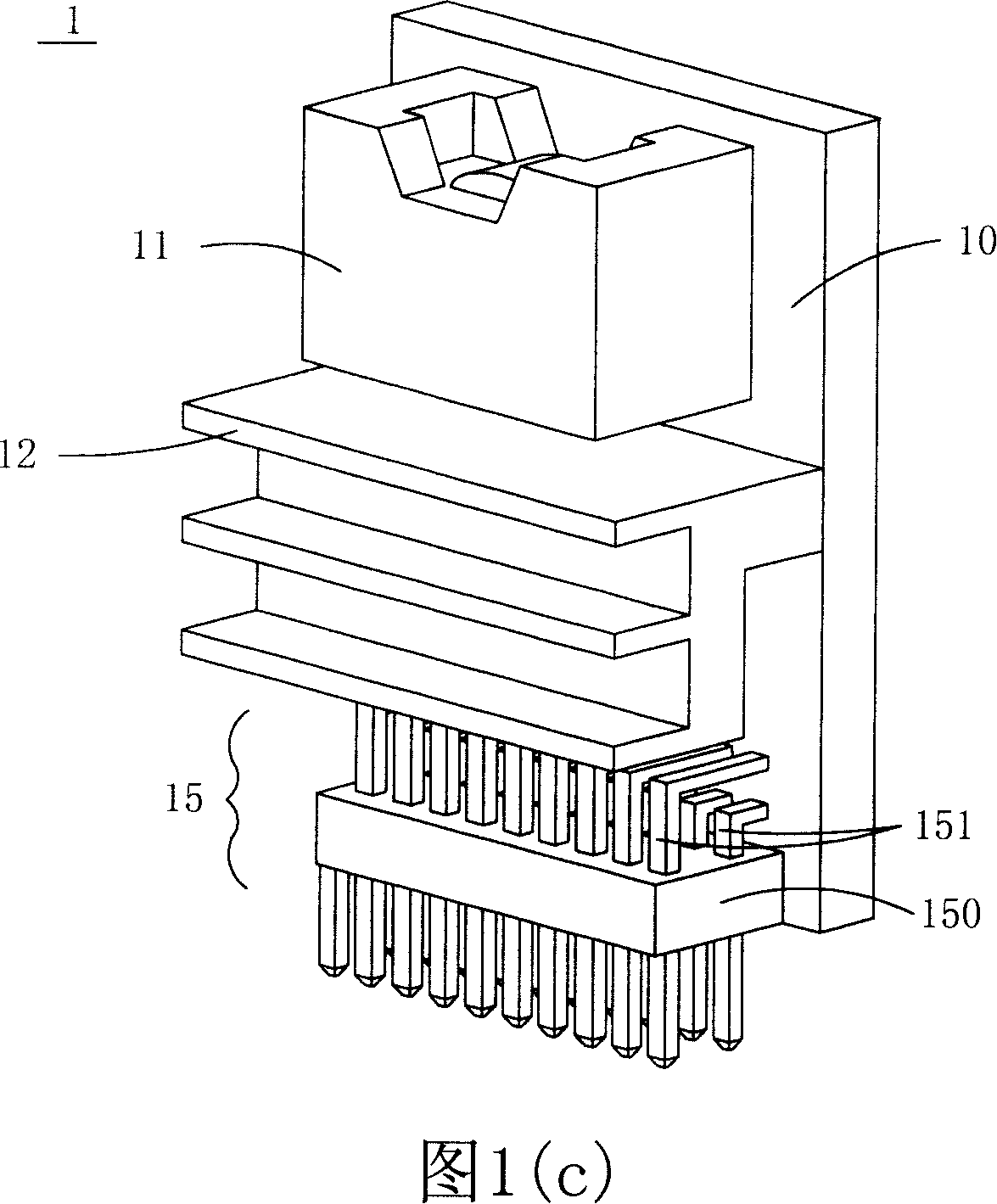

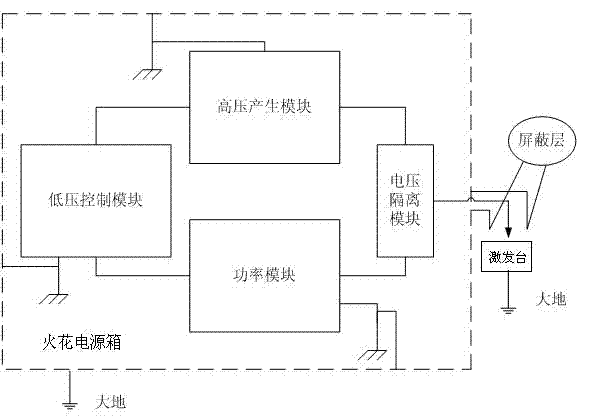

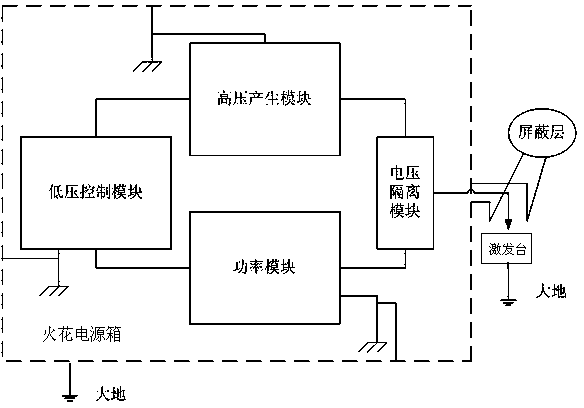

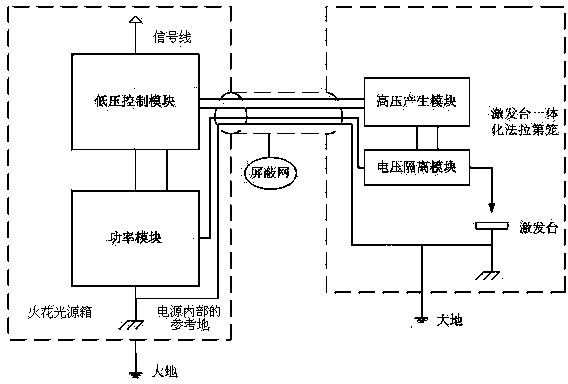

Electromagnetic compatibility device for spark light source of photoelectric direct-reading spectrometer

ActiveCN102853911AShorten the current pathReduce the amplitude of electromagnetic interferenceRadiation pyrometrySpectrometry/spectrophotometry/monochromatorsDirect readingElectromagnetic interference

The invention discloses an electromagnetic compatibility device for a spark light source of a photoelectric direct-reading spectrometer.The electromagnetic compatibility device comprises a low voltage controlling module, a high voltage generating module, a power module and a voltage isolating module; both the low voltage controlling module and the power module are arranged in a spark light source box; both the high voltage generating module and the voltage isolating module are arranged in a Faraday cage; the Faraday cage is integrated with an exciting platform; a connecting wire for the low voltage controlling module and the high pressure generating module between the Faraday cage and the spark light source box and a connecting wire for the voltage isolating module and the power module are arranged in a shielding mechanism; the exciting platform is connected with the power module through a return cable; the spark light source box and the return cable are grounded; the power module, the low voltage controlling module, the high voltage generating module and the exciting platform are connected with a reference ground in a power supply. According to the electromagnetic compatibility device for a spark light source of a photoelectric direct-reading spectrometer, a current path of a high voltage loop is reduced and electromagnetic interference amplitude is reduced, thereby foundationally solving electromagnetic interference.

Owner:昆山书豪仪器科技有限公司 +1

Antenna and miniaturization method thereof

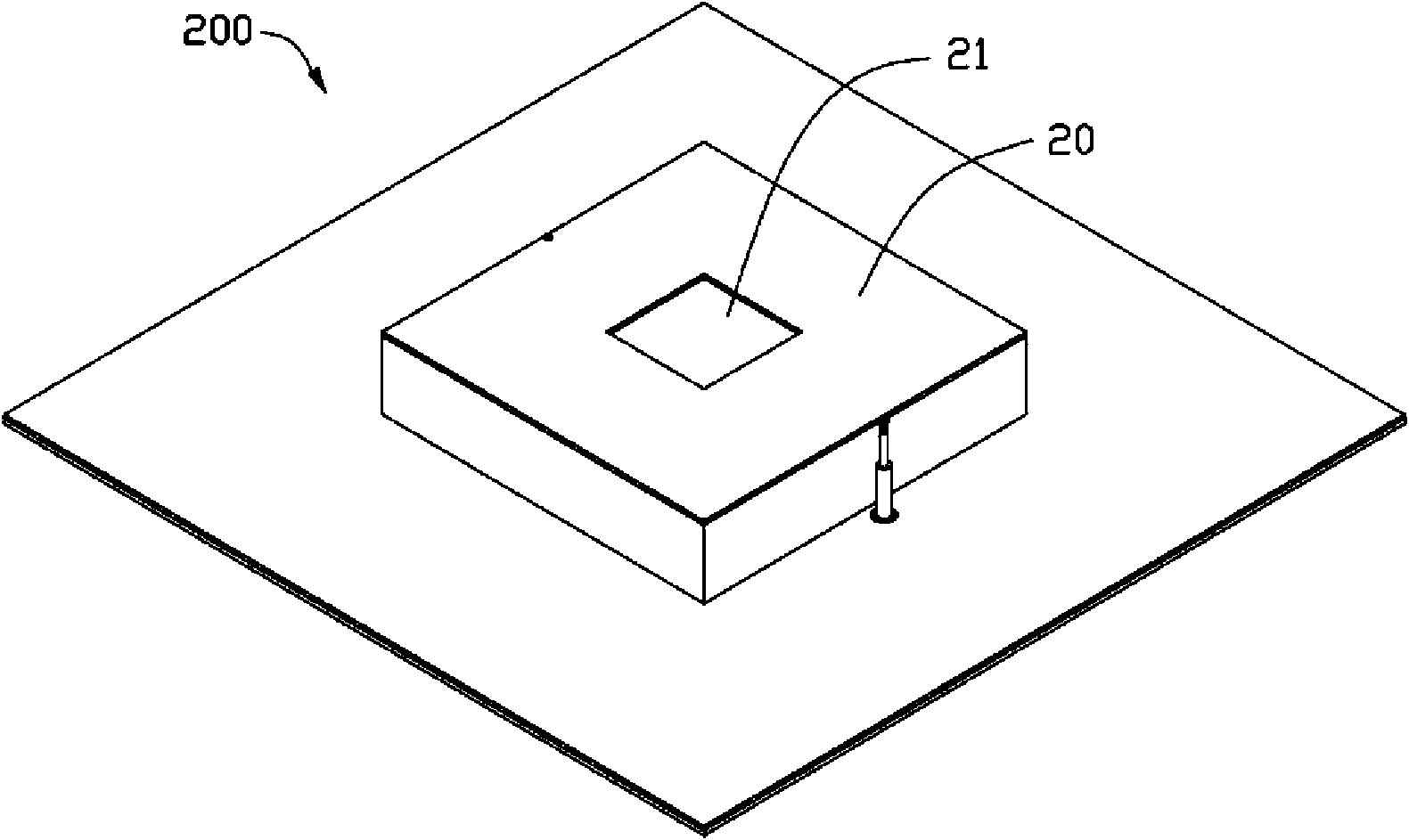

InactiveCN102104190AShorten the current pathExtended current pathRadiating elements structural formsSubstantially flat resonant elementsIncrease sizeIncreased sizes

The invention relates to a miniaturization method of an antenna. The antenna comprises a radiating body. The miniaturization method of the antenna comprises the following steps: decreasing the size of the radiating body of the antenna to shorten a current path of the antenna; setting up a through hole on the radiating body to increase the current path of the antenna, wherein the shortened size for the current path of the antenna is same as the increased size for the current path of the antenna; and forming an miniaturized antenna. By using the miniaturization method of the antenna, the volume of the antenna can be reduced under the condition of keeping the current path of the antenna unchanged, thus the miniaturized antenna can keep frequency unchanged. The invention also relates to an antenna with smaller volume.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

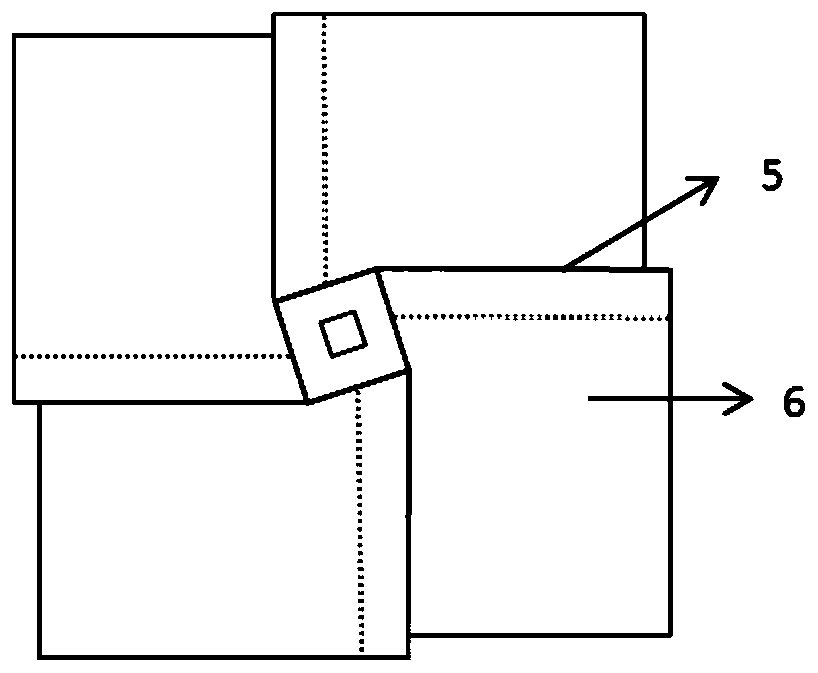

Cross-band frequency-conversion antenna based on intelligent paper folding structure

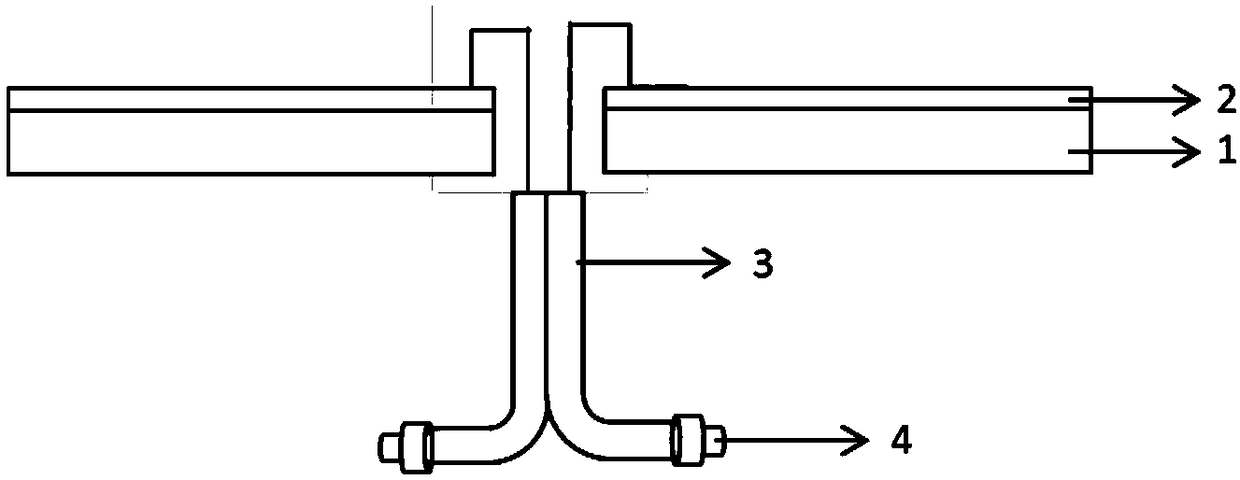

ActiveCN108461906AShorten the current pathThe electrical length of the antenna is smallRadiating elements structural formsAntennas earthing switches associationRadio frequencyWave band

The present invention relates to a cross-band frequency-conversion antenna based on an intelligent paper folding structure, belonging to the field of frequency reconfigurable antennas. The antenna comprises a substrate, an antenna arms, a coaxial feeder, a radio frequency coaxial connector and a RF signal emitter; the substrate employs a self-locking square-twist folding structure; the middle portion of the substrate is provided with a cross-line hole, the two antenna arms are symmetrically glued and fixed at the upper side plate surface of the substrate, the initiating terminal of each antenna arm is extended outwards from the cross-line hole, each antenna arm is located the panel overlapping position for ducking in a folding state; the initiating terminals of the antenna arms are respectively connected with two output ports of the RF signal emitter through the coaxial feeder via the radio frequency coaxial connector, and output signal phase difference of two ends of the RF signal emitter is 180 degrees. The antenna can be subjected to self unfolding through heating to change working frequency, the influence of frequency modulation on performances of the antenna is little, the frequency tuning amplitude is large, and cross of different wave bands can be achieved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

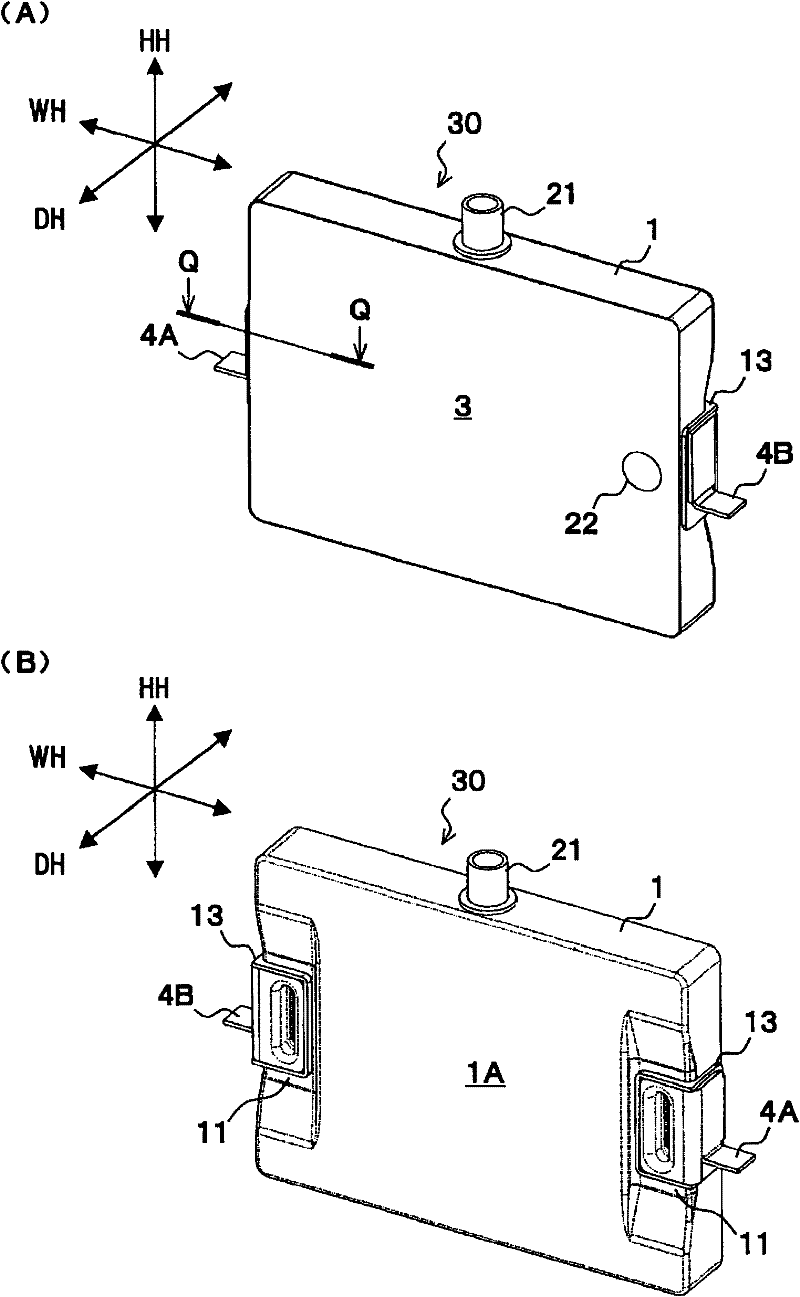

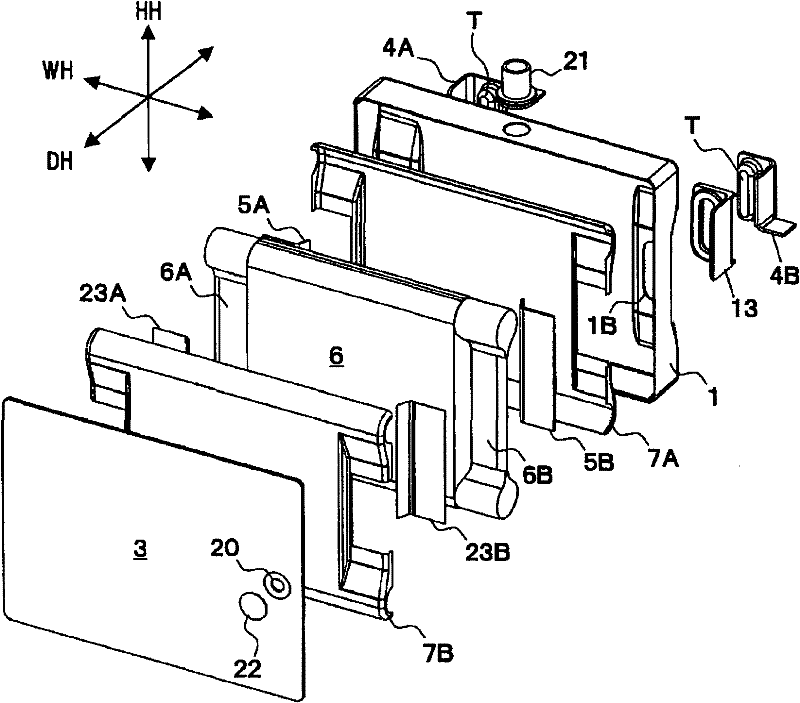

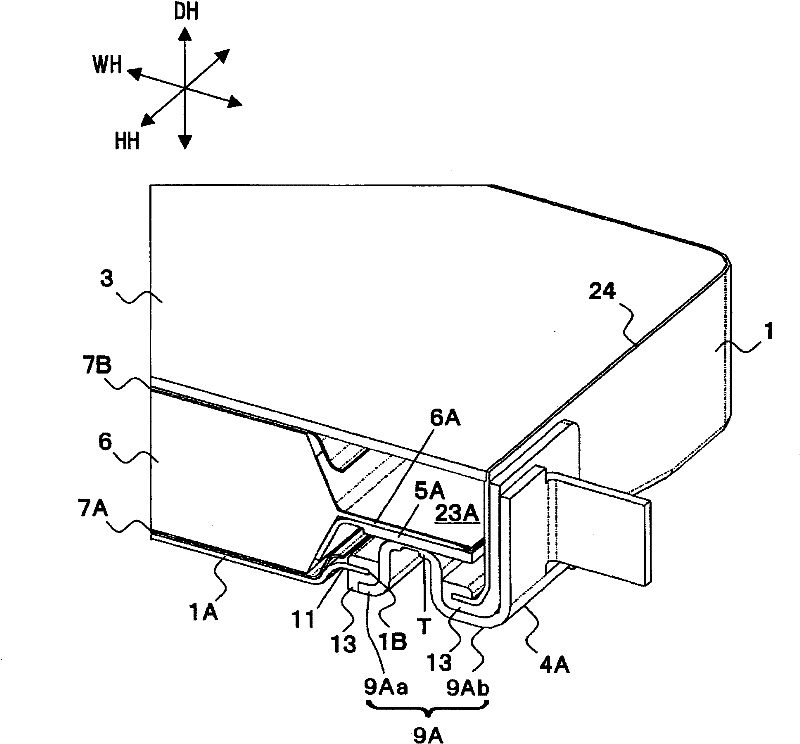

Secondary battery and manufacturing method therefor

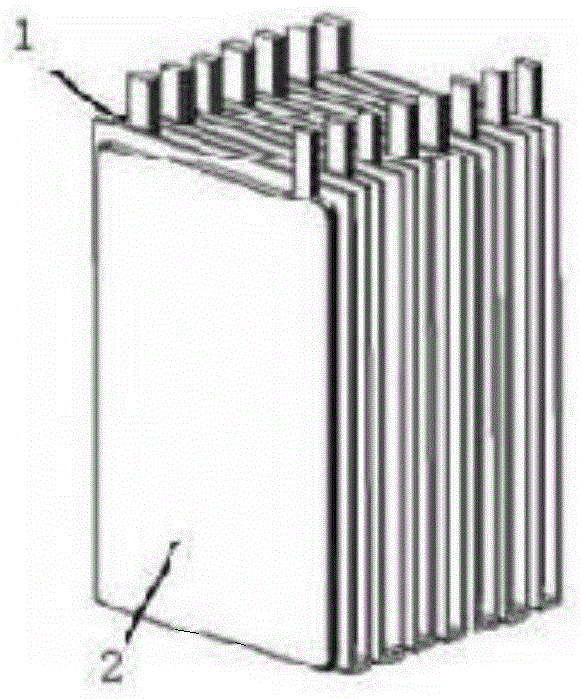

InactiveCN102197514AMiniaturizationShorten the current pathFinal product manufactureSmall-sized cells cases/jacketsLithiumElectricity

Disclosed is a lithium ion secondary battery provided with a battery can (1) and a battery lid (3) for sealing an opening of the battery can (1). A power generating element group (6) comprising wound positive and negative electrode plates is arranged in a space defined by the battery can (1) and the battery lid (3). The battery can (1) is formed into a rectangular parallelepiped shape with a bottom having a shallow form in which the length of one of the two perpendicular sides of the four sides forming the outer periphery of the opening is shorter than the other side. In the power generating element group (6), uncoated members (6A, 6B) of an active material mixture of the positive and negative electrode plates are exposed on mutually opposite sides. The power generating element group (6) is arranged so that the uncoated members (6A, 6B) are positioned directly above a through-hole (1B). Connecting members (9A, 9B) are connected to the uncoated members (6A, 6B) and conduct electricity to outside of the battery through the through-hole (1B).

Owner:HITACHI VEHICLE ENERGY

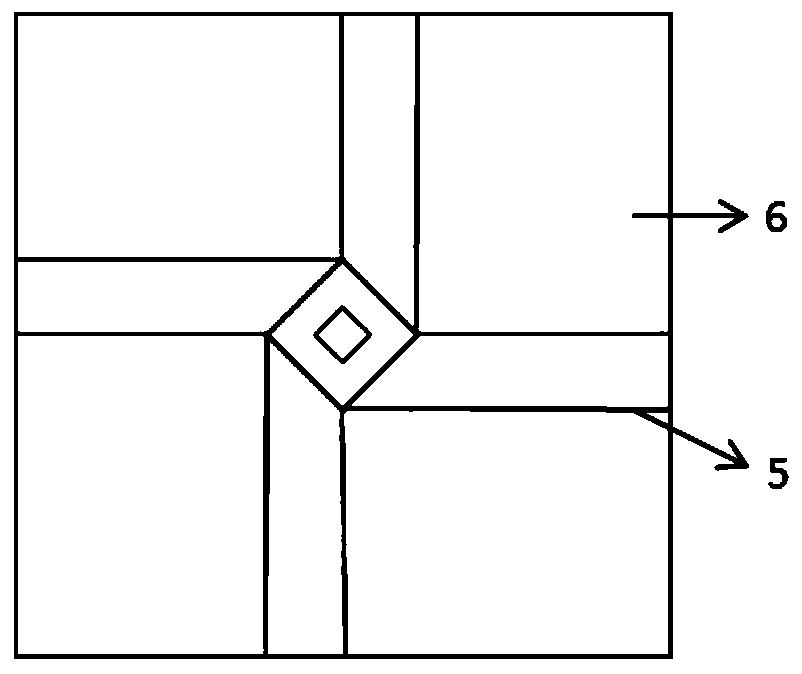

Integrated circuit, integrated circuit test socket with signal and power integration module

InactiveCN109298208ATest results are stableShorten the current pathElectronic circuit testingMeasurement instrument housingComputer moduleEngineering

The invention discloses an integrated circuit and an integrated circuit test socket with signal and power integration module, comprising a first conductive rubber layer, a second conductive rubber layer, a conductor module and a signal and power integration module. The second conductive rubber layer is opposite to the first conductive rubber layer. The conductor module comprises at least a pair ofconductors. The signal and power integration module is disposed between the first conductive rubber layer and the second conductive rubber layer. At least one pair of conductors respectively penetrate through the first and the second conductive rubber layer, an electrically contact with the signal and power integration module.

Owner:CHUNGHWA PRECISION TEST TECH

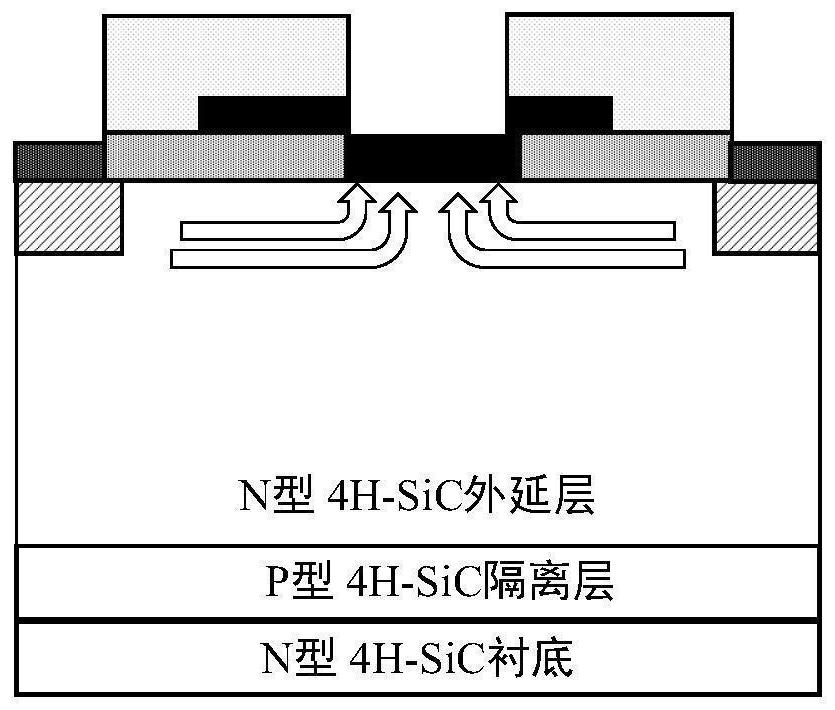

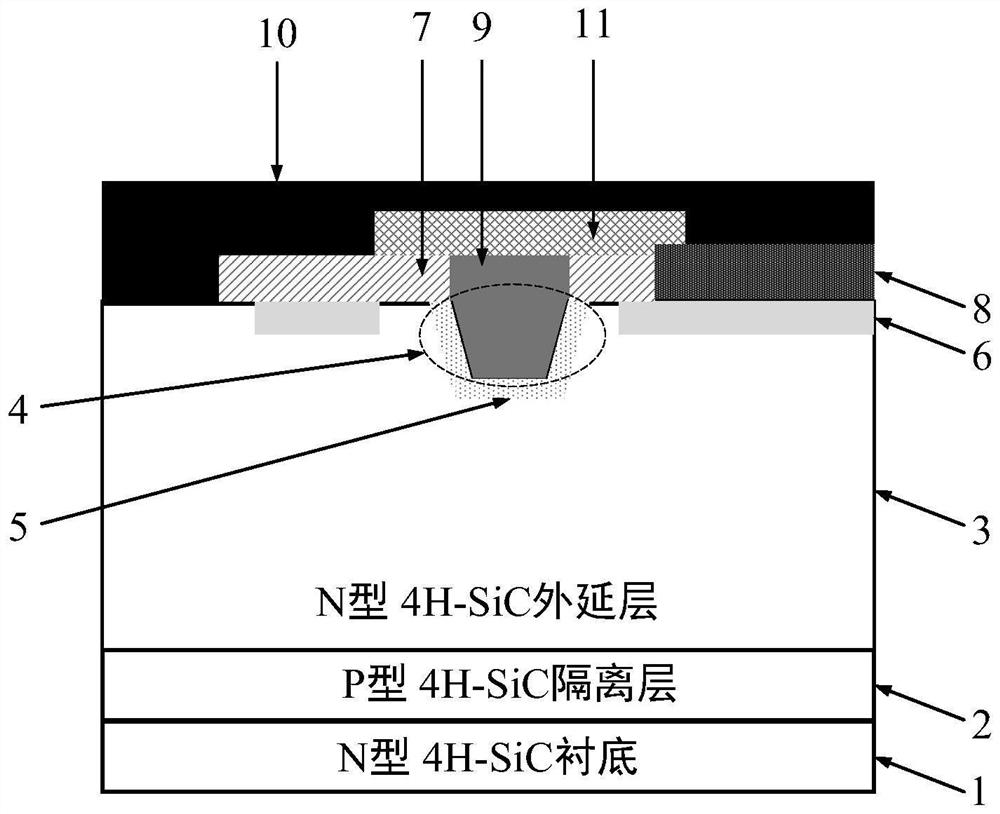

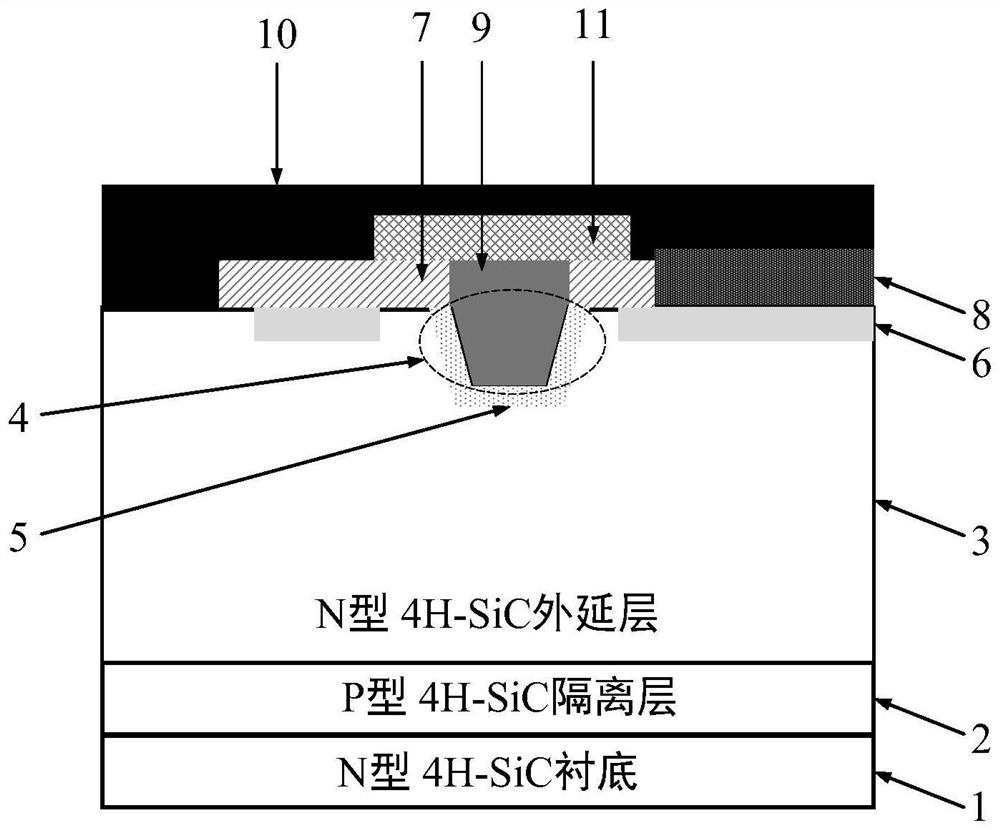

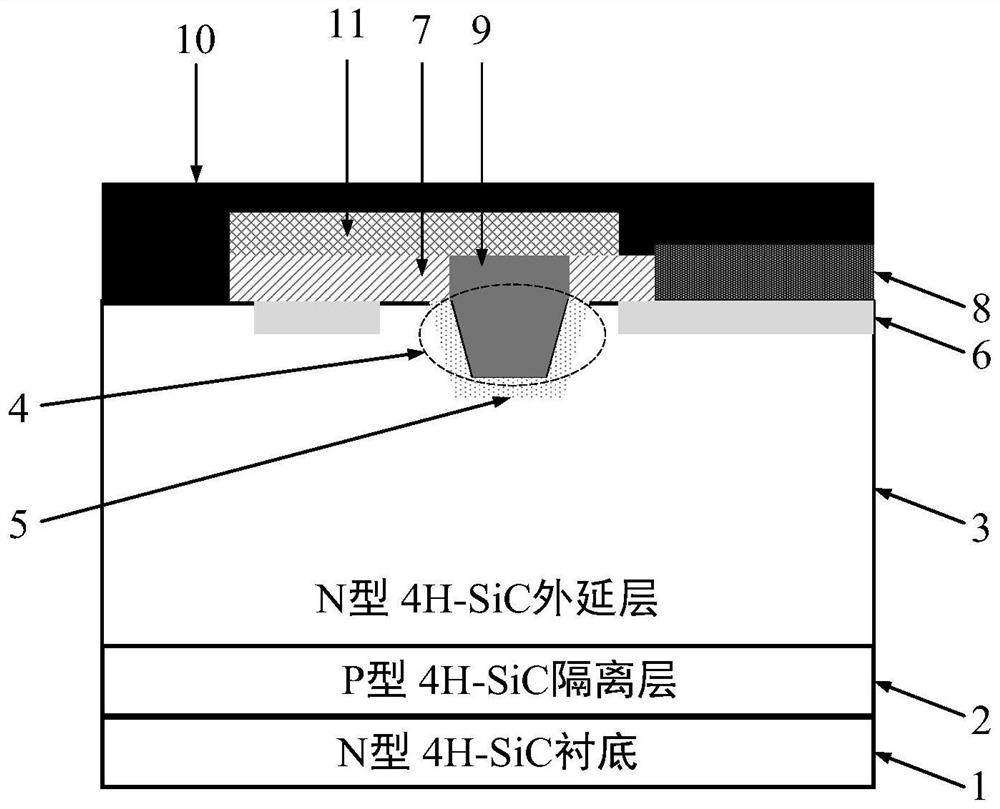

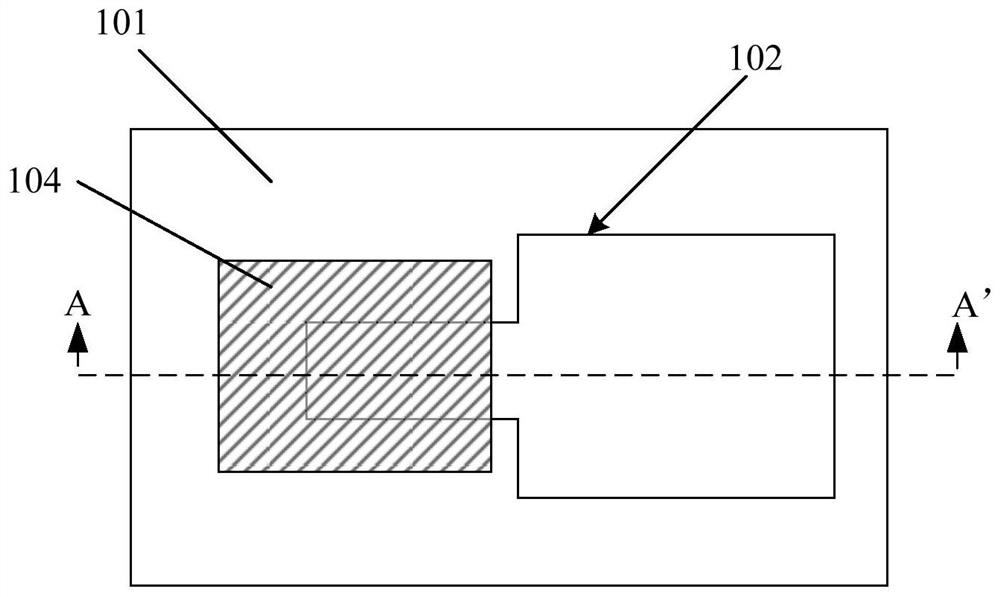

SiC Schottky power diode and production method thereof

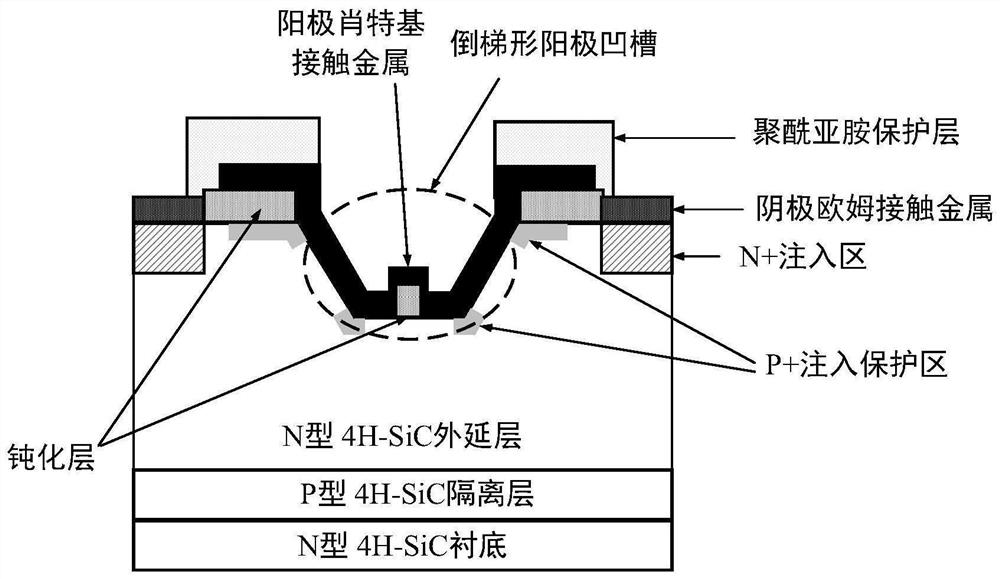

PendingCN113964208AReduce surface leakage currentImprove reverse characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactPower diode

The invention discloses a SiC Schottky power diode. The SiC Schottky power diode comprises an N-type 4H-SiC substrate, a P-type 4H-SiC isolation layer and an N-type 4H-SiC epitaxial layer from bottom to top, and the thickness of the epitaxial layer is less than 6 microns; cathode ohmic contact metal is included and positioned on two sides of the upper surface of the epitaxial layer, and an N + injection region is arranged on the epitaxial layer below the cathode ohmic contact metal; an inverted trapezoidal anode groove is included and p + injection protection regions are arranged on the epitaxial layer around the four inner corners of the inverted trapezoidal anode groove; a passivation layer is included, the first part of the passivation layer is deposited on the upper surface, which is not etched and not covered by the cathode ohmic contact metal, of the epitaxial layer, and the second part of the passivation layer is deposited in the middle of the bottom of the inverted trapezoidal anode groove; and the inverted trapezoidal anode groove, the first portion of the passivation layer, and the second portion of the passivation layer cover the anode Schottky contact metal. According to the invention, the productization of the 4H-SiC Schottky power diode with the high voltage of more than 3000V is realized.

Owner:瑶芯微电子科技(上海)有限公司

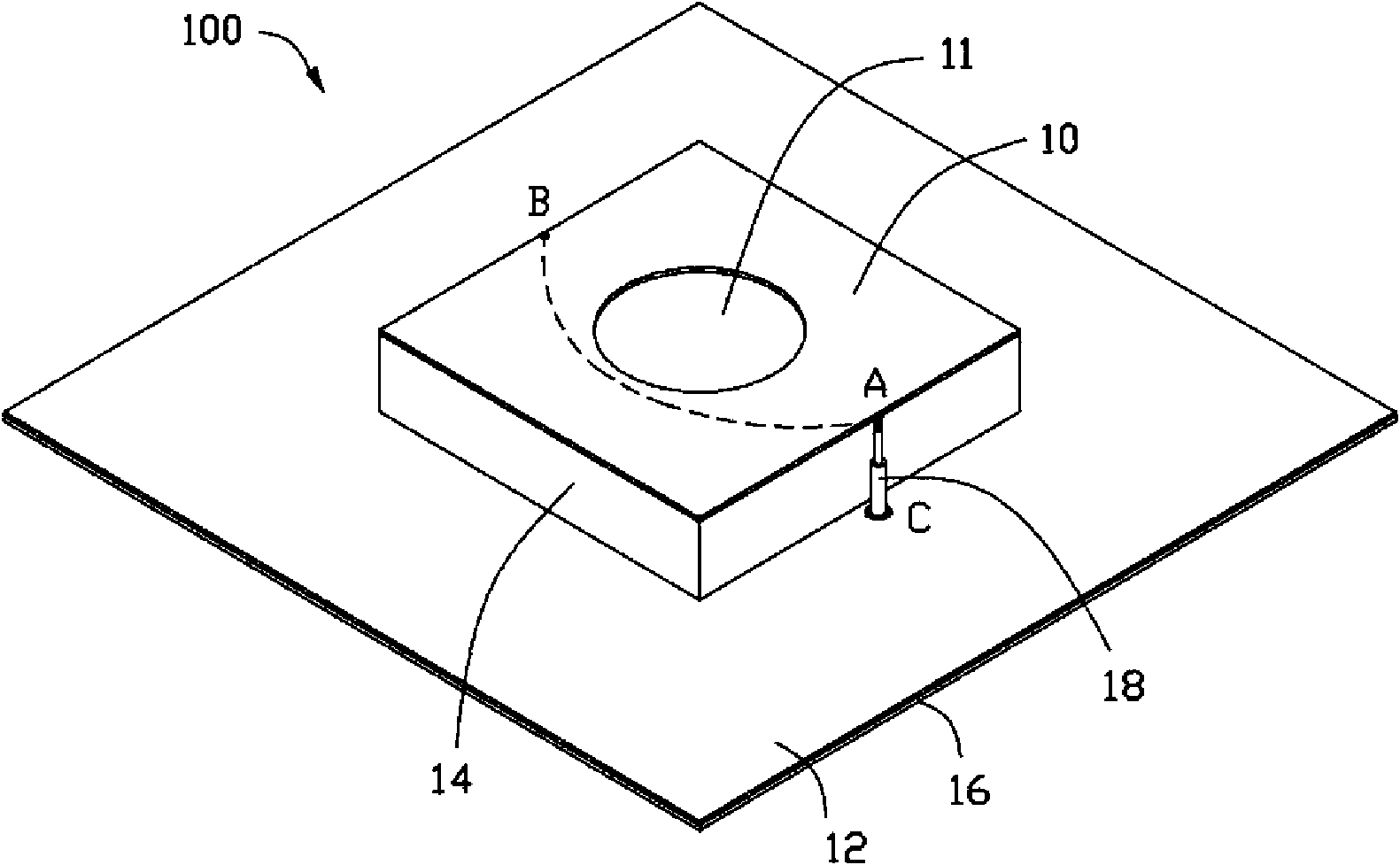

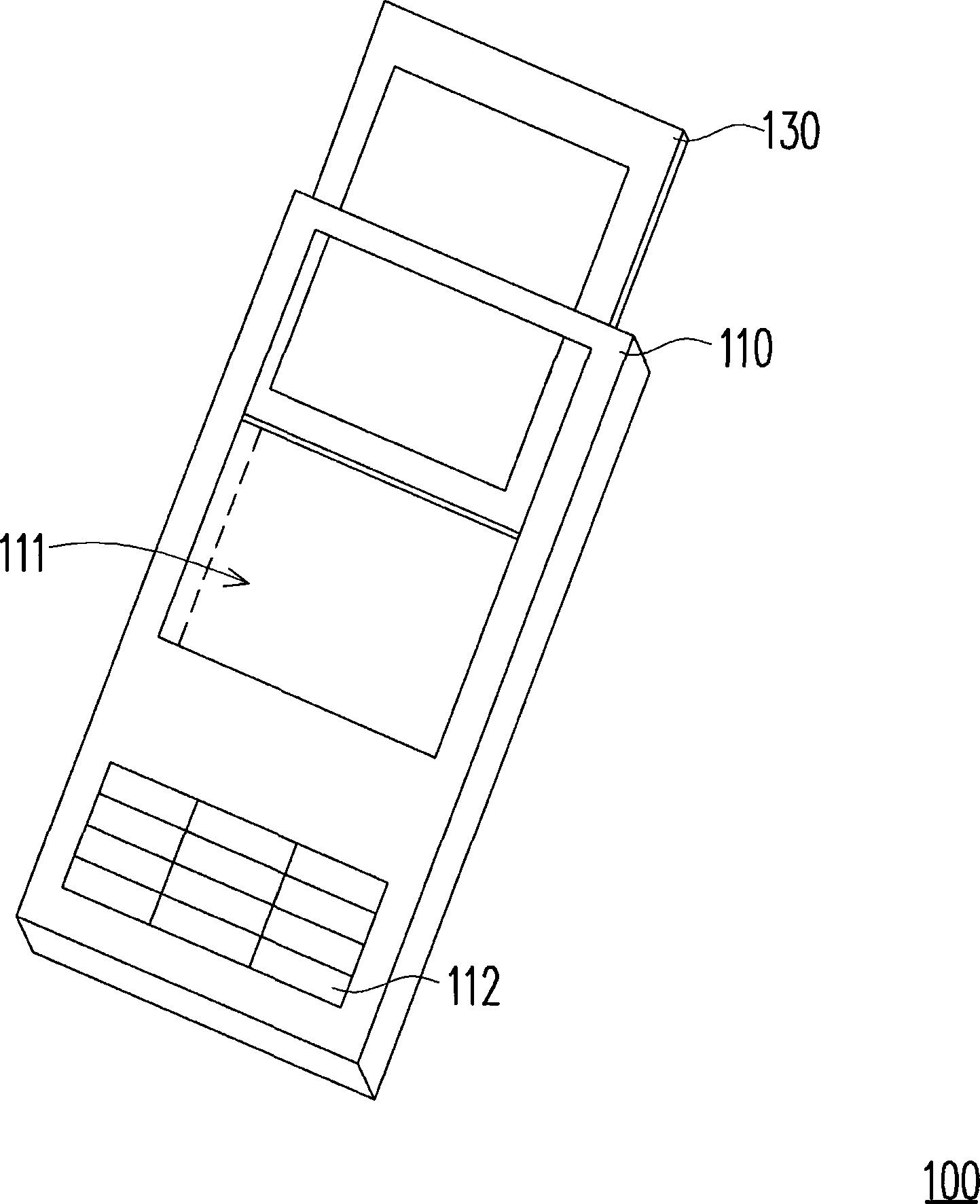

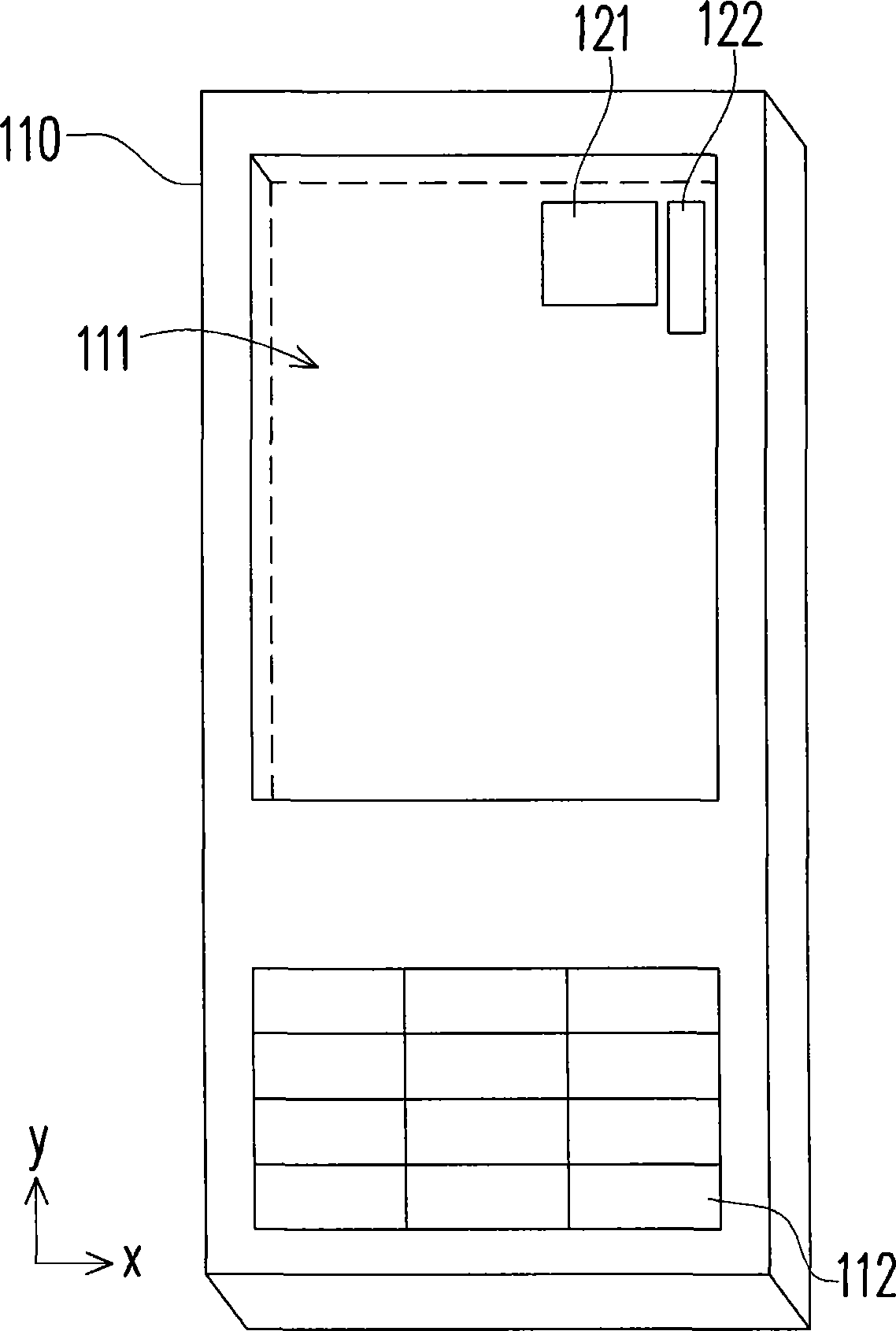

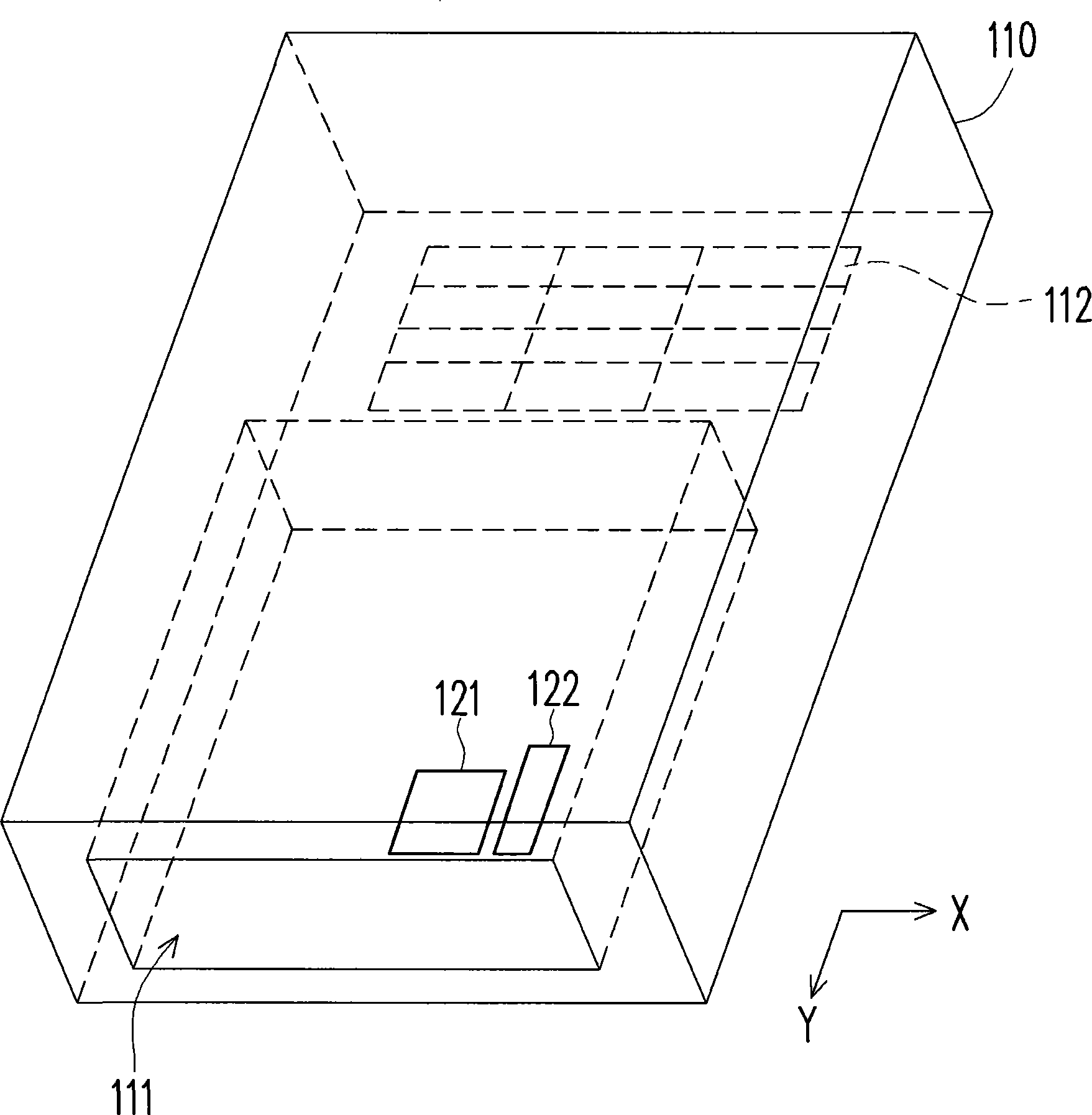

Assembly structure and electronic device having the same

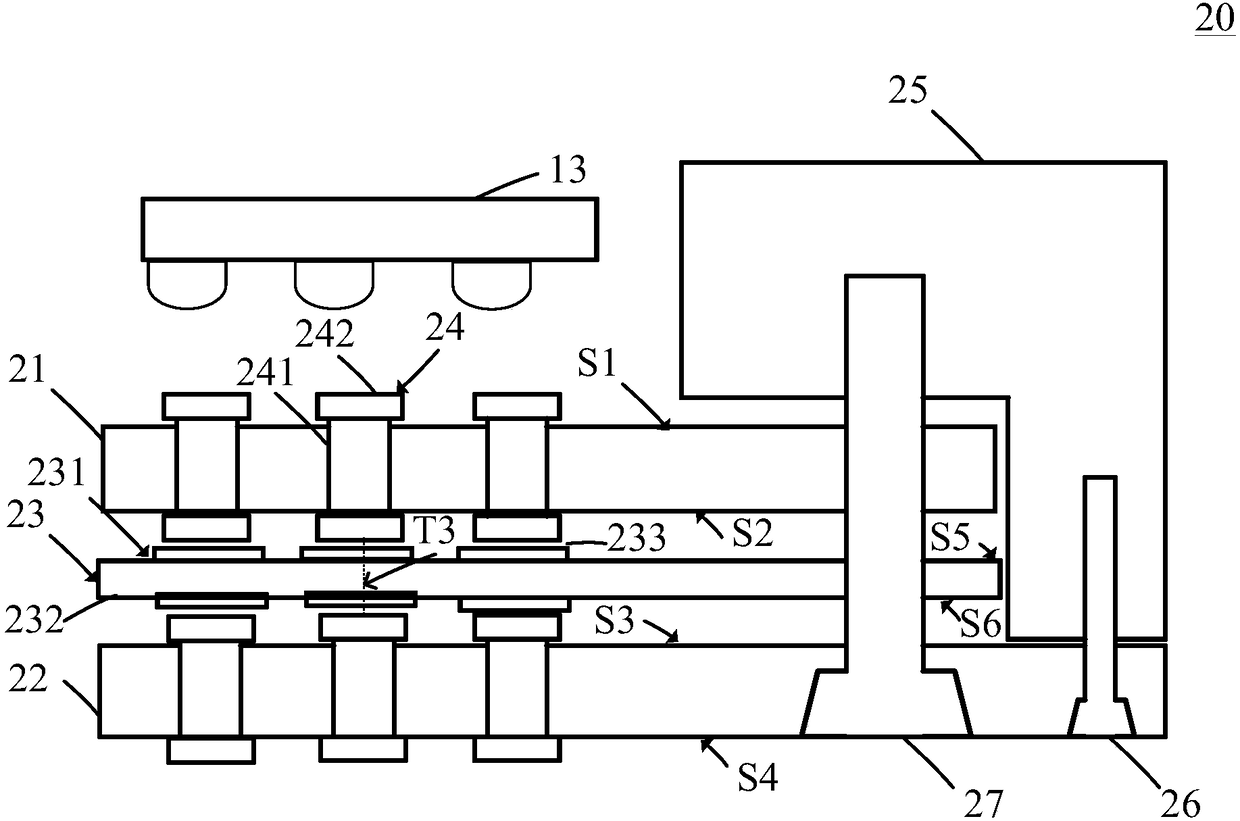

ActiveUS20200396855A1Shorten the current pathSemiconductor/solid-state device detailsSolid-state devicesElectric current flowComputer science

The present disclosure provides an assembly structure for providing power for a chip and an electronic device using the same. The assembly structure includes: a circuit board, configured to provide a first electrical energy; a chip; a power converting module, configured to electrically connect the circuit board and the chip, convert the first electrical energy to a second electrical energy, and supply the second electrical energy to the chip, wherein the chip, the circuit board and the power converting module are stacked; and a connection component, configured to electrically connect the circuit board and the power converting module. The present disclosure assembles a power converting module with a circuit board and a chip in a stacking manner, which may shorten a current path between the power converting module and the chip, reduce current transmission losses, improve efficiency of a system, reduce space occupancy and save system resource.

Owner:DELTA ELECTRONICS INC

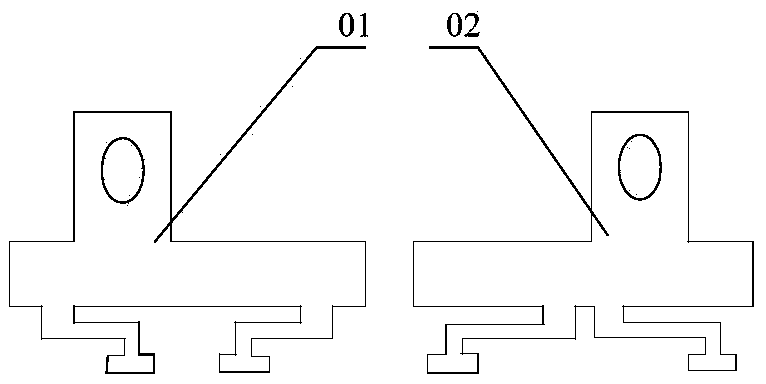

Electric connector

ActiveCN110416789AShorten the current pathImprove high frequency characteristicsSecuring/insulating coupling contact membersCoupling contact membersPower flowButt joint

The invention discloses an electric connector; the electric connector is used for being mounted to a circuit board to be electrically connected with a chip module, wherein the electric connector comprises an insulating body equipped with a plurality of terminal holes, and a plurality of conducting terminals which are contained in the terminal holes in a one-to-one correspondence mode; the insulating body has an upper surface and a lower surface which are opposite to each other; the terminal holes penetrate through the upper surface and the lower surface; each conducting terminal comprises a butt joint arm and a welding arm, wherein the butt joint arm is used for being in contact with the chip module, and the welding arm is used for being welded to the circuit board and extends up and down;each butt joint arm comprises a first main body portion and an elastic arm, wherein the first main body portion is fixedly clamped in the corresponding terminal hole, and each elastic arm extends andbends upwardly from the first main body portion to extend out of the upper surface; each butt joint arm and the corresponding welding arm are independent and are arranged at intervals; and the elastic arms move when the chip module presses down to prop against the welding arms downwardly so as to form electric conduction, and therefore the current path between the chip module and the circuit board is shortened, and the high-frequency performance of the electric connector is improved.

Owner:FUDING PRECISION COMPONENTS SHENZHEN +1

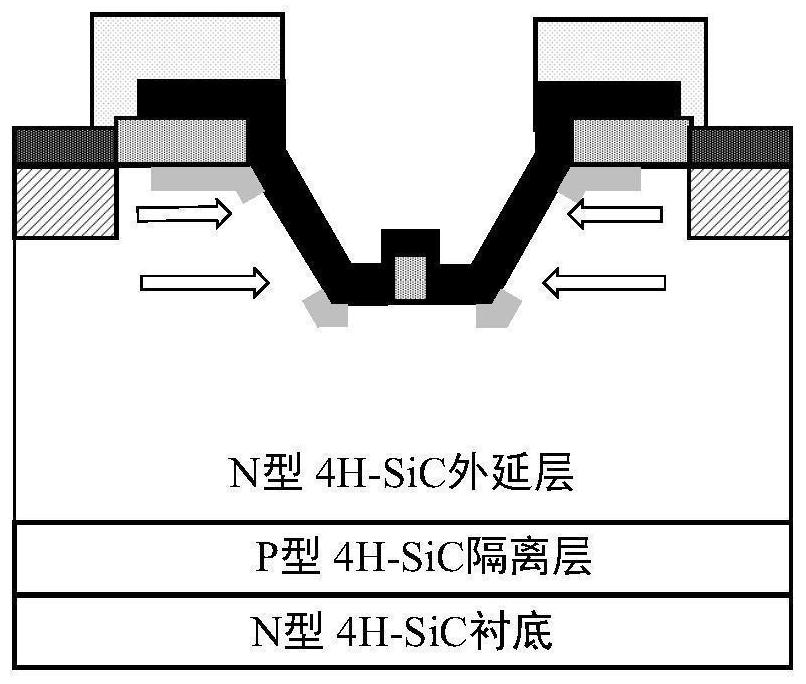

SiC Schottky power diode and production method thereof

PendingCN113964207AIncreased surface areaImprove forward conduction abilitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsPower diode

The invention discloses a SiC Schottky power diode which comprises a substrate, an isolation layer and an epitaxial layer. A cathode groove is engraved in the middle of the first region of the epitaxial layer, and an N + injection region is formed on the surface of the second region and the cathode groove; two P + injection regions are formed on the epitaxial layer at two sides of the cathode groove, a first passivation layer is covered on one P + injection region, a second passivation layer is partially covered on the other P + injection region, and an anode ohmic contact metal layer is partially covered on the other P + injection region; a cathode ohmic contact metal layer covers right above the N + injection region and fills the cathode groove; an anode schottky metal layer is stacked at the uppermost part of the first region, is electrically connected with the anode ohmic contact metal layer, and forms a PIN structure together with the two P + injection regions; and an intermediate medium is arranged between the cathode ohmic contact metal layer and the anode Schottky metal layer. According to the invention, the performance and yield of the 4H-SiC Schottky power diode under a high working voltage are improved.

Owner:瑶芯微电子科技(上海)有限公司

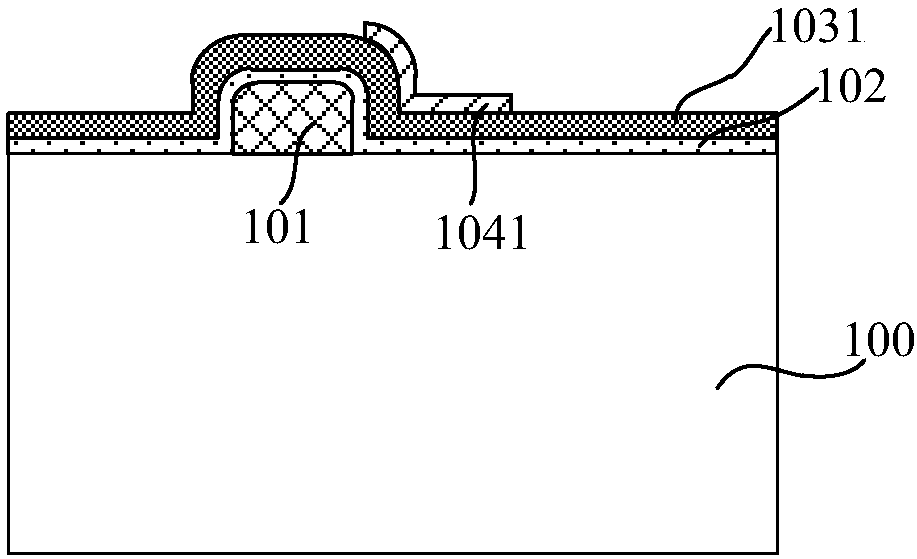

Chip and forming method thereof

PendingCN111834333AShorten the current pathLower resistanceSemiconductor/solid-state device detailsSolid-state devicesPhysicsStorage cell

The invention provides a chip and a method of forming the same. The chip includes: a substrate including a storage region and a peripheral region; a storage array formed in the storage region; at least one anti-fuse device formed in the peripheral region and used for repairing a storage defect caused by a failure storage unit in the storage array, wherein the anti-fuse device comprises a gate structure located on the surface of the substrate, and the gate structure comprises a gate dielectric layer located on the surface of the substrate and a gate located on the surface of the gate dielectriclayer; and a doped region arranged in the substrate on one side of the gate structure parallel to the surface direction of the substrate, wherein at least part of the edge of the doped region is aligned with the edge of the gate or is positioned below the gate, and the anti-fuse device is easier to be broken down.

Owner:CHANGXIN MEMORY TECH INC

Semiconductor device and process for fabricating the same

ActiveCN1875481BAchieve thinningExcellent electrical propertiesSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A thin stacked semiconductor device suitable for high speed operation. A plurality of specified circuits are formed on one surface of a semiconductor substrate while being arranged, and wiring and insulating layers being connected electrically with the circuits are laminated and formed sequentially in a specified pattern to form a multilayer wiring part. At the stage for forming the multilayer wiring part, a filling electrode is formed on the semiconductor substrate such that the surface is covered with an insulating film, a post electrode is formed on specified wiring at the multilayer wiringpart, a first insulating layer is formed on one surface of the semiconductor substrate, the surface of the first insulating layer is removed by a specified thickness to expose the post electrode, theother surface of the semiconductor substrate is ground to expose the filling electrode and to form a through-type electrode, forward end of the through-type electrode is projected by etching one surface of the semiconductor substrate, a second insulating layer is formed on one surface of the semiconductor substrate while exposing the forward end of the through-type electrode, bump electrodes areformed on both electrodes and then the semiconductor substrate is divided to form a semiconductor device. A plurality of semiconductor devices thus obtained are stacked and secured at the bump electrodesthus manufacturing a stacked semiconductor device.

Owner:TAIWAN SEMICON MFG CO LTD

electrical connector

ActiveCN110416789BShorten the current pathImprove high frequency characteristicsSecuring/insulating coupling contact membersCoupling contact membersElectrical connectionElectrical connector

The invention discloses an electrical connector, which is used for being mounted on a circuit board to electrically connect a chip module. The electrical connector comprises an insulating body with a plurality of terminal holes and a plurality of correspondingly accommodated in the The conductive terminal in the terminal hole, the insulating body has opposite upper and lower surfaces, the terminal hole penetrates the upper and lower surfaces, and the conductive terminal includes a docking arm for contacting the chip module and a soldering arm for soldering to the circuit board and extending up and down, the butt arm includes a first main body portion fixed in the terminal hole and the first main body portion is bent upwardly and extends out of the The elastic arm on the upper surface, the docking arm and the welding arm are independent and spaced apart from each other, the elastic arm moves when the chip module is pressed down and presses the welding arm downward to form electrical conduction, thereby shortening the The current path between the chip module and the circuit board improves the high-frequency performance of the electrical connector.

Owner:FUDING PRECISION COMPONENTS SHENZHEN +1

Electromagnetic compatibility device for spark light source of photoelectric direct-reading spectrometer

ActiveCN102853911BGuaranteed flow backGuaranteed shielding effectRadiation pyrometrySpectrometry/spectrophotometry/monochromatorsHigh voltage igbtLow voltage

Owner:昆山书豪仪器科技有限公司 +1

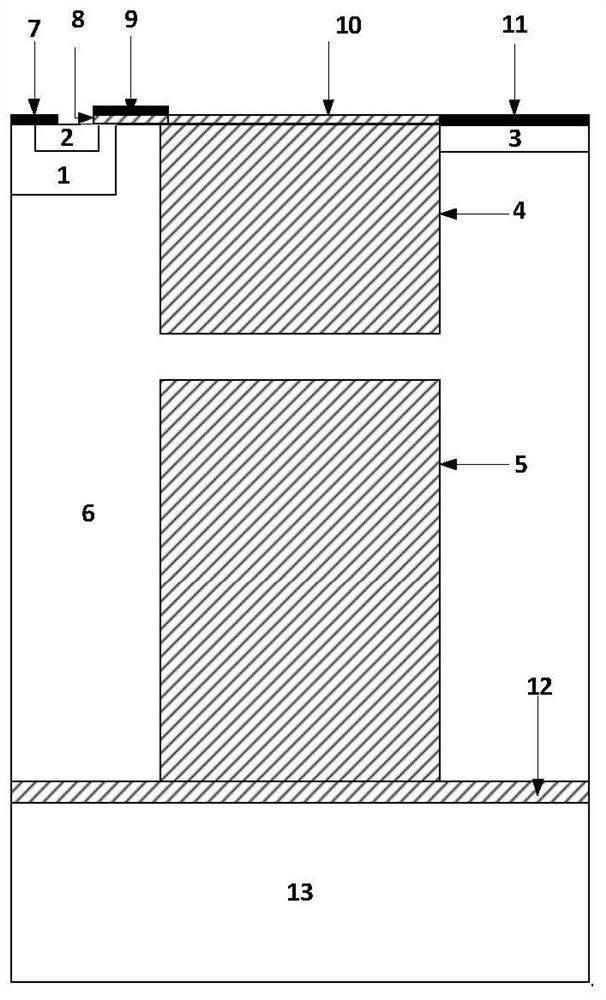

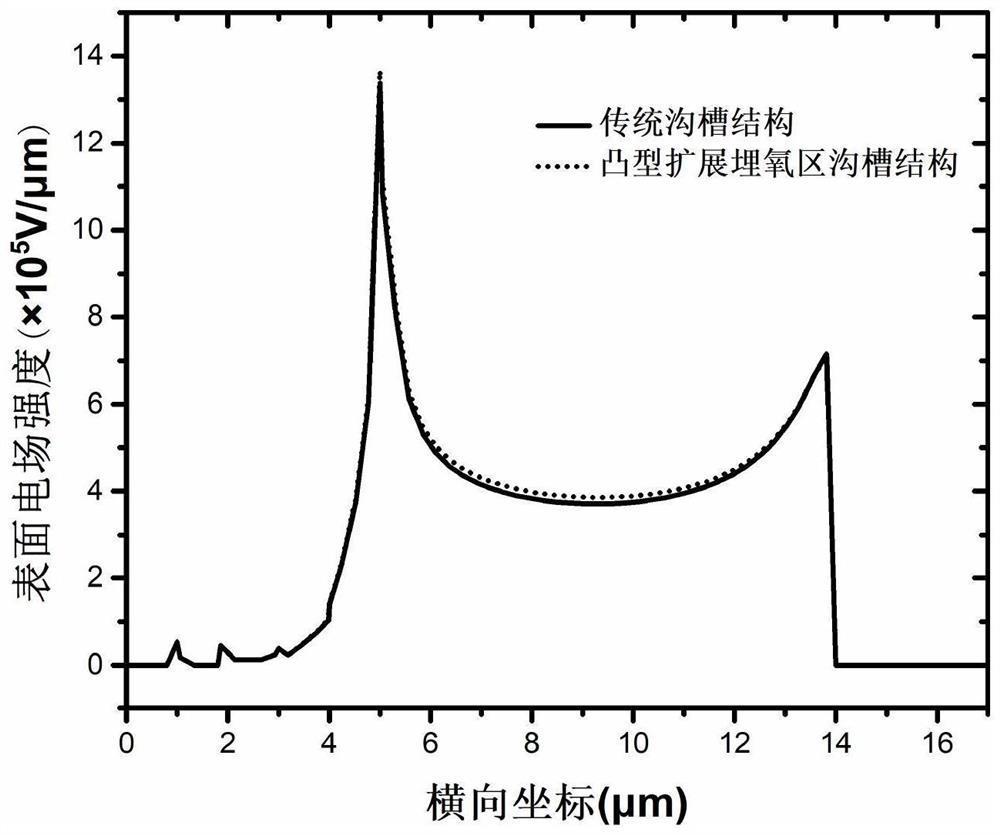

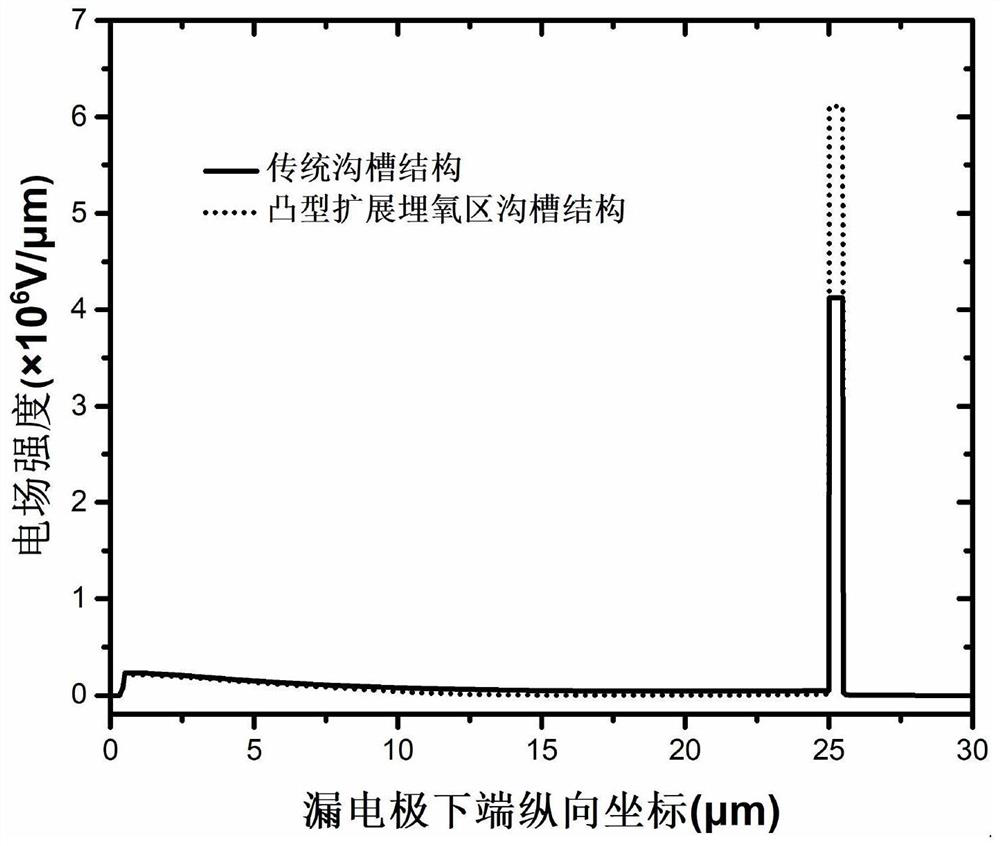

Trench LDMOS transistor with convex extended buried oxide region

ActiveCN112713193AImprove electric field distributionIncrease the electric field strengthSemiconductor devicesBuried oxideElectrical and Electronics engineering

The invention discloses a trench LDMOS transistor with a convex buried oxide layer. The buried oxide layer is located above the substrate layer; a silicon film layer is positioned above the buried oxide layer; the silicon film layer comprises a silicon body, a source region, a drain region, an oxidation trench, a convex extended buried oxide region and a drift region; the oxidation trench is located at the top of the silicon film layer and located between the silicon body and the drain region; the convex extended buried oxide region is positioned at the bottom of the silicon film layer; a device top layer is arranged above the silicon film layer and comprises a source electrode, a gate oxide layer, a gate electrode, an extended oxide layer and a drain electrode; the gate oxide layer is located above the channel and completely covers the channel; the gate electrode is located right above the gate oxide layer and completely covers the gate oxide layer; the extended oxide layer is positioned above the silicon film layer and is in contact with one side, far from the source electrode, of the gate oxide layer; and the drain electrode completely covers the drain region and is in contact with one side, far from the gate oxide layer, of the extended oxide layer. According to the invention, the electric field distribution is improved through the coupling between the oxidation trench and the convex extended buried oxide region, and the conduction resistance and the quality factor are more excellent.

Owner:杭州电子科技大学温州研究院有限公司 +1

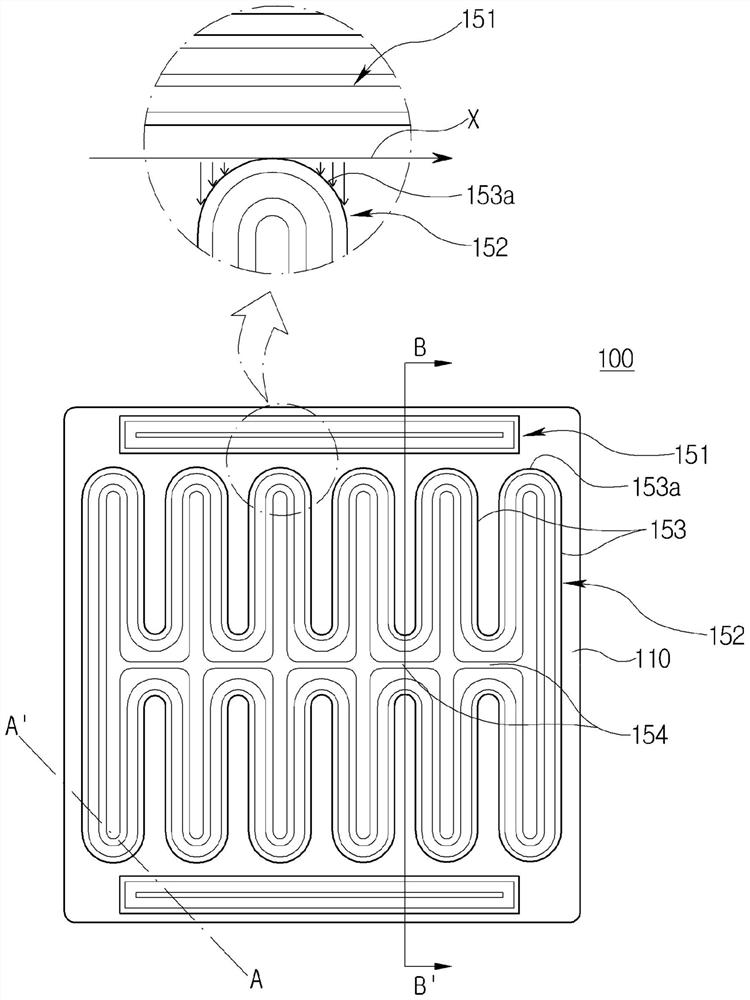

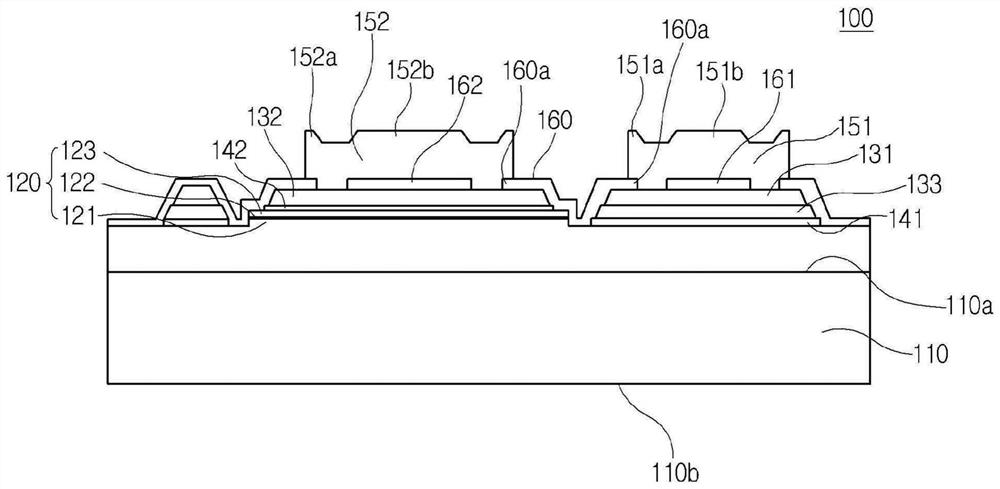

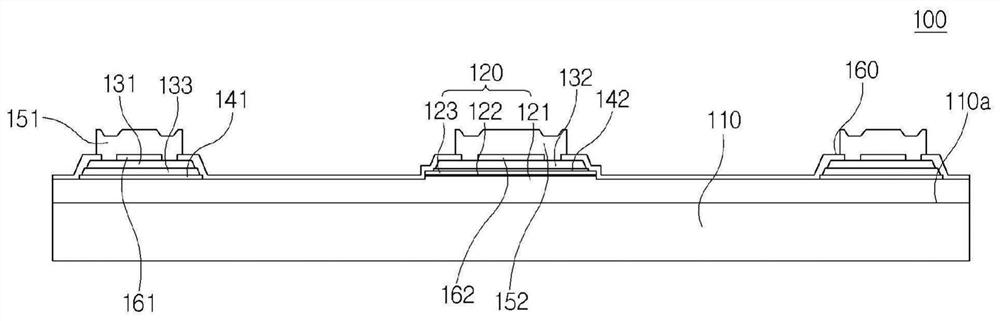

Light-emitting device

PendingCN113948623ALower resistanceLow working voltageSolid-state devicesSemiconductor devicesPhysicsChemistry

A light-emitting device according to the invention comprises: a substrate; a first conductive type semiconductor layer disposed on the substrate; a mesa disposed on the first conductive type semiconductor layer and including a second conductive type semiconductor layer and an active layer; a first contact electrode contacting the exposed first conductive type semiconductor layer around the mesa; a second contact electrode contacting the second conductive type semiconductor layer on the mesa; a passivation layer covering the first contact electrode, the mesa, and the second contact electrode and having openings; and first and second bump electrodes electrically connected to the first and second contact electrodes through the openings of the passivation layer, wherein the mesa has a plurality of depressions when viewed from above, the first contact electrode is separated from the mesa at a predetermined distance and formed to surround the mesa and contacts the first conductive type semiconductor layer in the pluraity of depressions, and the first and second bump electrodes cover the openings of the passivation layer and a part of the passivation layer.

Owner:SEOUL VIOSYS CO LTD

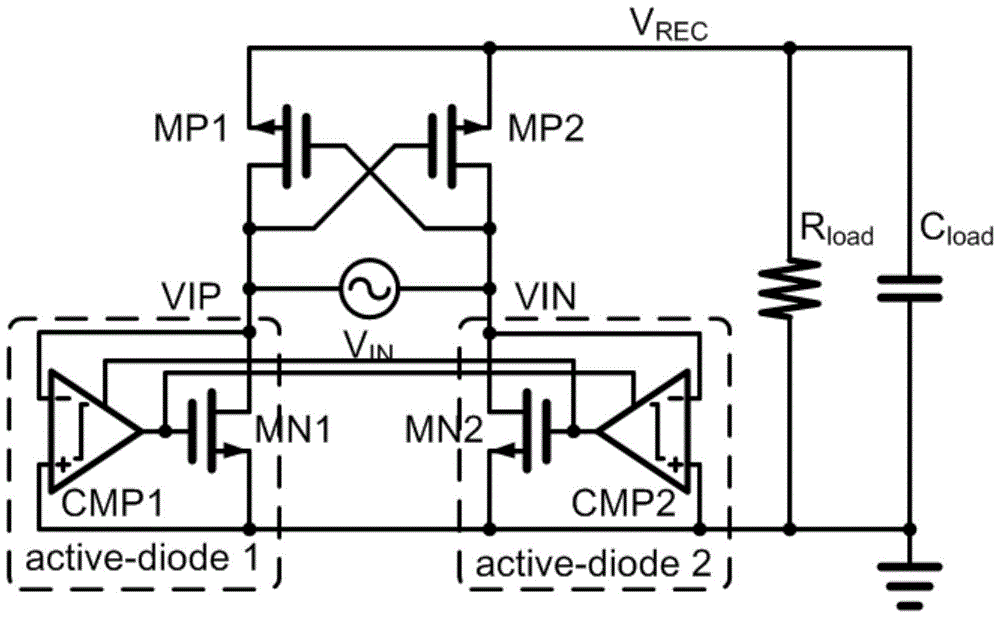

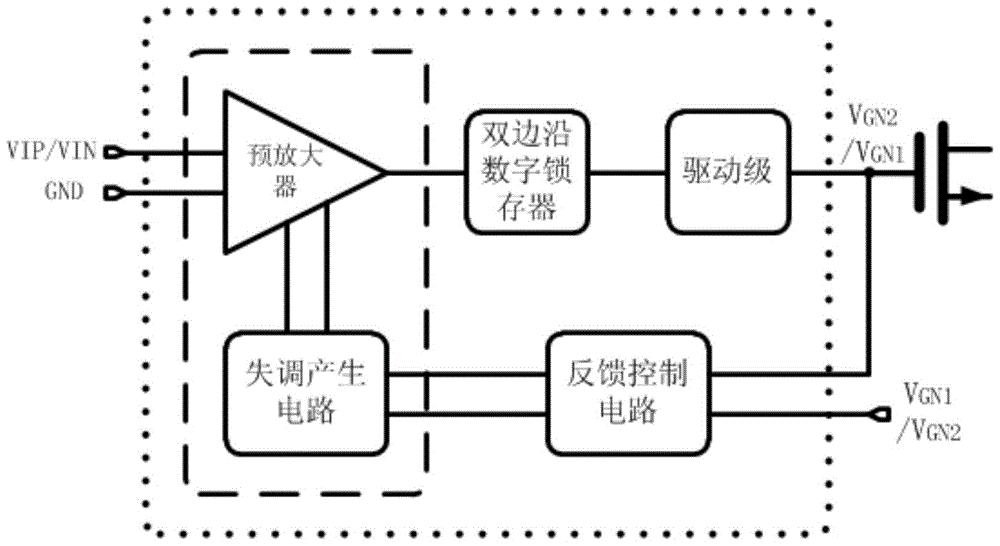

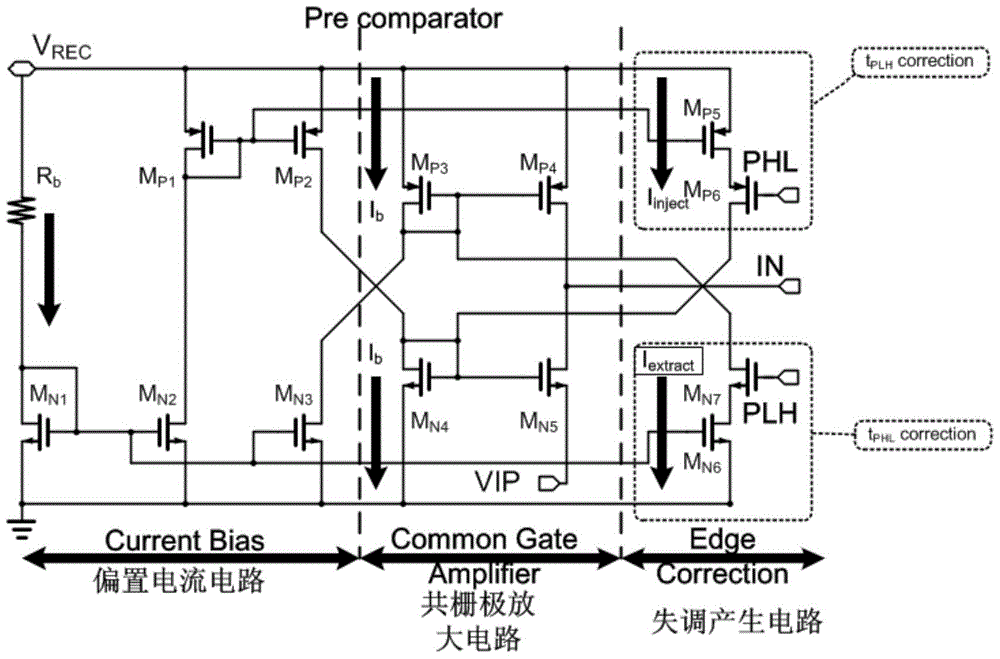

Dual Edge Look-ahead Enhanced Comparator and Its Active Full-Bridge Rectifier

ActiveCN104467761BRealize individual adjustmentShorten the current pathMultiple input and output pulse circuitsAc-dc conversionFull bridgeHemt circuits

Owner:XI AN JIAOTONG UNIV

A cross-band frequency conversion antenna based on intelligent origami structure

ActiveCN108461906BShorten the lengthIncrease the lengthRadiating elements structural formsAntennas earthing switches associationFrequency conversionFrequency modulation

The present invention relates to a cross-band frequency-conversion antenna based on an intelligent paper folding structure, belonging to the field of frequency reconfigurable antennas. The antenna comprises a substrate, an antenna arms, a coaxial feeder, a radio frequency coaxial connector and a RF signal emitter; the substrate employs a self-locking square-twist folding structure; the middle portion of the substrate is provided with a cross-line hole, the two antenna arms are symmetrically glued and fixed at the upper side plate surface of the substrate, the initiating terminal of each antenna arm is extended outwards from the cross-line hole, each antenna arm is located the panel overlapping position for ducking in a folding state; the initiating terminals of the antenna arms are respectively connected with two output ports of the RF signal emitter through the coaxial feeder via the radio frequency coaxial connector, and output signal phase difference of two ends of the RF signal emitter is 180 degrees. The antenna can be subjected to self unfolding through heating to change working frequency, the influence of frequency modulation on performances of the antenna is little, the frequency tuning amplitude is large, and cross of different wave bands can be achieved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Insulated gate bipolar thyristor module and electrode power terminals

ActiveCN103545282BFlexible designEliminate the inability to interconnectSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionInductance

The present invention provides an insulated gate bipolar thyristor module and an electrode power terminal, wherein the electrode power terminal includes a first electrode and a second electrode, and the first electrode and the second electrode are composed of a multilayer board, The multi-layer board includes N-layer electrode boards, and an insulating board is arranged between two adjacent layers of electrode boards, wherein the M-layer electrode boards are electrically connected through at least one first through hole to form the first electrode, and Each of the first through holes is electrically insulated from every electrode plate except the M layer of electrode plates, and at least one layer of electrode plates other than the M layer of electrode plates constitutes the second electrode. Since the multilayer electrode plates are electrically connected through the first through holes, the alternate arrangement of the multilayer electrode plates can be realized, which can increase the area where the electrodes face each other in parallel and reduce parasitic inductance. The parasitic inductance generated by the IGBT module based on the electrode power terminal is also low.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Portable electronic device

ActiveCN102244525BShorten the current pathAntenna supports/mountingsTransmissionCouplingElectrical and Electronics engineering

The invention provides a portable electronic device, comprising a demountable first shell, an antenna and a first coupling element, wherein the antenna is arranged in the demountable first shell; the first coupling element is arranged on the inner wall of the demountable first shell; and the first coupling element is separated from the antenna and overlapped with a part of the antenna on a vertically projective plane.

Owner:PEGATRON