Patents

Literature

32results about How to "Reduce surface leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

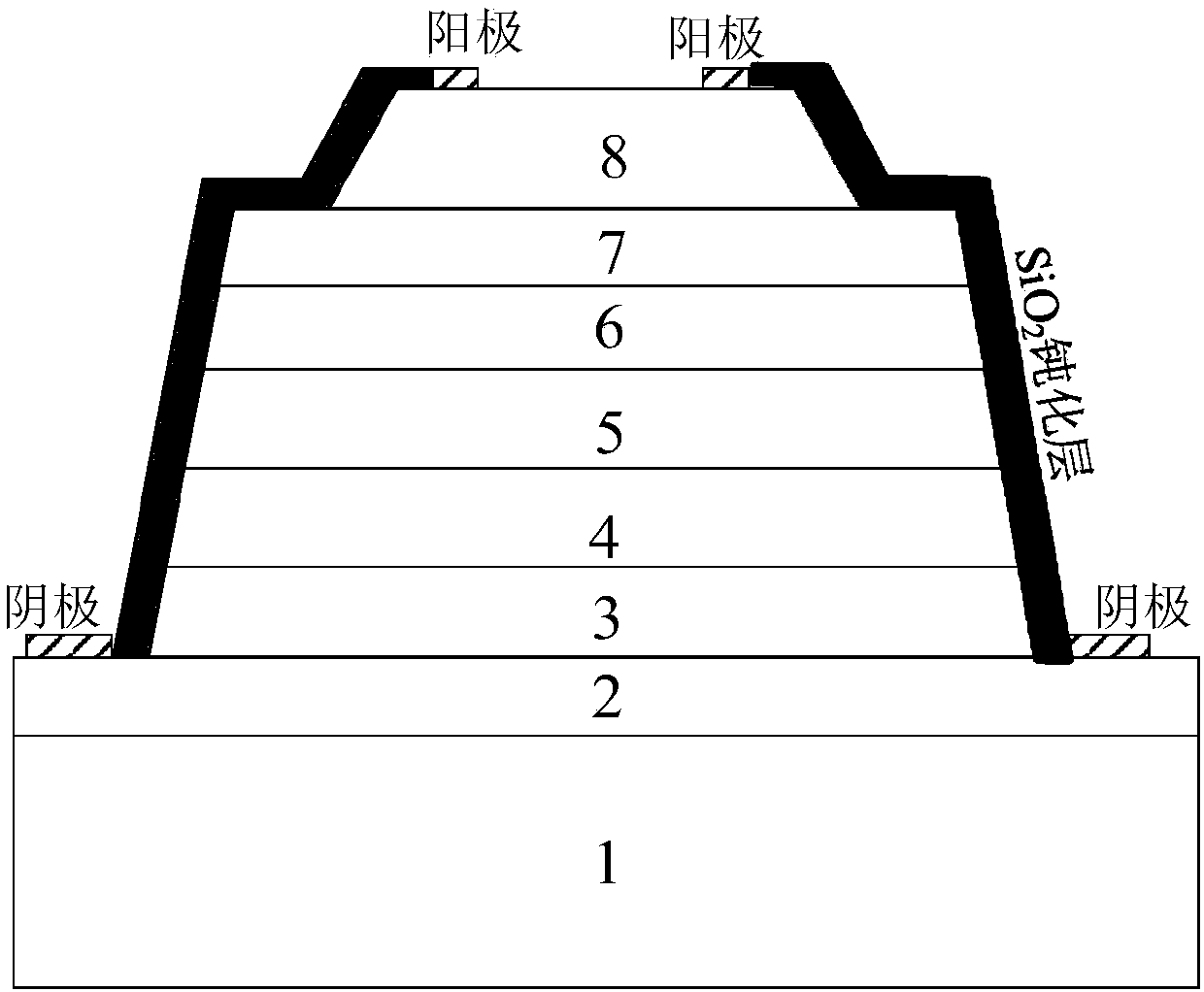

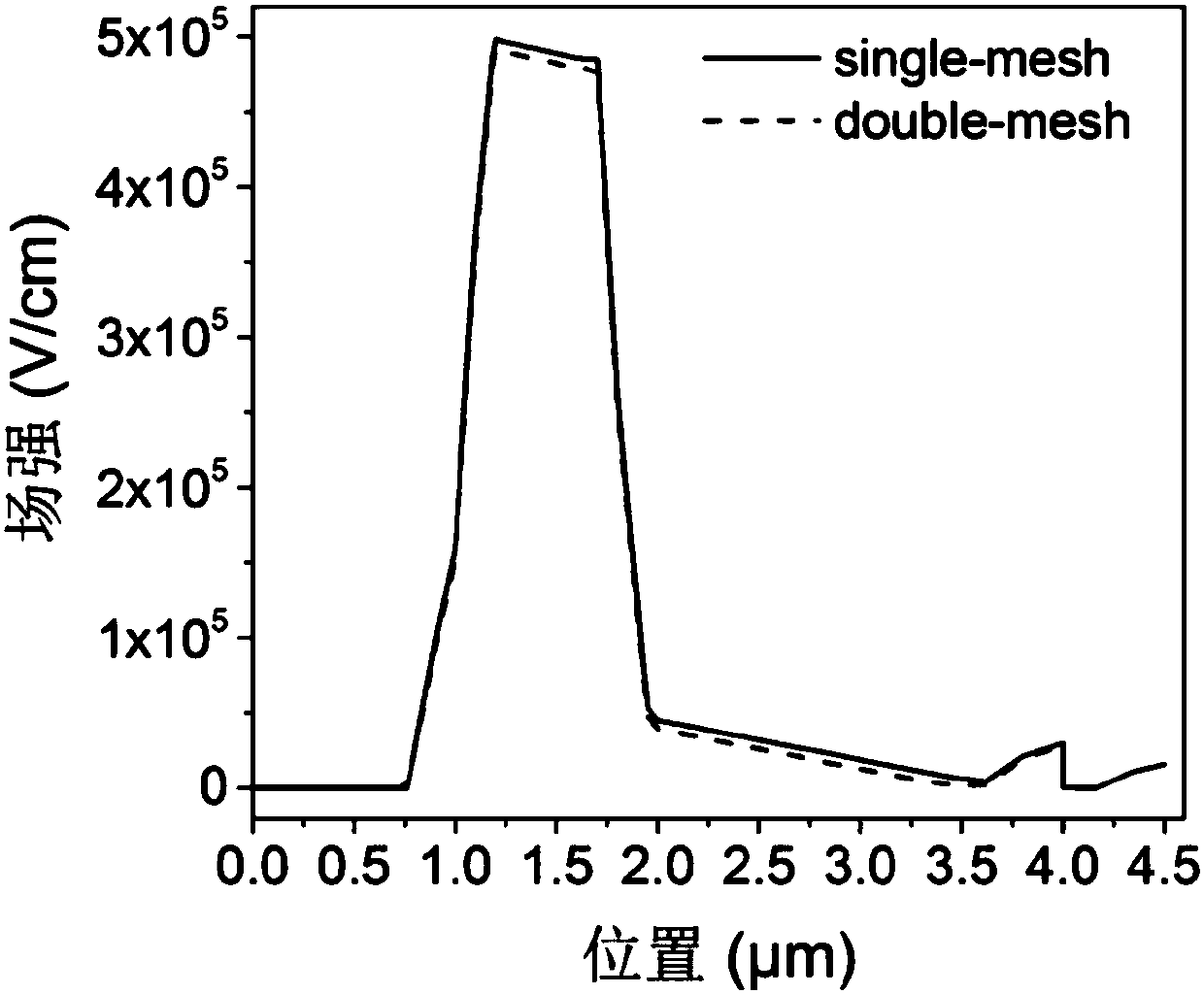

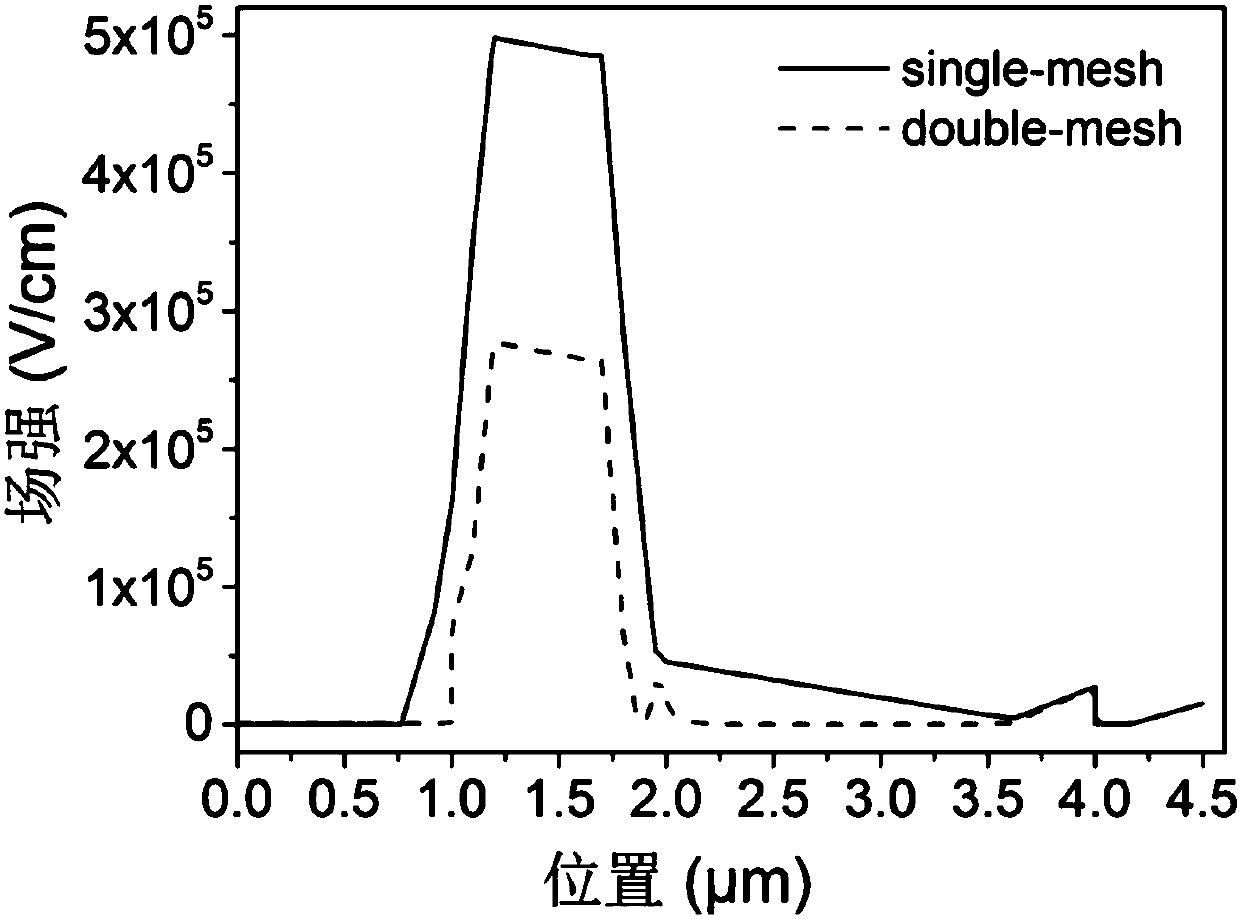

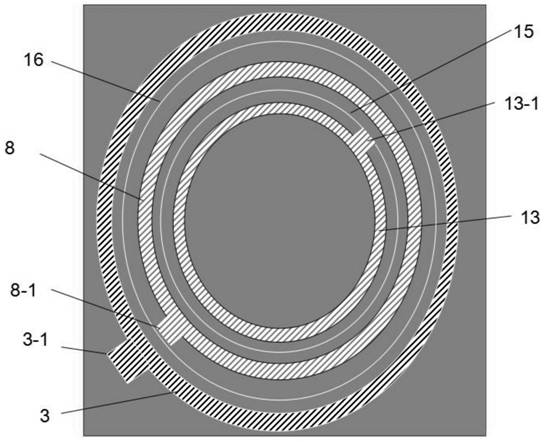

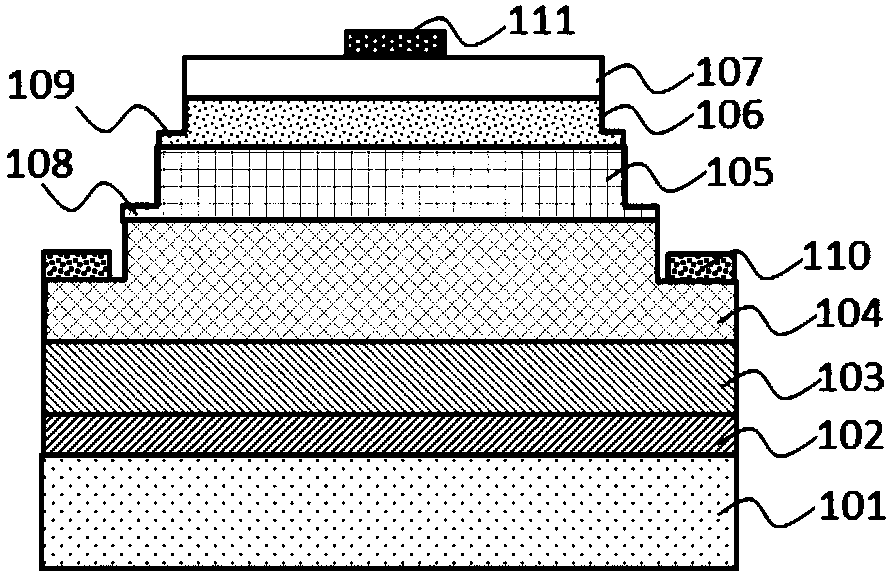

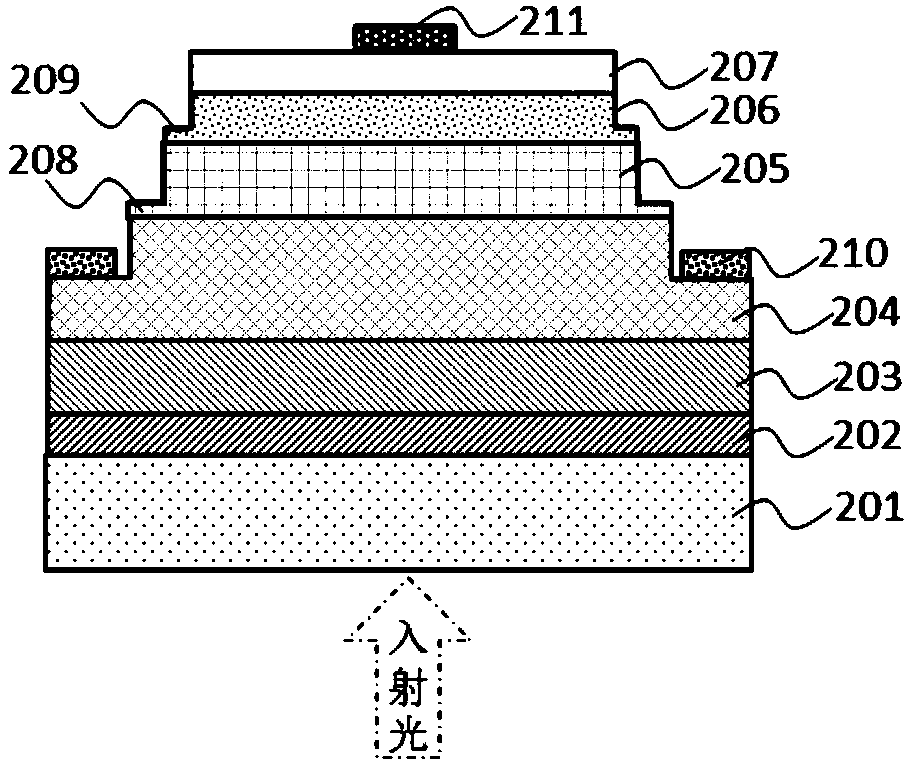

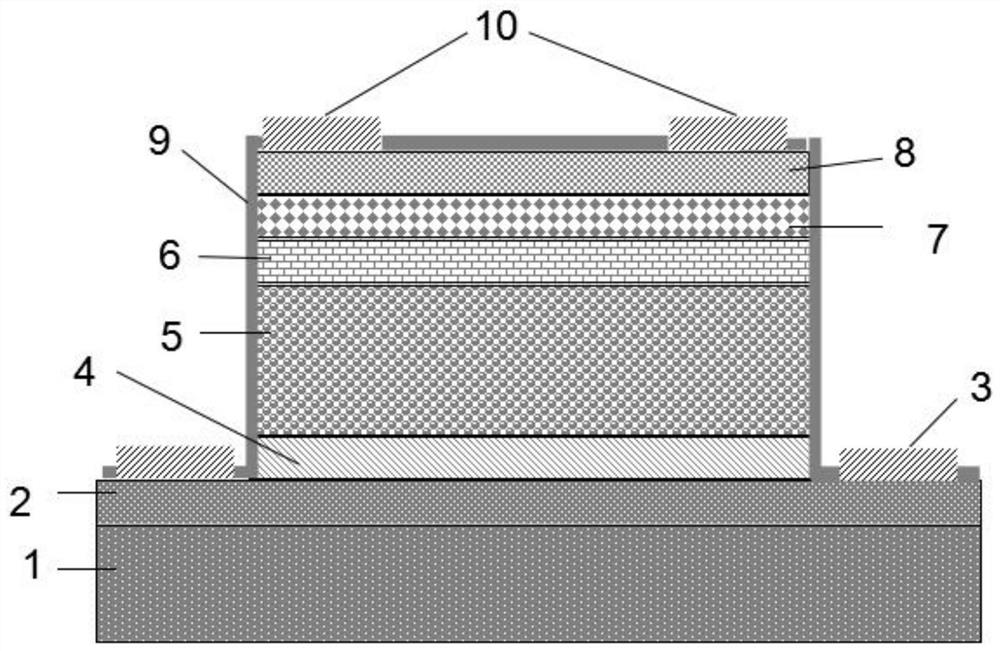

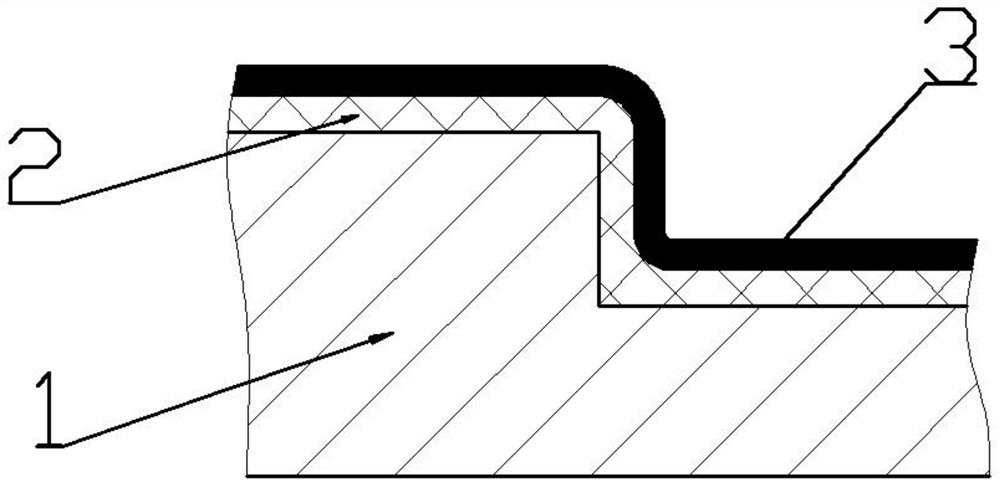

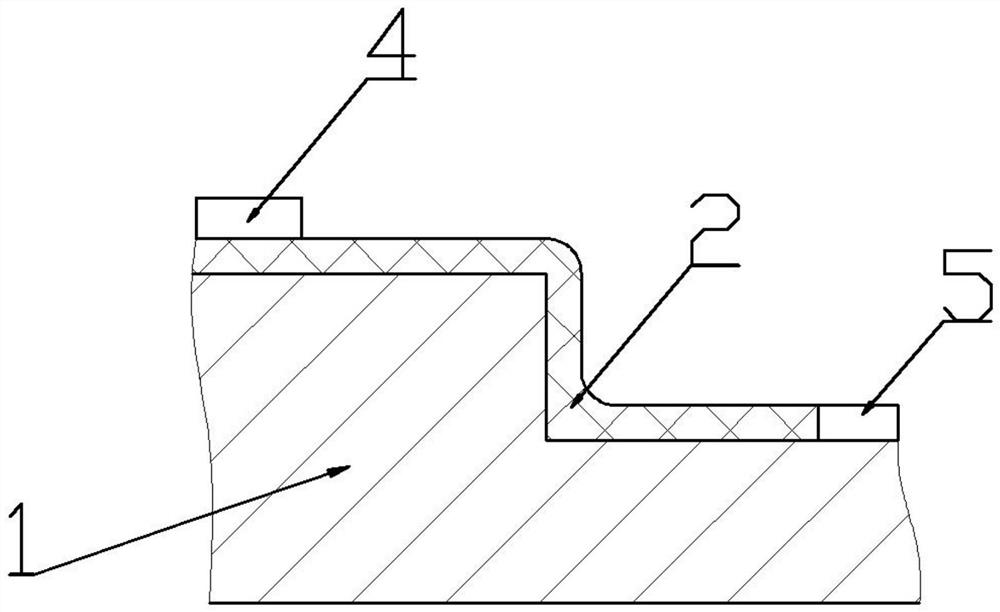

Two-stage table-top InGaAs/InP avalanche photodiode and preparation method thereof

InactiveCN107768462AReduce fringe electric fieldSuppresses edge breakdownSemiconductor devicesCharge layerContact layer

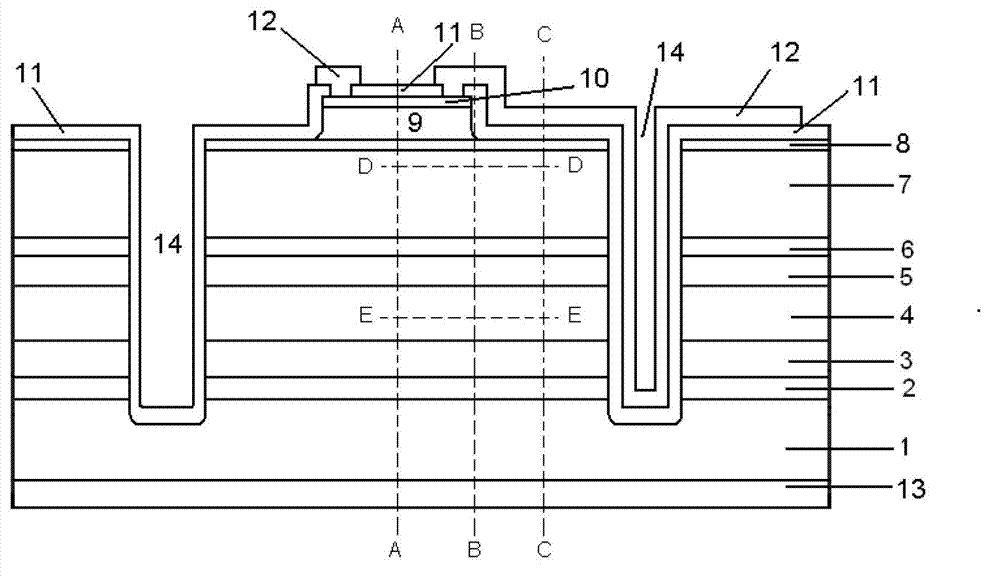

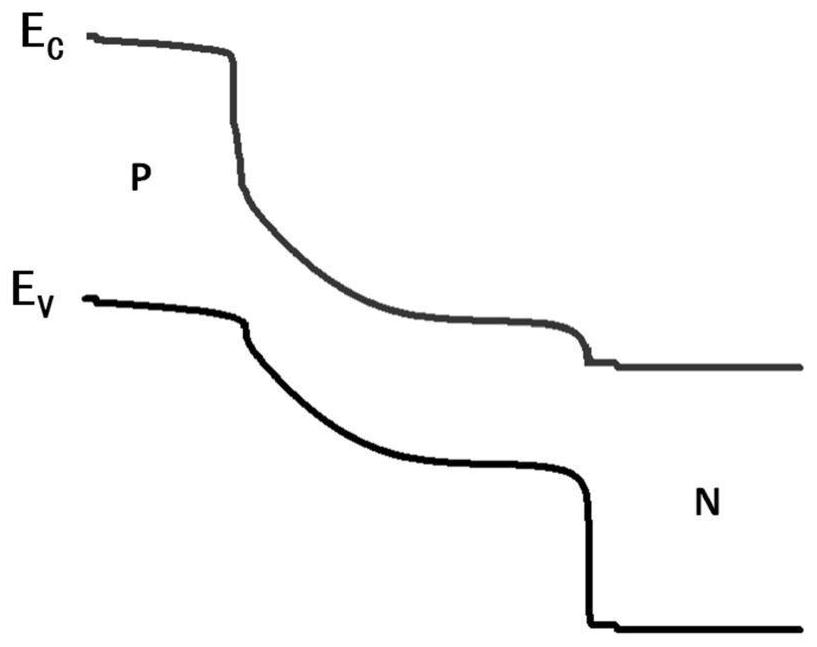

The invention belongs to the fields of photoelectric detection and image sensors, and in order to inhibit fringe field and reduce device dark current while guaranteeing a high field in the central area of the device, reference basis is provided for industrial application. The invention discloses a two-stage table-top InGaAs / InP avalanche photodiode and a preparation method thereof. The structure comprises an N<+>-InP substrate, an N-InP buffer layer, an N<->-InGaAs In0.53Ga0.47As absorbed layer, an N-InGaAsP In(1-x)GaxAsyP(1-y) component gradient layer, an N-InP charge layer, an i-InP multiplying layer, a P-InP field buffer layer and a P<+>-InP contact layer, wherein the P-InP field buffer layer forms a shallow table-top through etching, the N-InP buffer layer forms a deep table-top through etching, and constant impact ionization of photon-generated carriers inside the multiplying layer causes avalanche multiplication. The avalanche photodiode is mainly applied to the design occasionsof photoelectric detection and photoelectric sensors.

Owner:TIANJIN UNIV

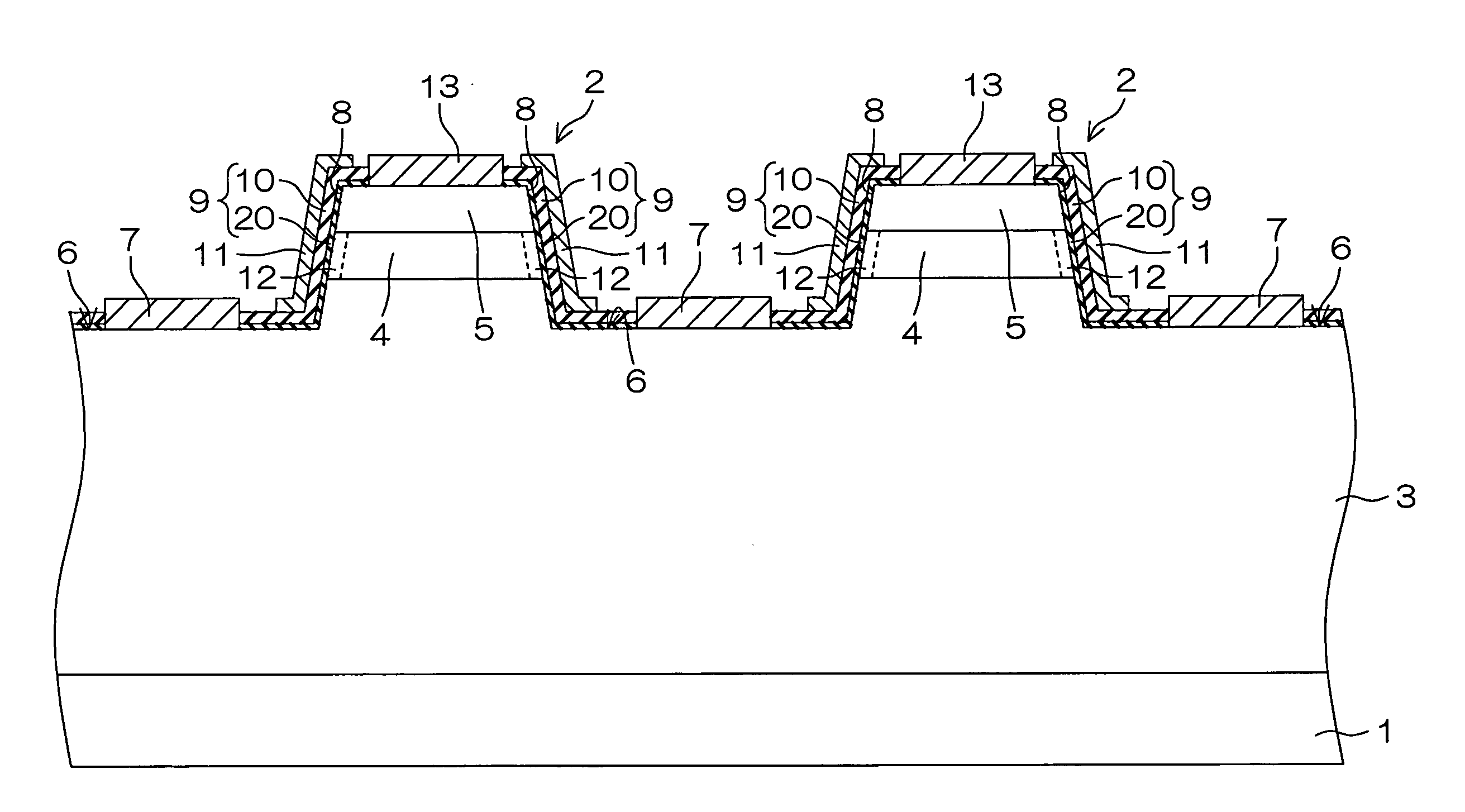

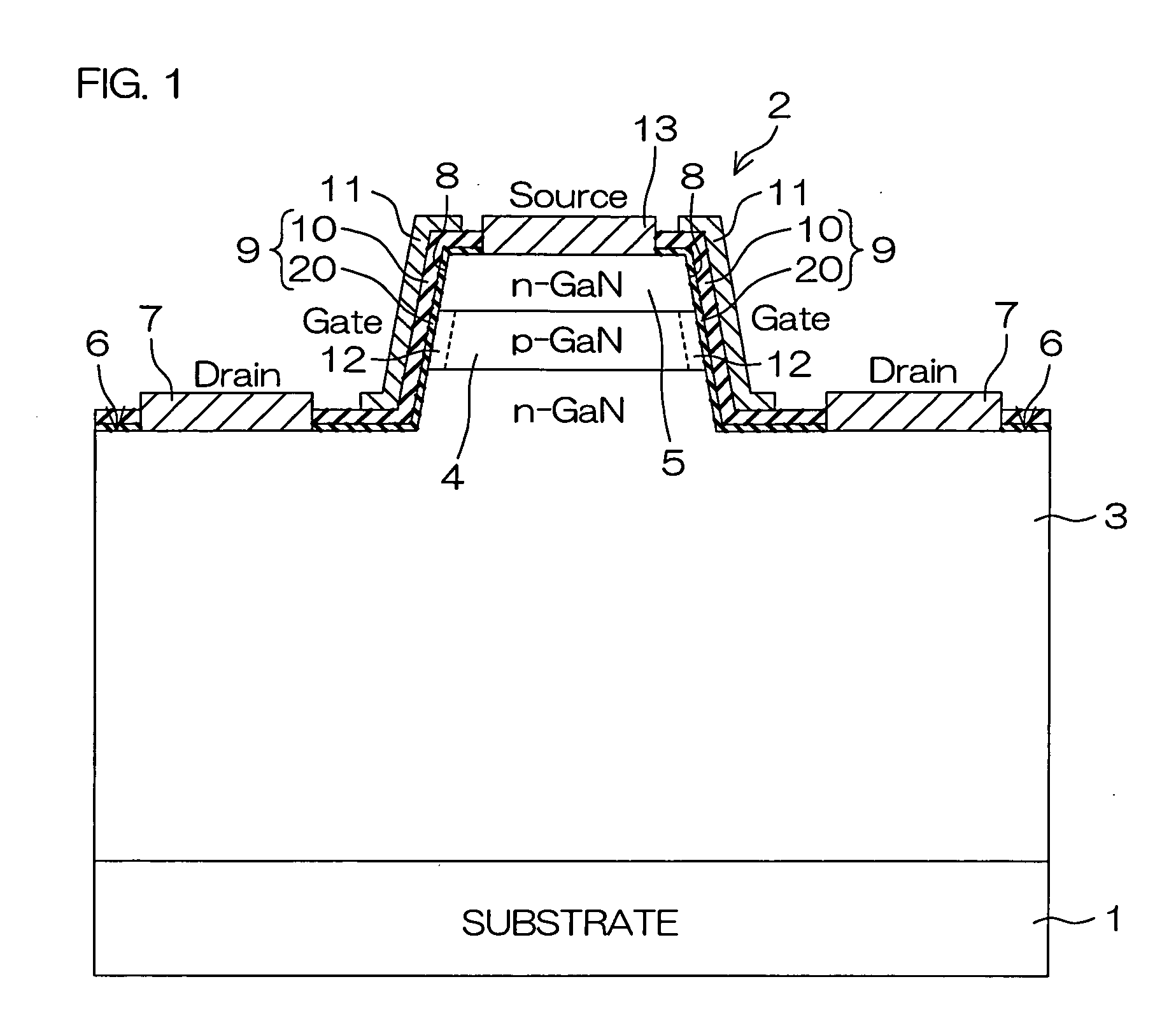

Nitride semiconductor device and method for producing nitride semiconductor device

ActiveUS20090026556A1Reduce surface leakage currentReduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingNitrogen atmosphereNitrogen gas

A method for producing a nitride semiconductor device according to the present invention includes the steps of: forming an insulating film containing oxygen on the surface of a group III nitride semiconductor; and placing the group III nitride semiconductor under a nitrogen atmosphere in advance of the step of forming the insulating film. A nitride semiconductor device according to the present invention includes a group III nitride semiconductor; and an insulating film containing oxygen formed on the surface of the group III nitride semiconductor, wherein the nitrogen concentration in a region provided with the insulating film is higher than the nitrogen concentration in a region not provided with the insulating film on the surface of the group III nitride semiconductor.

Owner:ROHM CO LTD

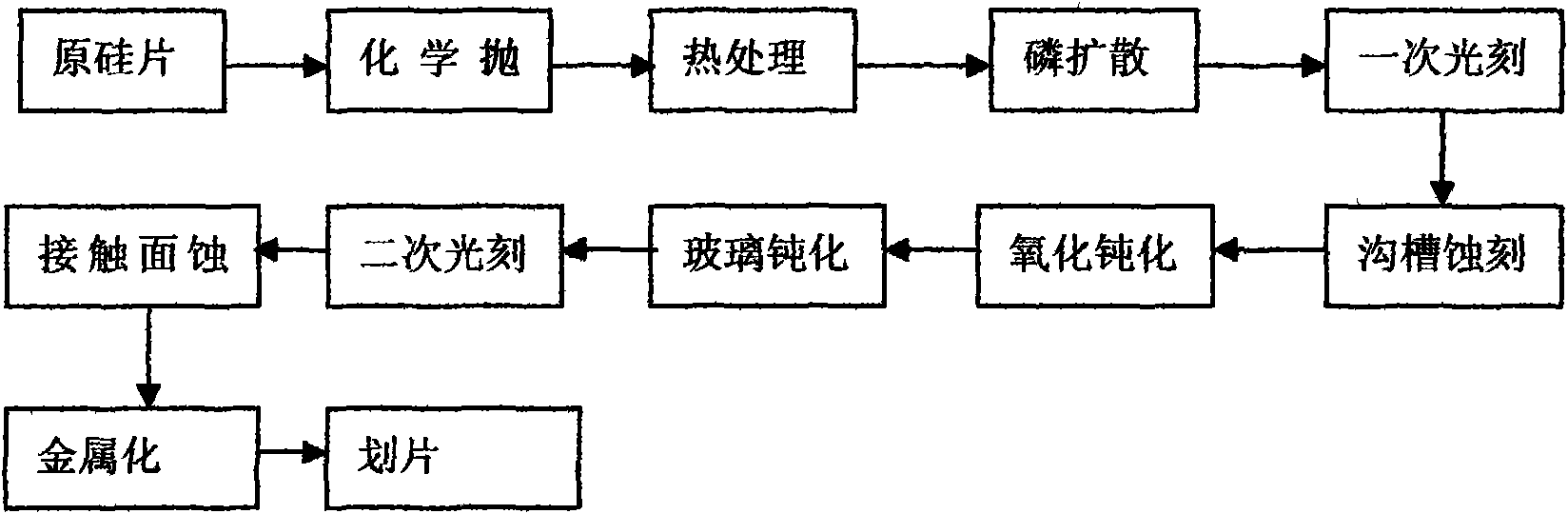

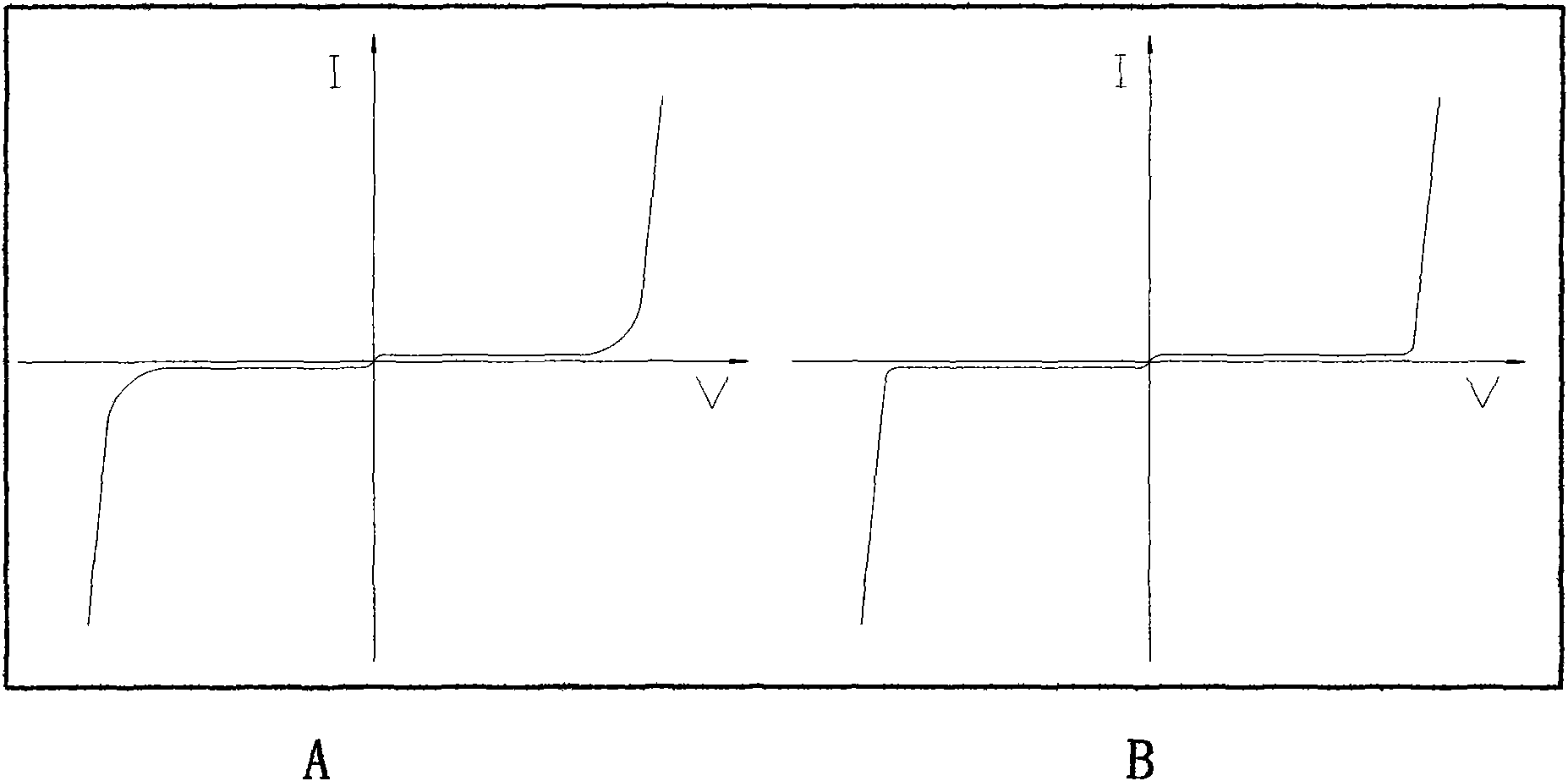

Manufacturing method of low-voltage transient voltage suppression diode chip

ActiveCN101621002APrevent penetrationEnhance the ability to capture alkali metal ionsSemiconductor/solid-state device manufacturingLow voltageCrystal orientation

The invention discloses a manufacturing method of a low-voltage transient voltage suppression diode chip, which is characterized by comprising the following steps: a. selecting a P type crystal orientation monocrystalline silicon piece with resistivity of 0.001-0.02 omega*cm; carrying out chemical polishing and heat treatment gettering technologies on the monocrystalline silicon piece to reduce the defects and the impurity concentration of the surface and near a P / N nodal area of the monocrystalline silicon piece so as to realize the characteristic of low internal current leakage; c. doping chlorine, thermally oxidizing and passivating a P / N nodal surface; and d. bending a P / N node on the edge part of the P / N nodal surface towards a P area through a thermal oxidation technology so as to realize the characteristic of low surface current leakage. The invention can effectively reduce the reverse current leakage.

Owner:BESTBRIGHT ELECTRONICS

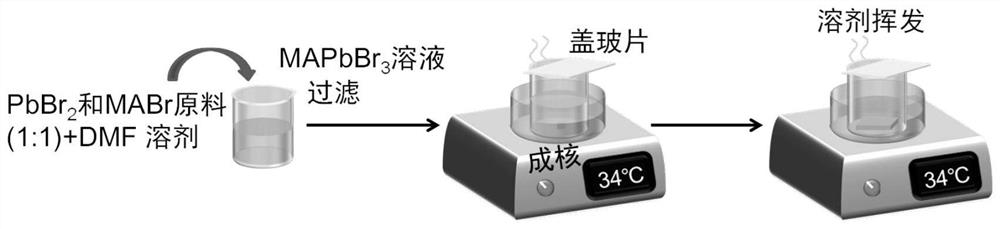

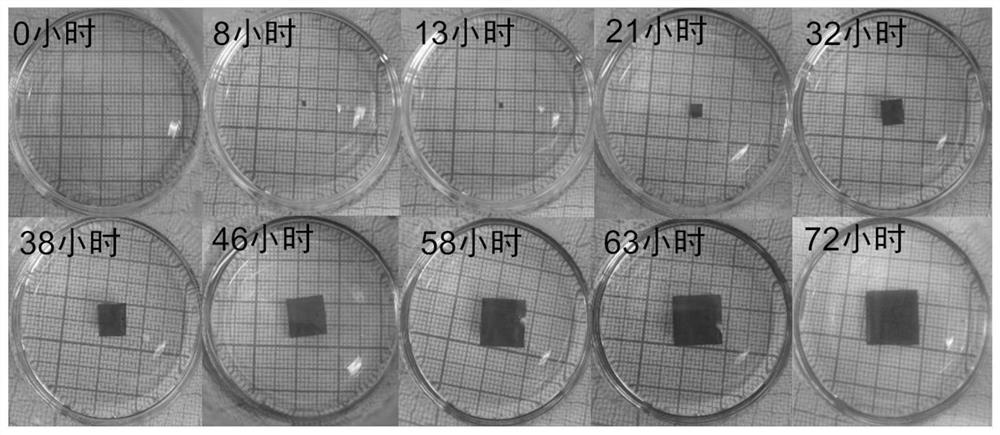

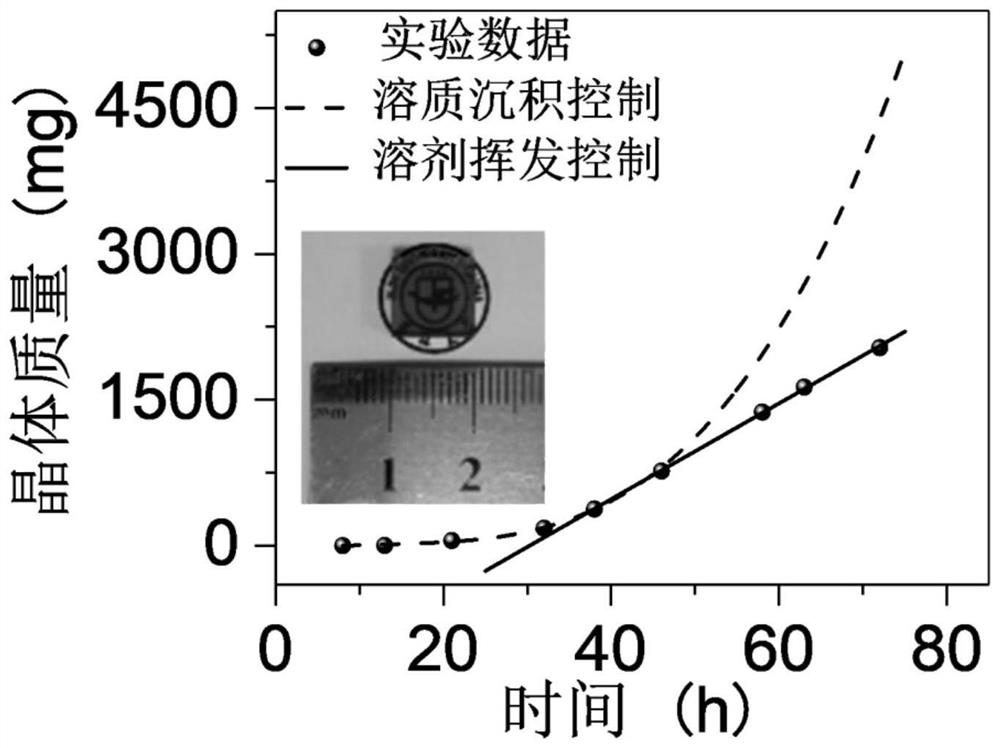

Halide perovskite single crystal, preparation method and application of halogenated perovskite single crystal in preparation of X-ray detector

ActiveCN111647944AReduce the density of defect statesQuality improvementPolycrystalline material growthFrom normal temperature solutionsCharge carrier mobilityMetallic materials

The invention discloses a halide perovskite single crystal, a preparation method and application of the single crystal in preparation of an X-ray detector, and belongs to the technical field of X-raydetectors. The invention develops a method for controlling the growth of halide perovskite single crystals through solvent evaporation, the growth rate of the crystals is constant mainly by regulatingand controlling the growth temperature, the opening area of a solution and other factors, and the perovskite single crystals with lower crystal defect state density and higher carrier mobility-carrier lifetime deposition are grown. Polyoxyethylene is used for passivating surface defects of the perovskite single crystal, so that the crystal surface defects and surface leakage current are remarkably reduced, and the crystal has higher resistivity and lower noise current signals. The sensitivity of the prepared X-ray detector under 120 keV hard rays reaches 1274 [mu] C.Gyair.cm <2>, the lowest detection amount is as low as 0.56 [mu] Gyair.s <-1>, the requirements of medical imaging application are met, and the X-ray detector can be applied to metal material component analysis and flaw detection.

Owner:JILIN UNIV

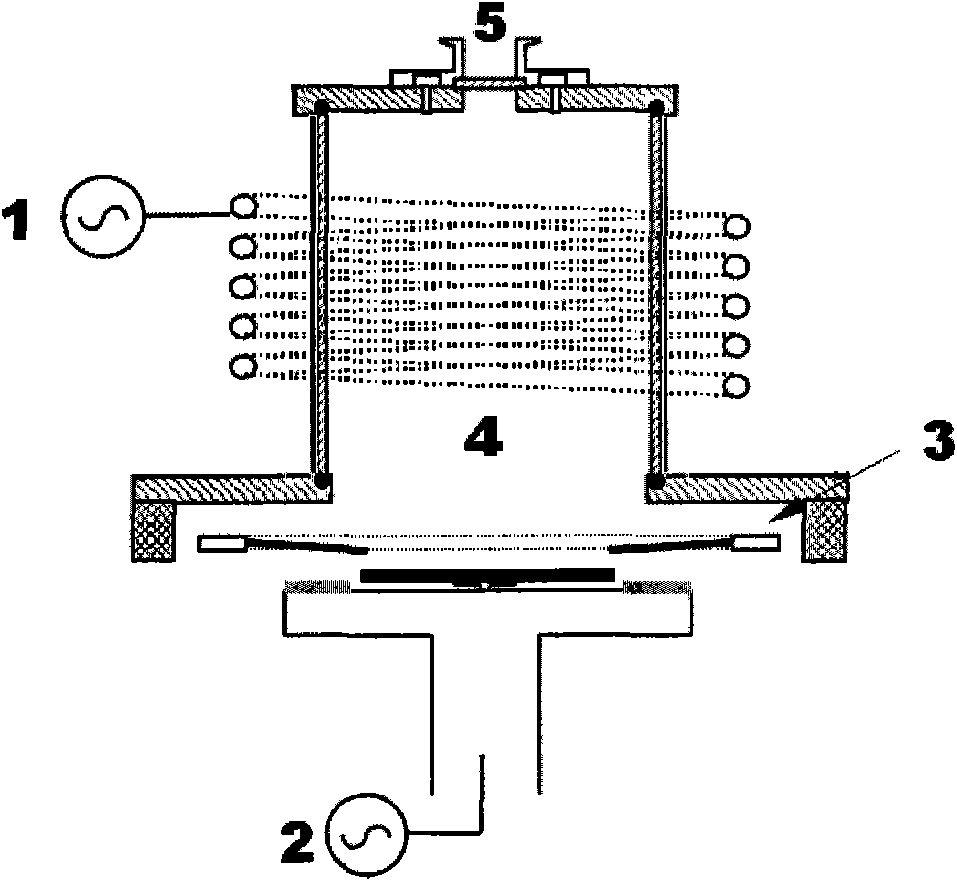

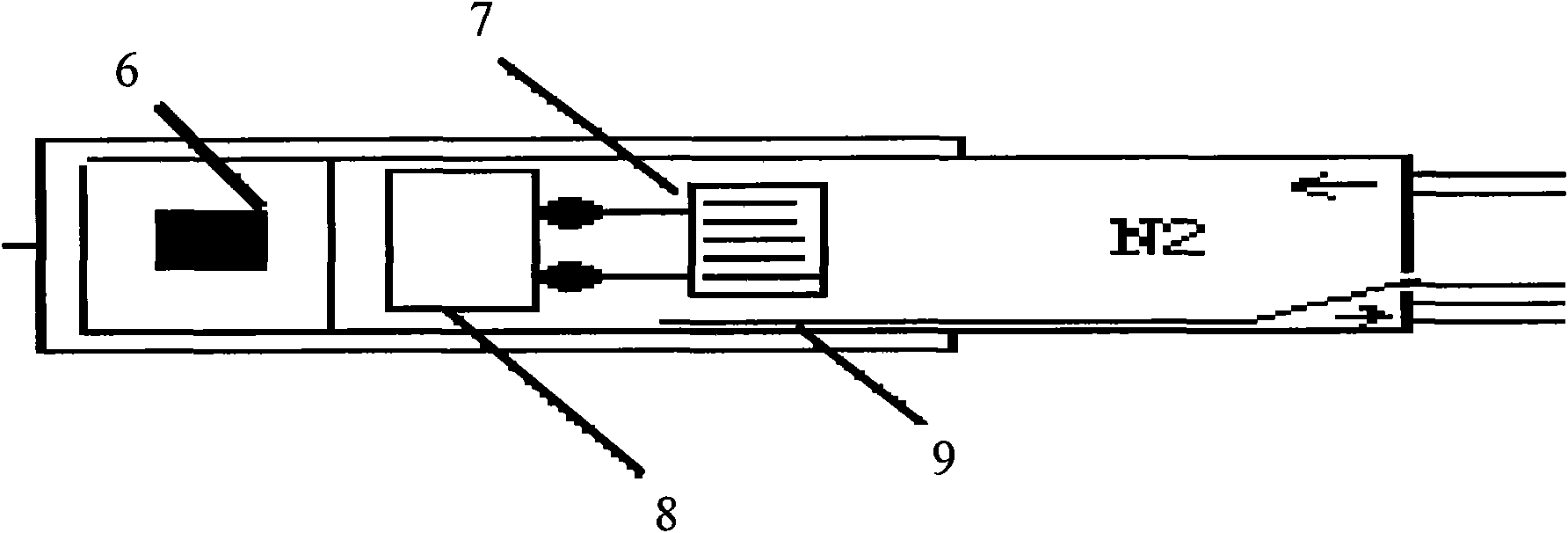

Dry etching method for two-color HgCdTe device and etching device thereof

InactiveCN101640230AReduce dry etch damageReduce surface leakage currentElectric discharge tubesFinal product manufactureHigh surfaceRadio frequency

The invention discloses a dry etching method for a two-color HgCdTe device and an etching device thereof. The device comprises a radio frequency source which is connected with an inductive coupling coil surrounding a reaction chamber, and the other radio frequency source which is connected with a lower electrode at the lower end of the reaction chamber. The method comprises the following steps: forming a photoresist masking graphics on the surface of the HgCdTe device; fixing the HgCdTe device in the etching device, and then vacuumizing the etching device; and leading a mixed gas of argon, hydrogen and methane, and carrying out dry etching. In the mesa molding process of the two-color HgCdTe detector, the invention effectively reduces damage resulted from dry etching on the surface of thedeep mesa two-color device, thus significantly reducing leakage current on the surface of the side wall of the mesa of the two-color device, and solving a series of technical problems of the device such as poor electrical performance, low finished product rate and the like resulted from high surface damage in the mesa molding process of the two-color HgCdTe device.

Owner:11TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

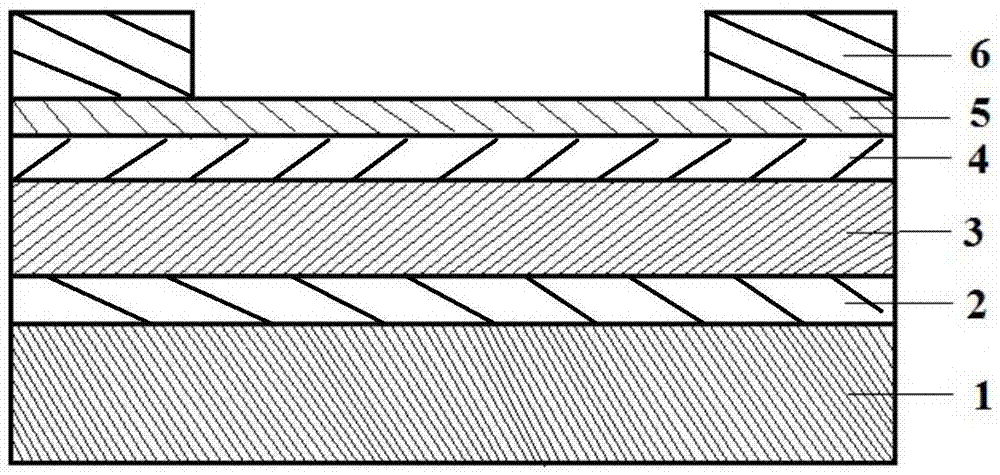

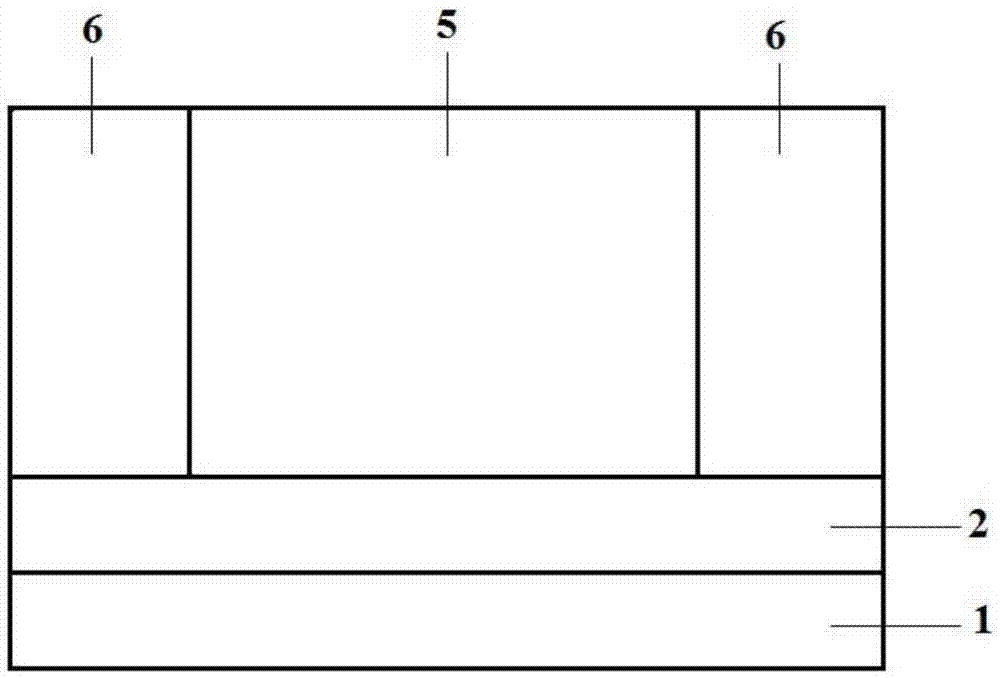

Double-active layer Cu2O/SnOp channel thin film transistor and preparation method thereof

InactiveCN105449000AImprove mobilityOptimize the valence band structureTransistorSemiconductor/solid-state device manufacturingSwitched currentOxygen vacancy

The invention belongs to the technical field of semiconductors, and discloses a double-active layer Cu2O / SnOp channel thin film transistor and a preparation method thereof. The thin film transistor comprises a substrate, a grid electrode, a grid insulating medium layer, a first semiconductor active layer, a second semiconductor active layer, a source electrode and a drain electrode from bottom to top, wherein the first semiconductor active layer is a p-type SnO semiconductor active layer and the second semiconductor active layer is a Cu2O semiconductor active layer. According to the p-type SnO semiconductor active layer, oxygen vacancy is imported to properly optimize the valence band structure, so that the hole migration rate is improved; and through depositing a layer of Cu2O membrane on the SnO active layer, the surface leakage current is decreased, the switch current ratio is improved, the influences on the SnO layer from the external oxygen and water are decreased and the device stability is improved.

Owner:SOUTH CHINA UNIV OF TECH

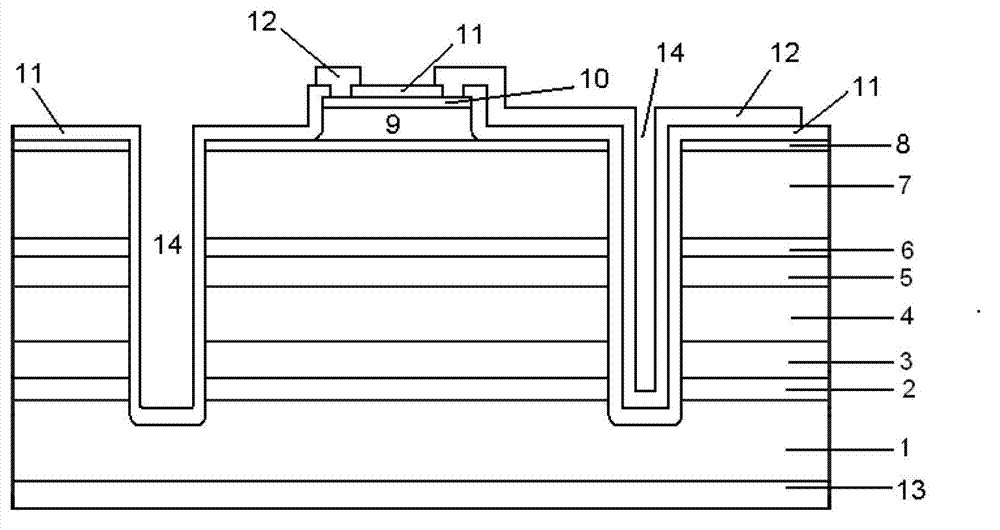

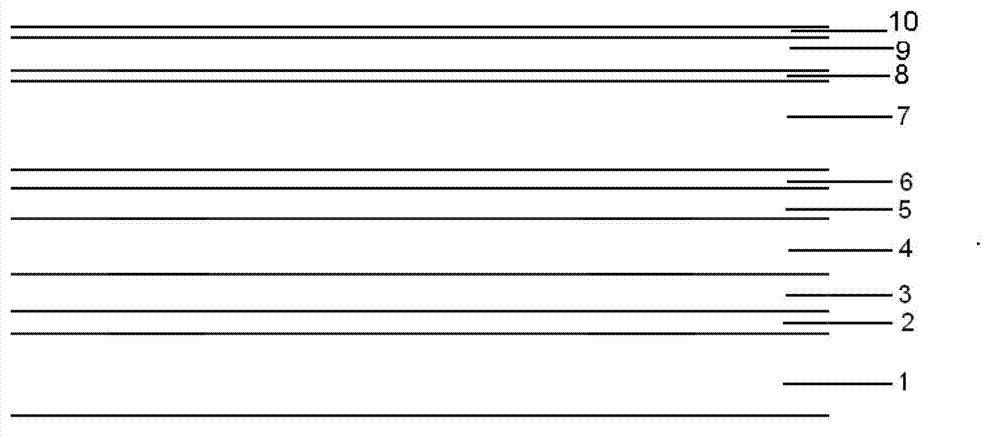

Monolithic integrated nBnBn four-waveband detector

The invention belongs to the technical field of semiconductor photoelectric detectors, and particularly relates to a monolithic integrated nBnBn four-waveband detector, which adopts a longitudinal integrated structure. The monolithic integrated nBnBn four-waveband detector comprises a GaSb substrate, an n-type short-wave channel ohmic contact layer, a first metal electrode layer, a short-wave channel absorption layer, a first barrier layer, a medium-wave channel absorption layer, an n-type medium-wave channel contact layer, a common electrode layer, a long-wave channel absorption layer, a second barrier layer, an ultra-long-wave channel absorption layer, an n-type ultra-long-wave channel contact layer, a second metal electrode layer and a passivation layer. The detector with four wave bands in the detector has an integrated structure from bottom to top, has a four-absorption-layer structure, can respectively detect the four wave bands through voltage control, has the advantages of highresponsivity, low dark current and the like, reduces the false alarm rate, reduces the size of a device, and reduces the complexity of a preparation process and a detection system.

Owner:TIANJIN JINHANG INST OF TECH PHYSICS

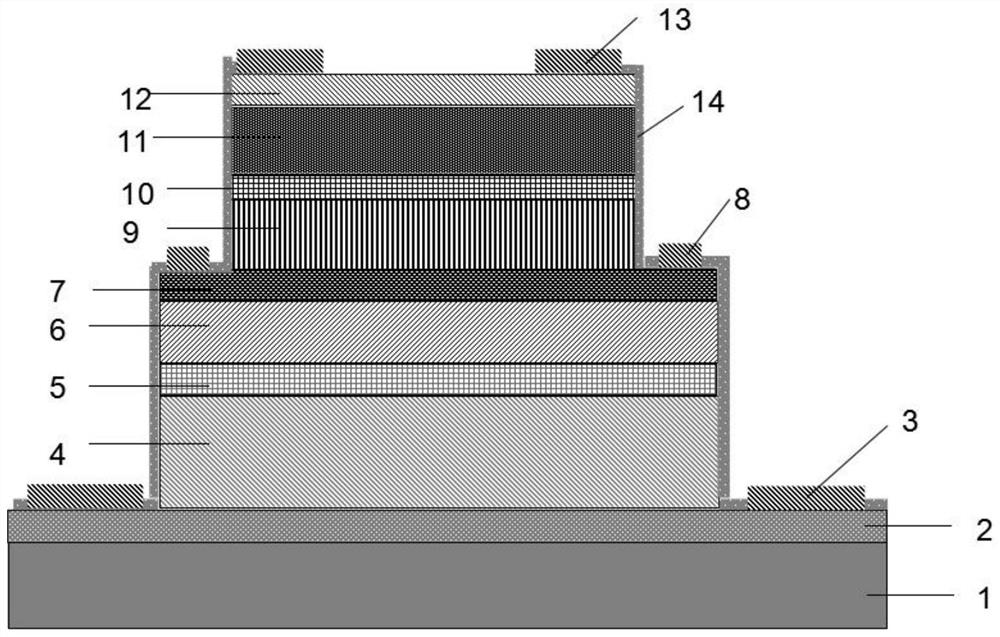

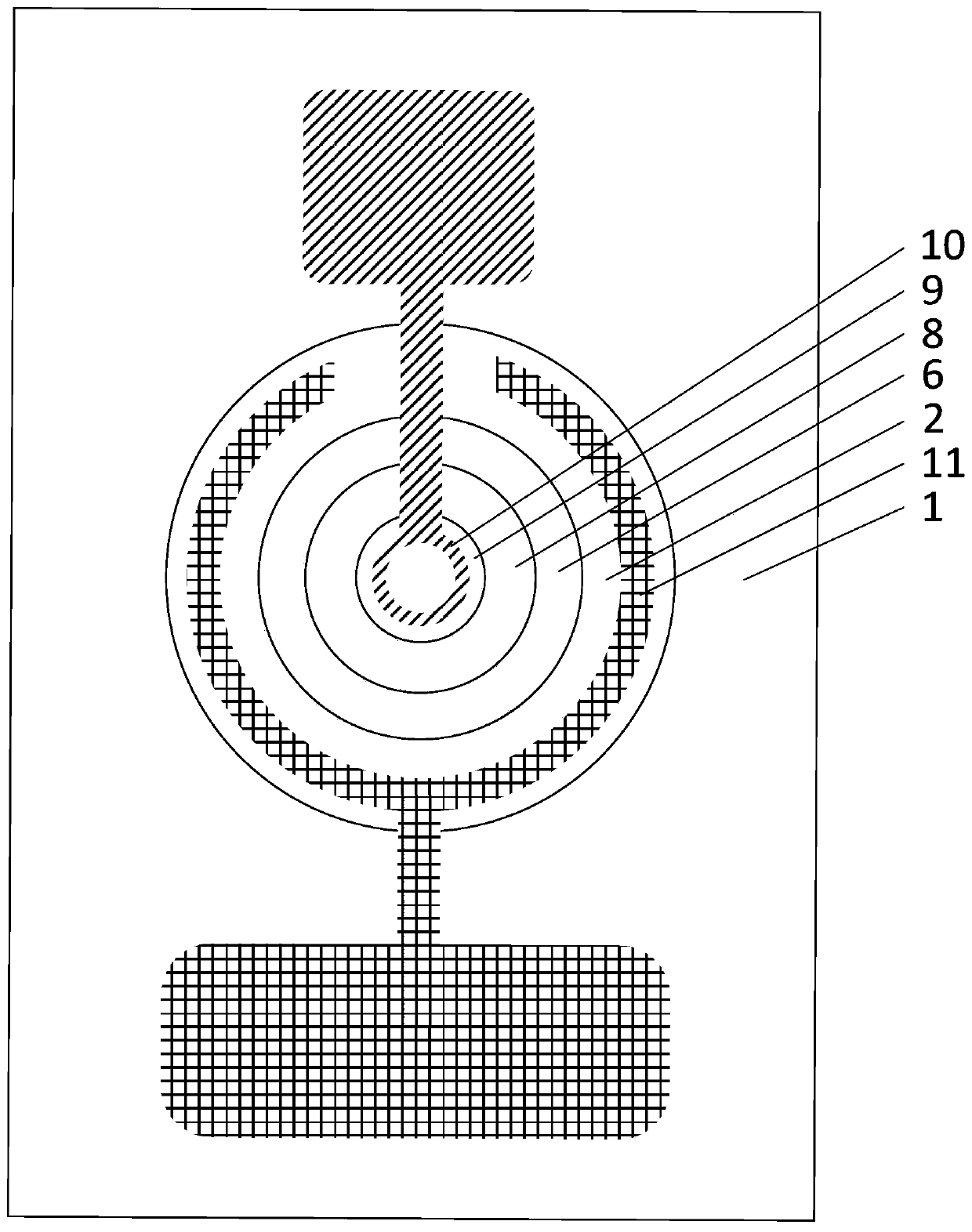

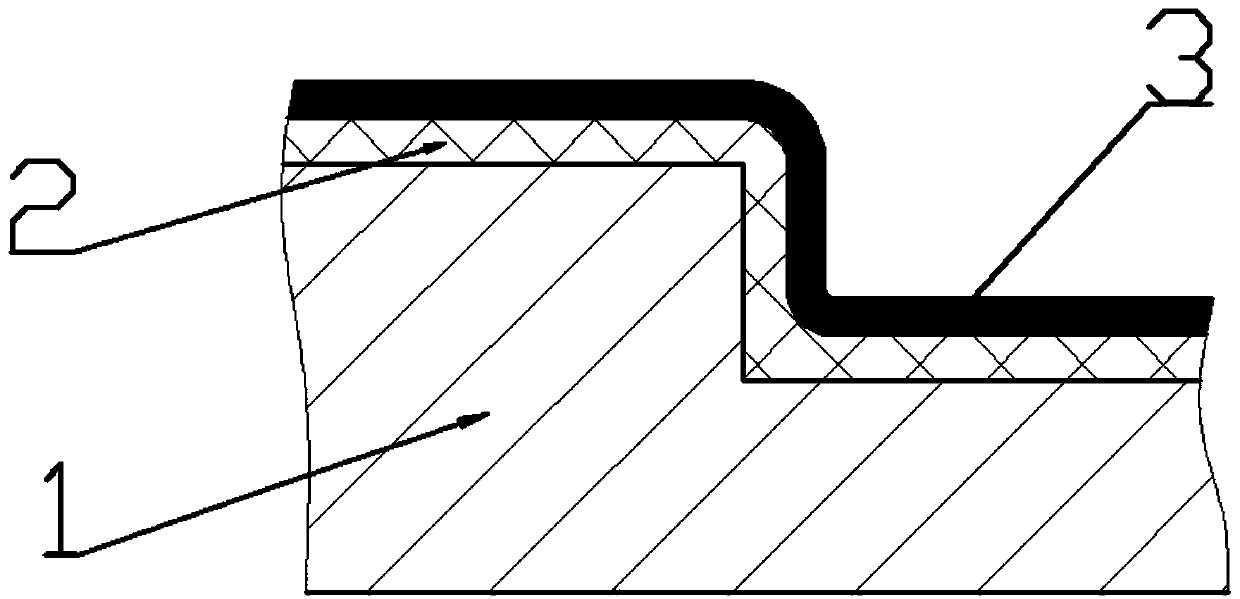

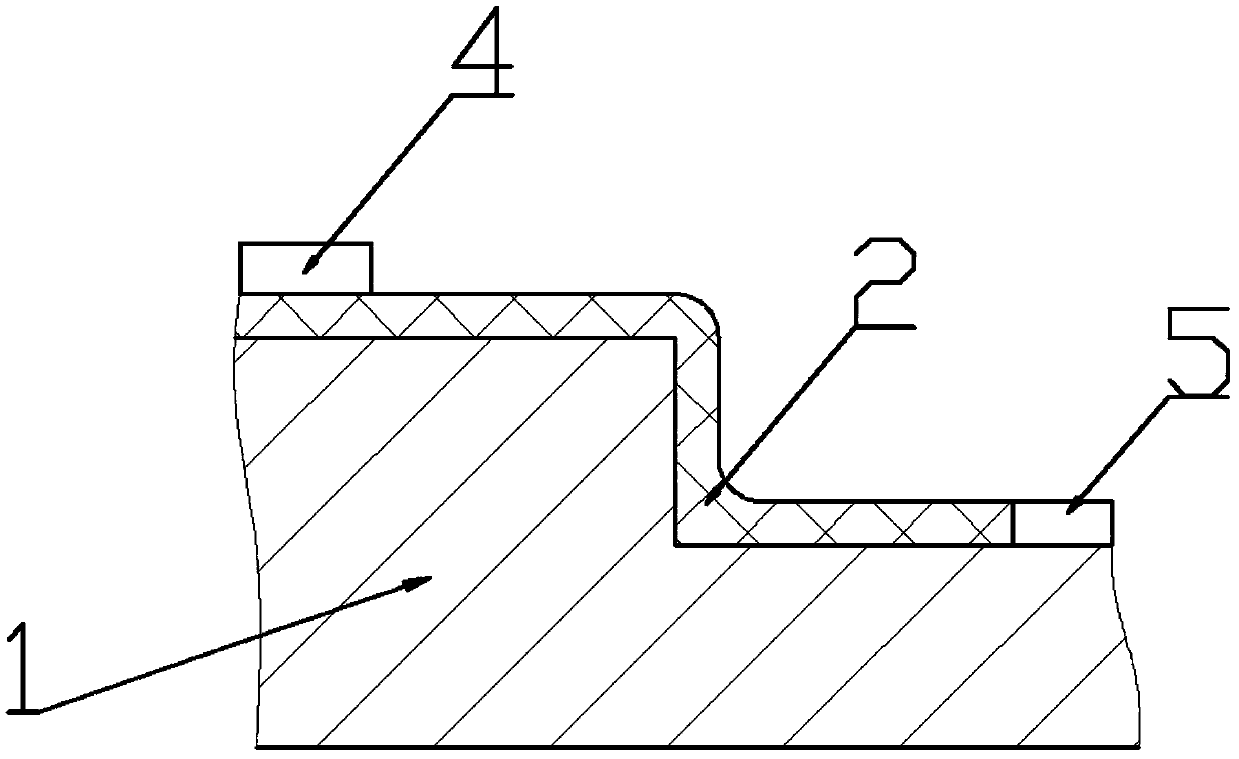

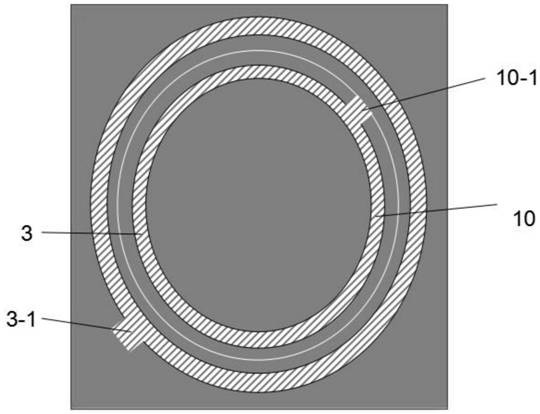

Diffusion-free avalanche photodiode and preparation method thereof

ActiveCN103094398ASimple designEasy to manufactureSemiconductor devicesControl layerSelective leaching

The invention provides a diffusion-free avalanche photodiode and a preparation method thereof. The avalanche photodiode comprises a substrate. A buffer layer, a diffusion impervious layer, an avalanche multiplication layer, an electric field control layer, a gradual change layer, a light absorption layer, a corrosion stop layer, a window layer and a contact layer sequentially grow on the surface of the substrate. The window layer is placed at the central position of the corrosion stop layer. Medium insulating layers of the corrosion stop layer are covered both on the periphery of the window layer and above the contact layer, and the medium insulating layers are provided with annular channels. The circular window layer is corroded by selectivity corrosion, the medium insulating layers are covered on the parts outside the window layer, the size of the window layer can directly define the light sensitive area of the avalanche photodiode, and so that the avalanche photodiode is suitable for working at different rate environments. In addition, although a slightly strong electric field exists on one side, close to the edge of the window layer, of the light absorption layer, edge punch-through can not occur on the avalanche multiplication layer.

Owner:WUHAN TELECOMM DEVICES

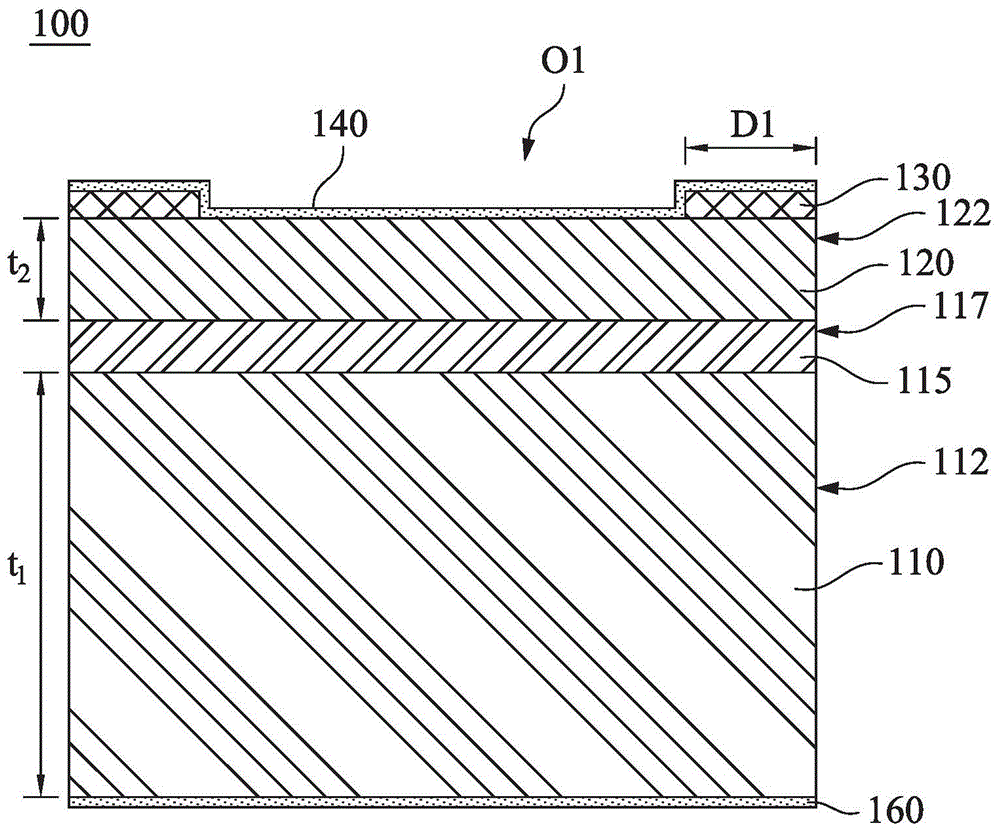

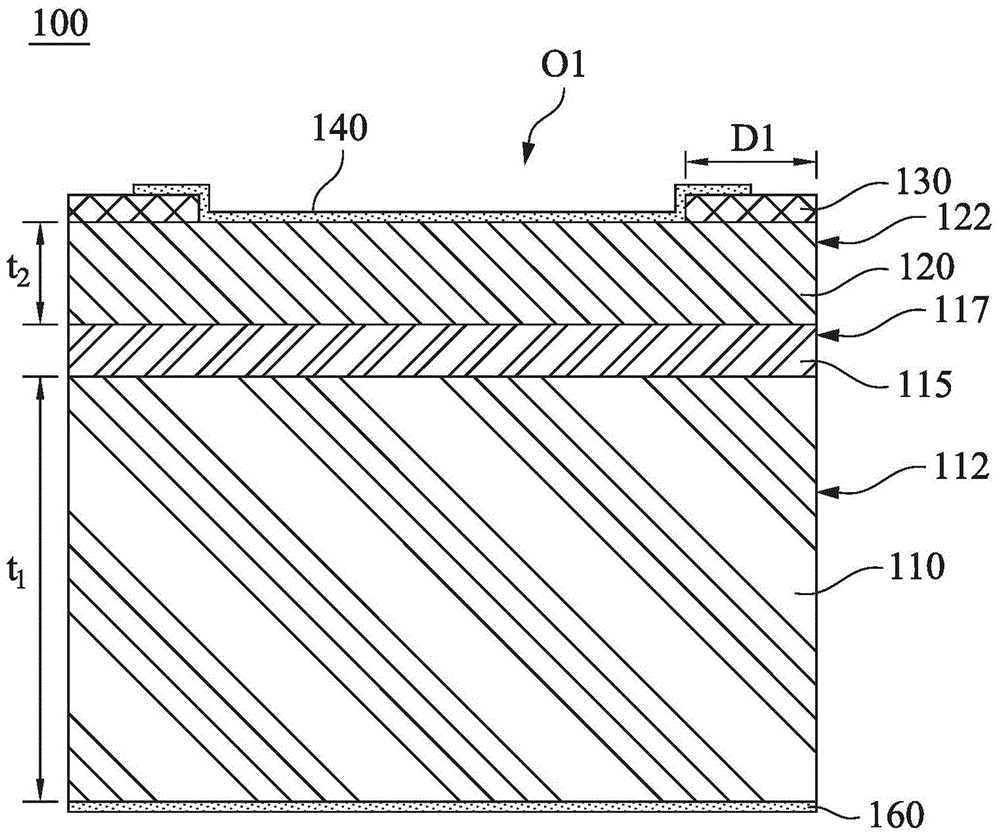

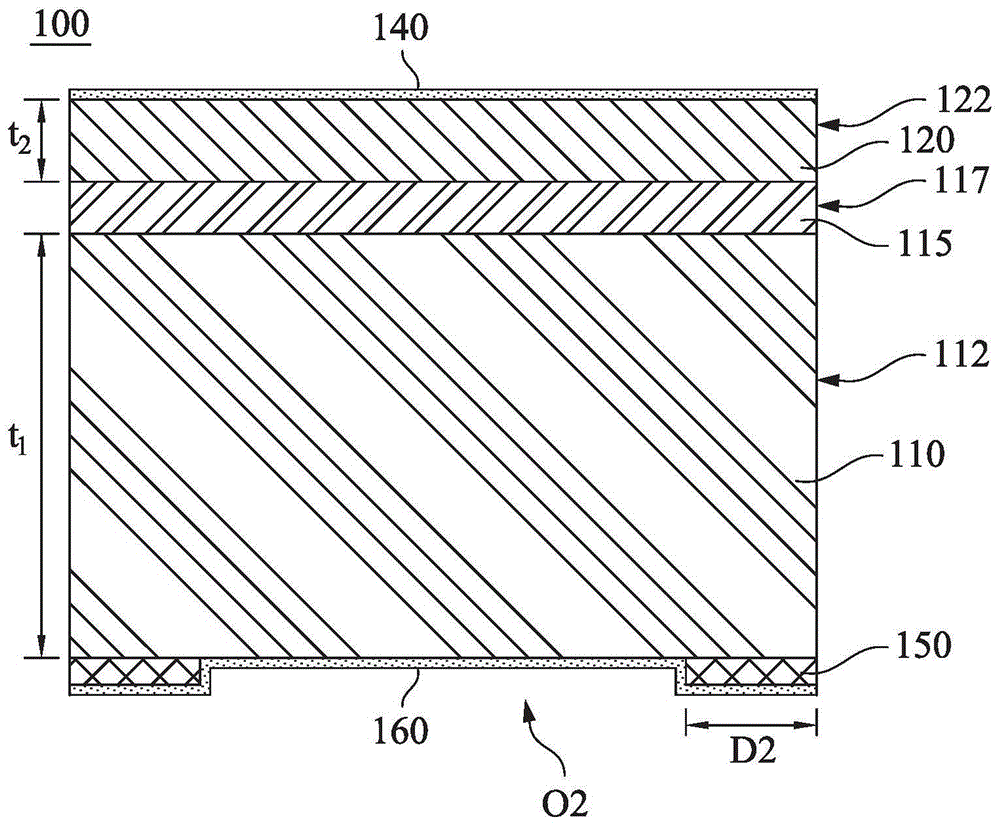

Micro-light-emitting diode

ActiveCN105355733AImprove luminous efficiencyIncrease current densitySemiconductor devicesShortest distanceShort distance

Owner:MIKRO MESA TECH

Novel microwave GaN transistor with high electron mobility

InactiveCN108807528APlay a buffer roleReduced frequency characteristicsSemiconductor devicesMicrowaveHigh electron

The invention provides a novel microwave GaN transistor with high electron mobility. The novel microwave GaN transistor with high electron mobility comprises a semi-insulation substrate, an aluminum nitride nucleating layer, a GaN buffer layer and AlGaN barrier layer which are arranged from bottom to top, wherein a source cap layer and a drain cap layer are arranged on the AlGaN barrier layer, a source electrode is arranged on an upper surface of the source cap layer, a drain electrode is arranged on a surface of the drain cap layer, a gate electrode is arranged between the source electrode and the drain electrode and is near to an end of the source electrode, a high gate is arranged between the source cap layer and the drain cap layer, an upper surface of the high gate is higher than a bottom surface by 5 nanometers, a left concave region is formed right below a part between the source electrode and the gate electrode and on an upper surface of the GaN buffer layer and is formed frompits, and a right concave region is formed right below a part between the drain electrode and the gate electrode and the upper surface of the GaN buffer layer and is formed from pits. By the novel microwave GaN transistor, the transconductance region of the device is improved, the saturation output power of the device is increased, and the DC characteristic and the frequency characteristic of thedevice are improved.

Owner:XIDIAN UNIV

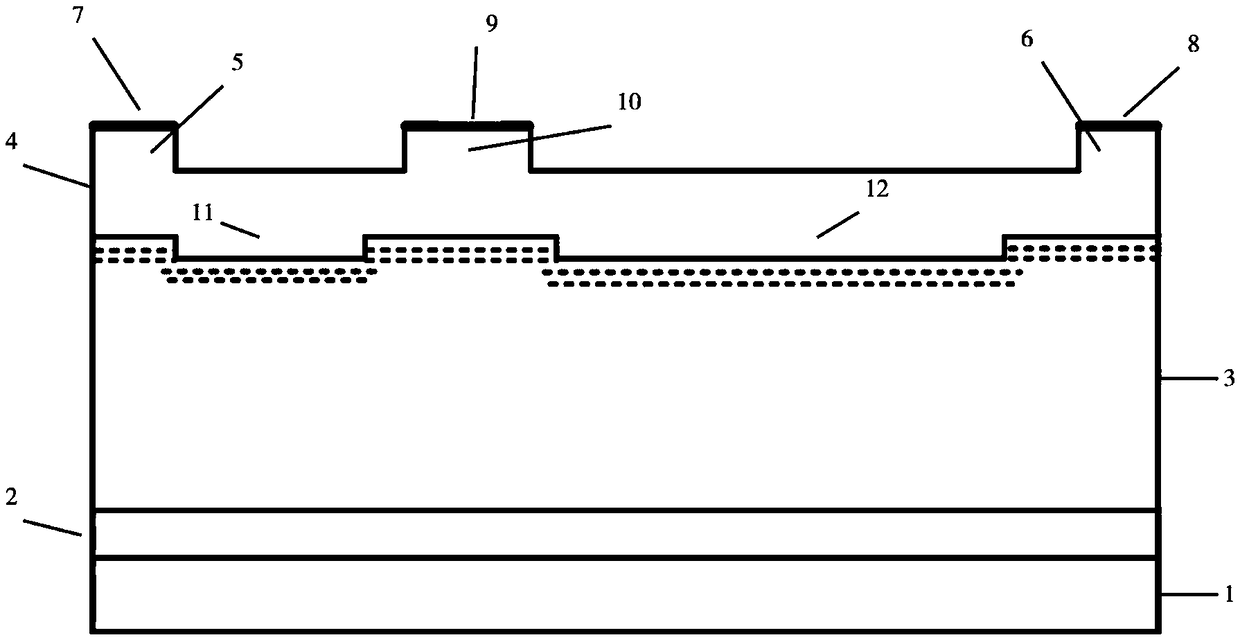

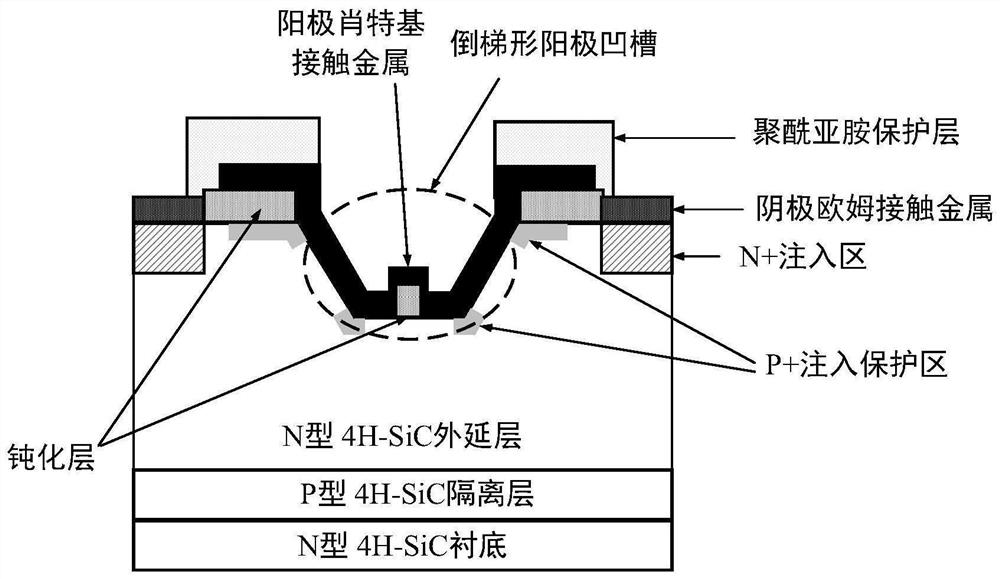

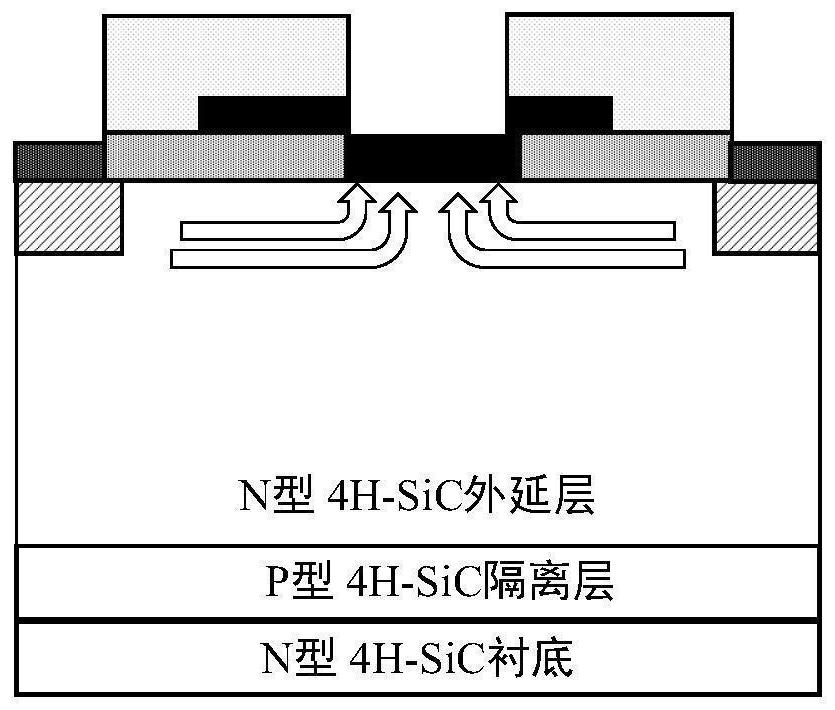

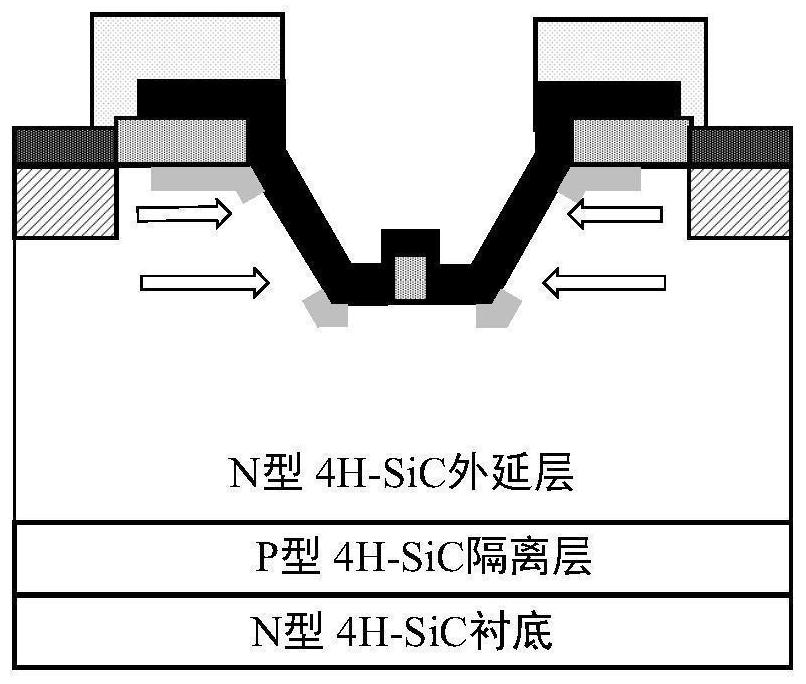

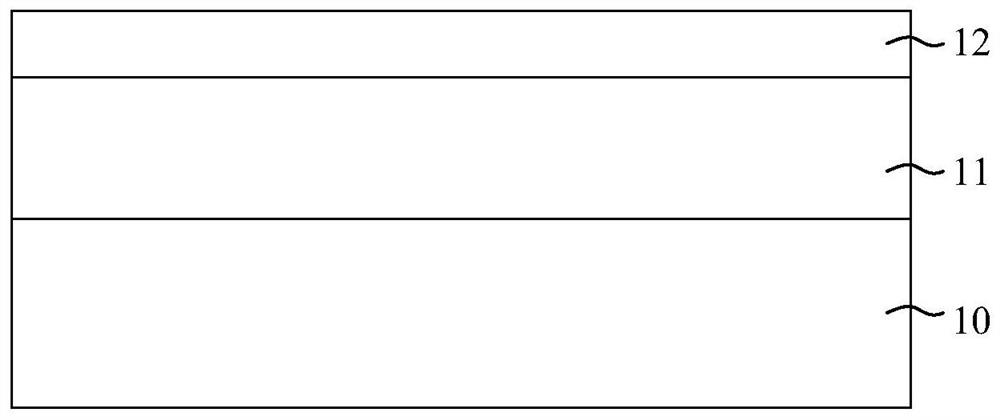

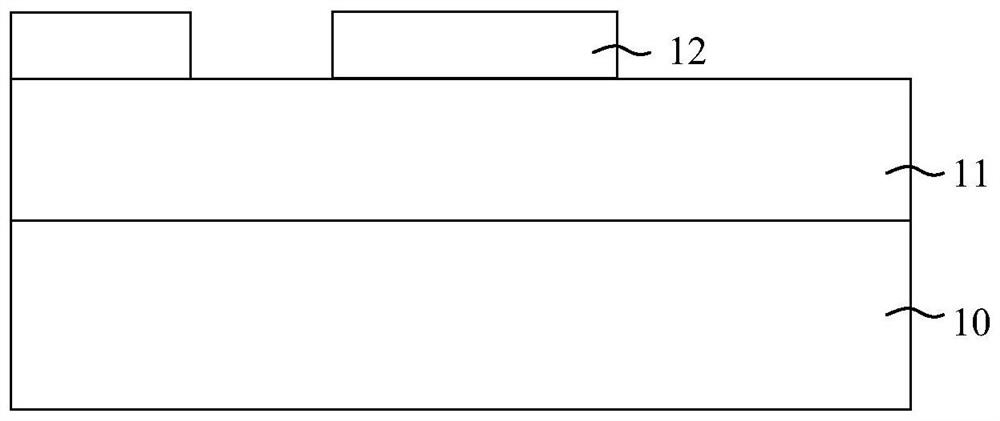

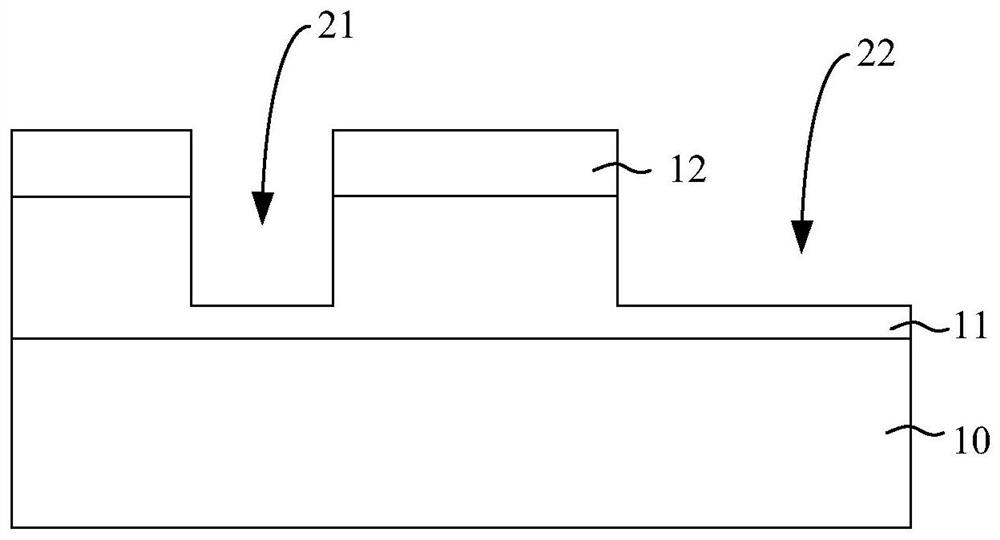

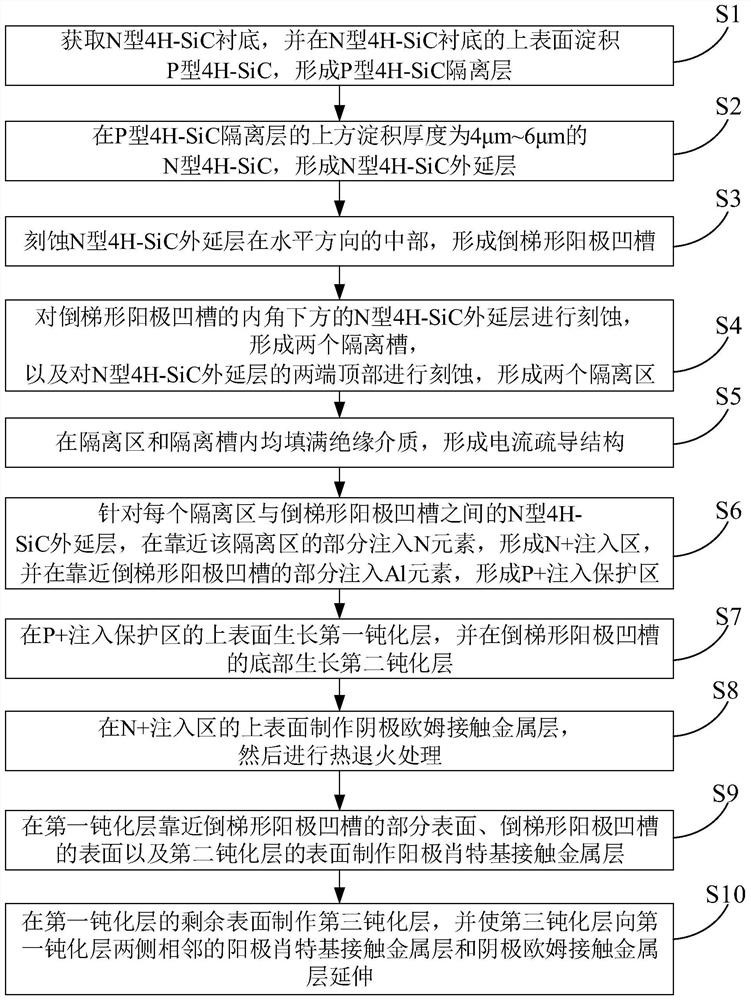

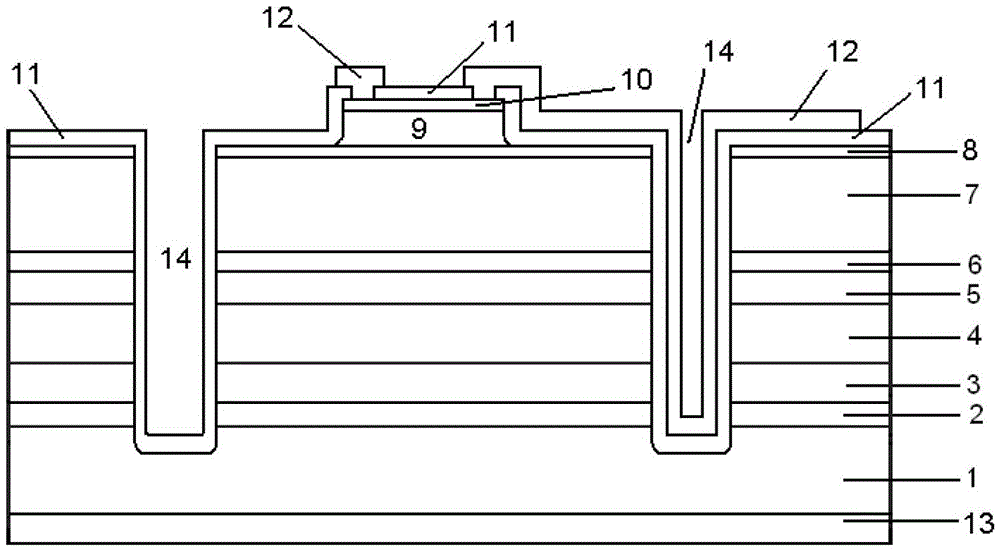

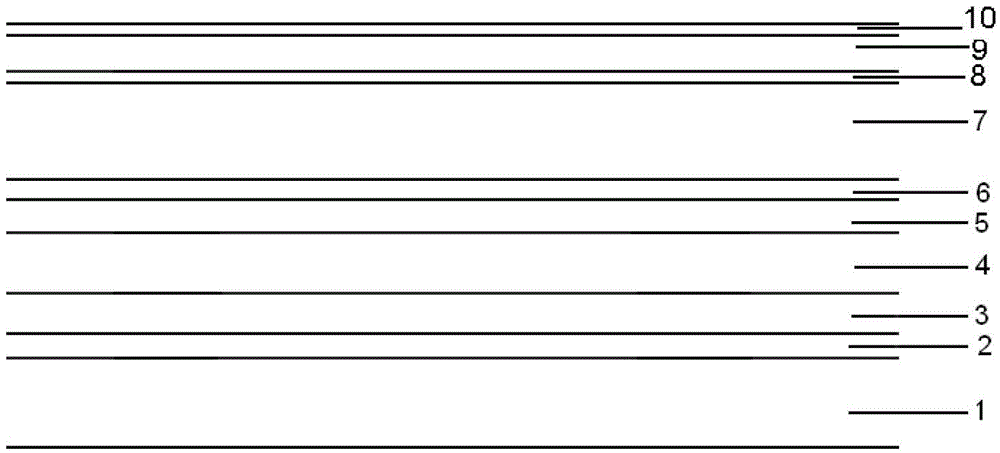

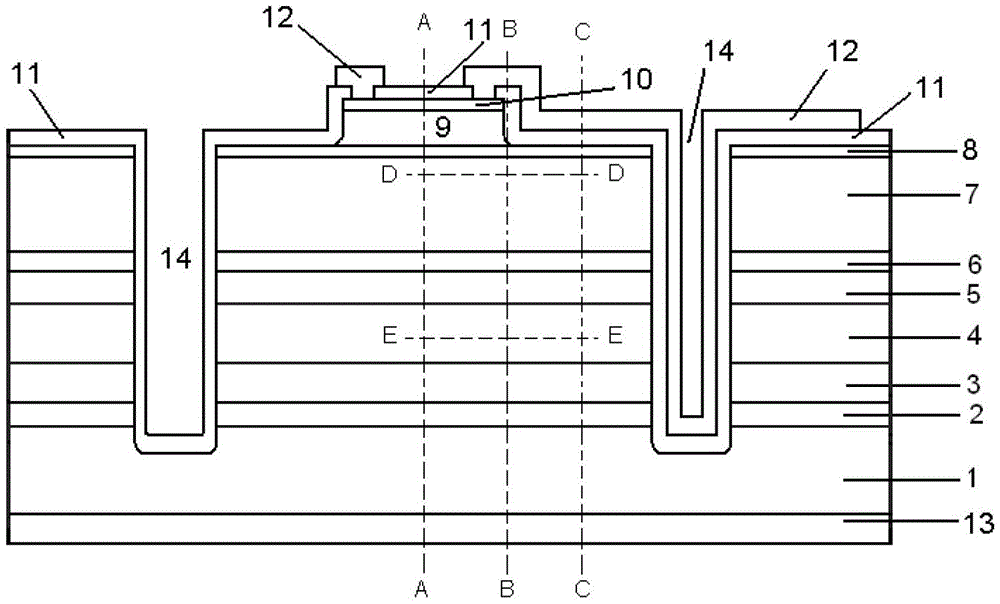

SiC Schottky power diode and production method thereof

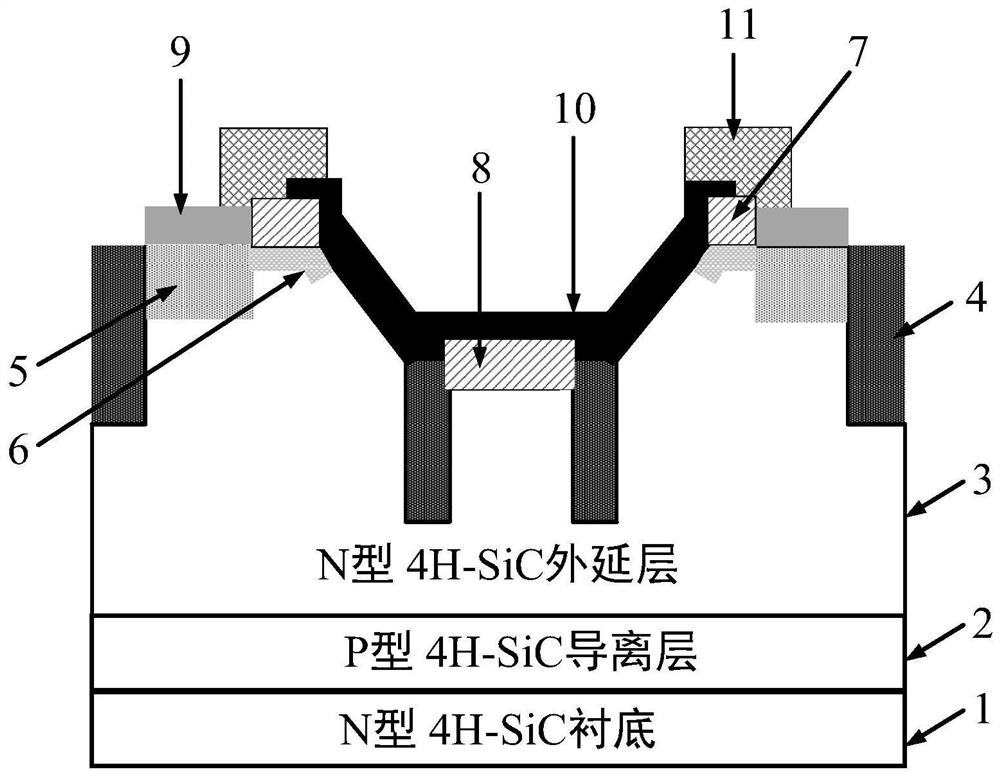

PendingCN113964208AReduce surface leakage currentImprove reverse characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactPower diode

The invention discloses a SiC Schottky power diode. The SiC Schottky power diode comprises an N-type 4H-SiC substrate, a P-type 4H-SiC isolation layer and an N-type 4H-SiC epitaxial layer from bottom to top, and the thickness of the epitaxial layer is less than 6 microns; cathode ohmic contact metal is included and positioned on two sides of the upper surface of the epitaxial layer, and an N + injection region is arranged on the epitaxial layer below the cathode ohmic contact metal; an inverted trapezoidal anode groove is included and p + injection protection regions are arranged on the epitaxial layer around the four inner corners of the inverted trapezoidal anode groove; a passivation layer is included, the first part of the passivation layer is deposited on the upper surface, which is not etched and not covered by the cathode ohmic contact metal, of the epitaxial layer, and the second part of the passivation layer is deposited in the middle of the bottom of the inverted trapezoidal anode groove; and the inverted trapezoidal anode groove, the first portion of the passivation layer, and the second portion of the passivation layer cover the anode Schottky contact metal. According to the invention, the productization of the 4H-SiC Schottky power diode with the high voltage of more than 3000V is realized.

Owner:瑶芯微电子科技(上海)有限公司

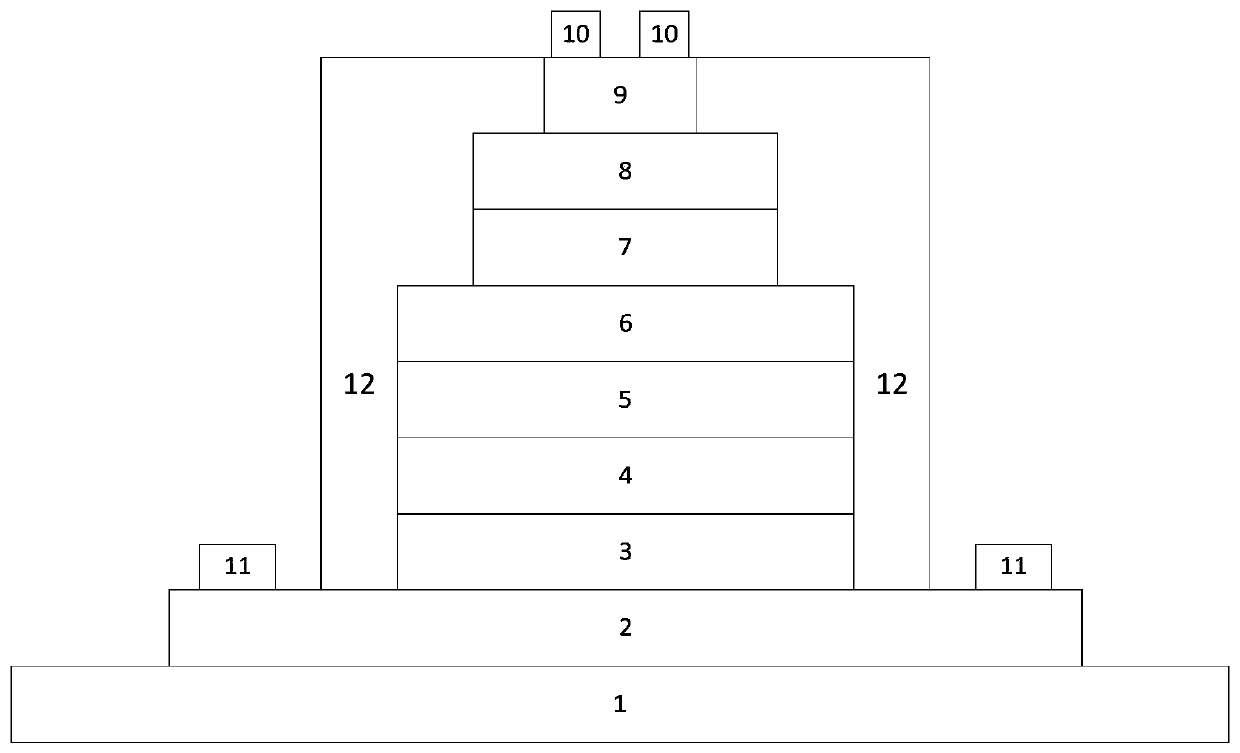

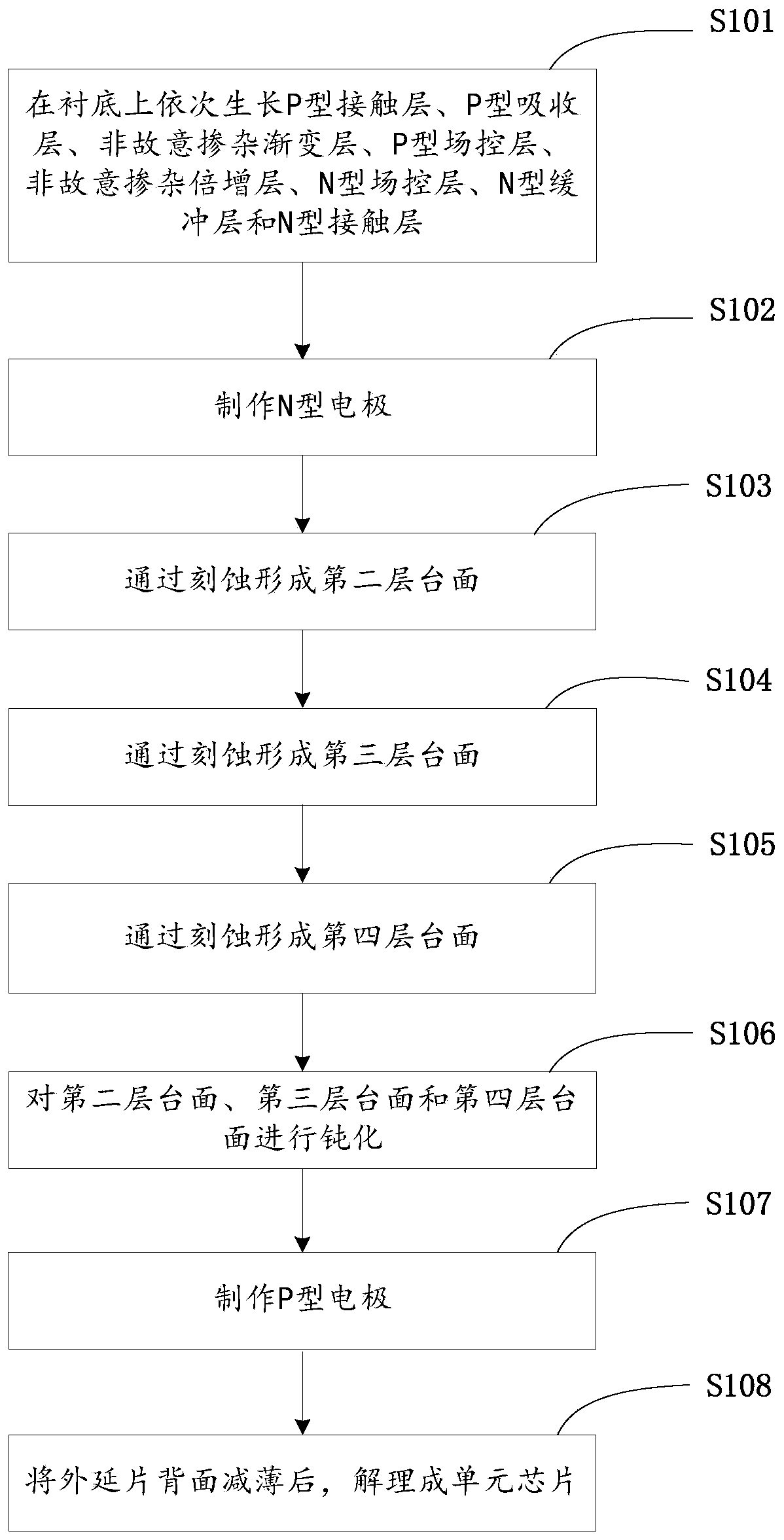

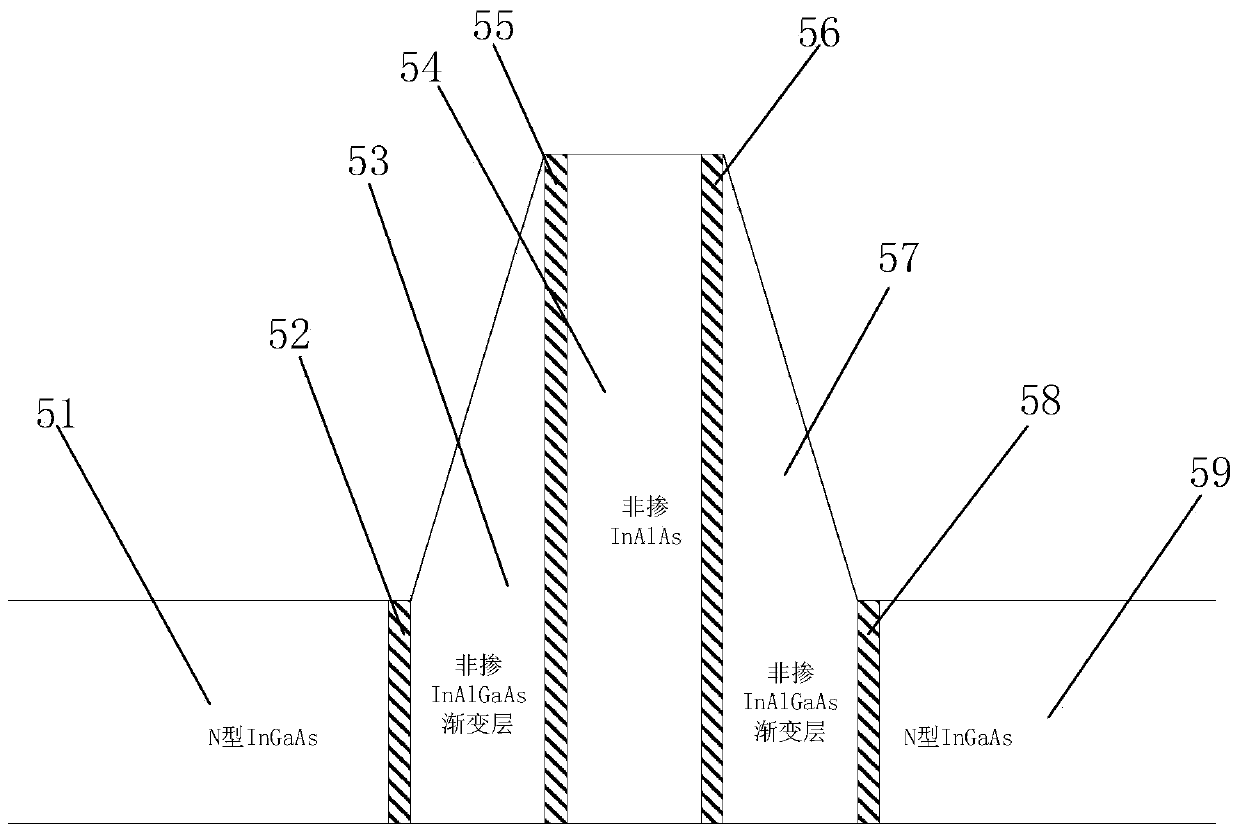

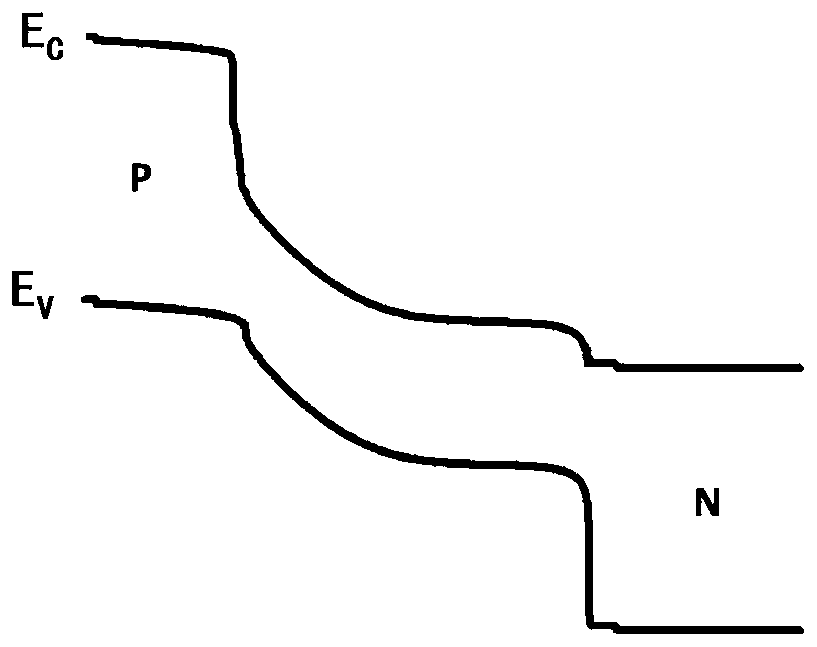

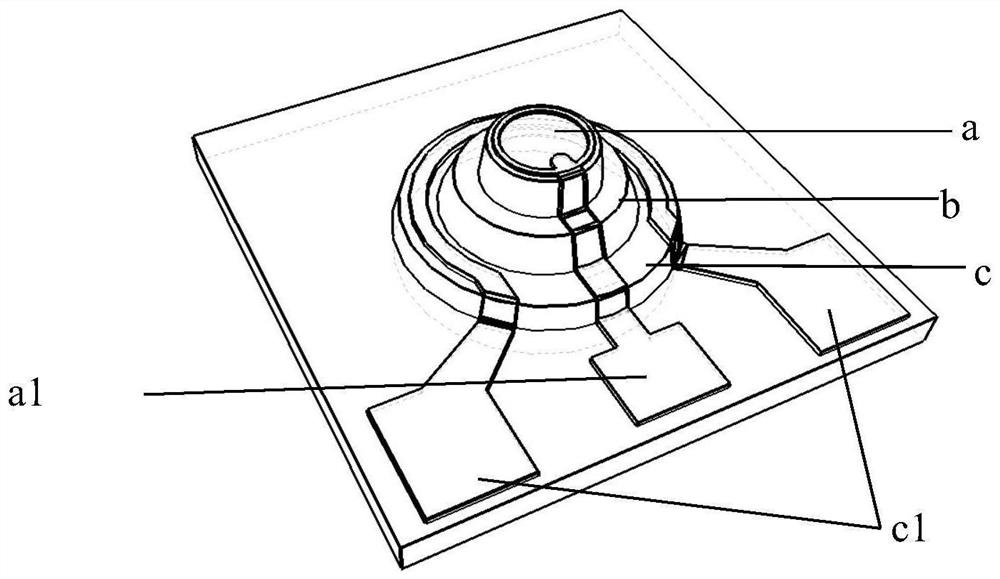

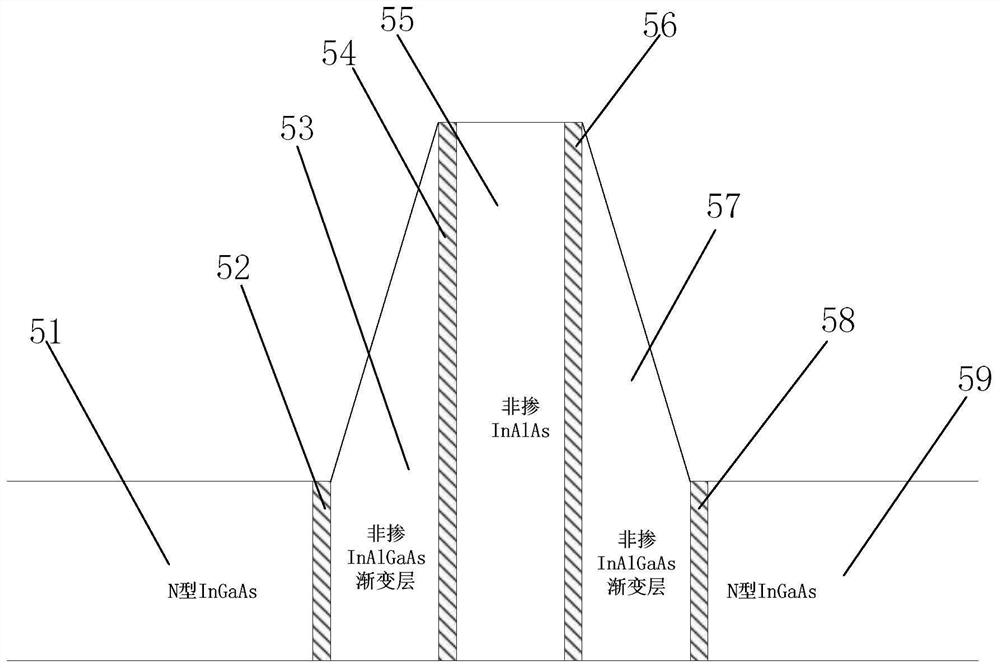

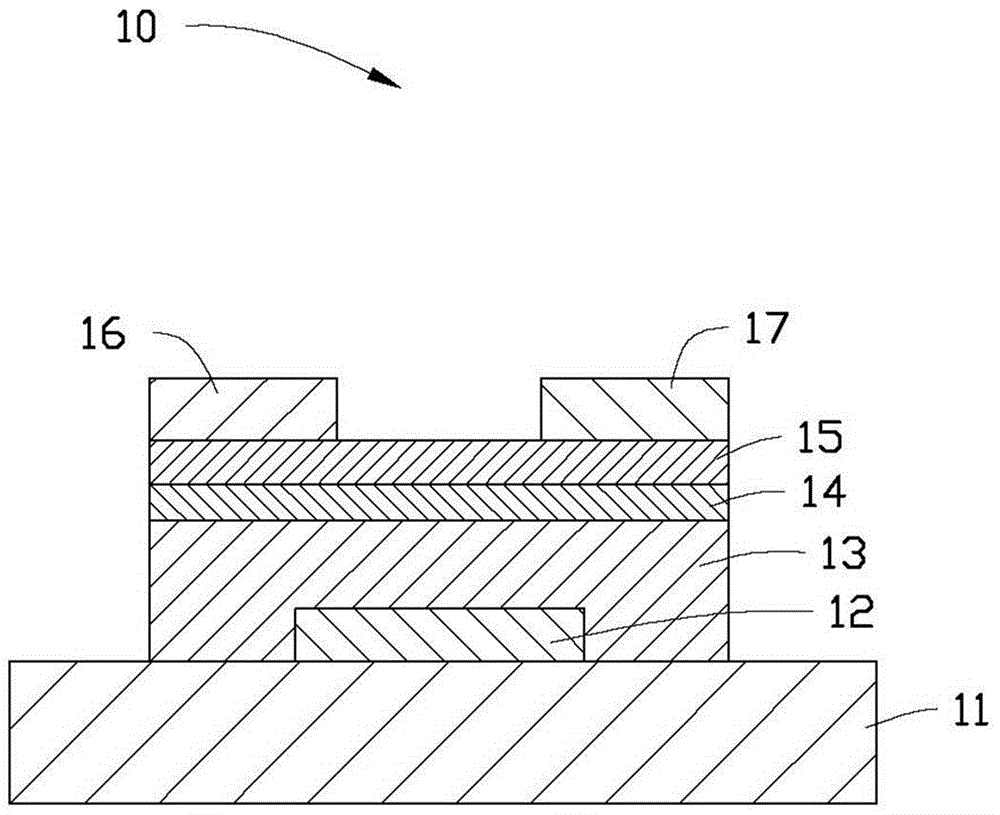

Single-electron transmission avalanche photodiode structure and manufacturing method

ActiveCN111312835AHigh frequencyImprove featuresFinal product manufactureSemiconductor devicesSingle electronElectron hole

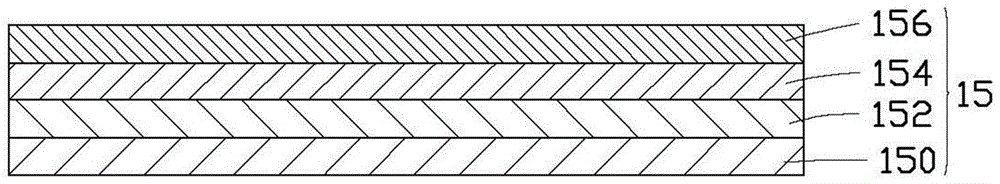

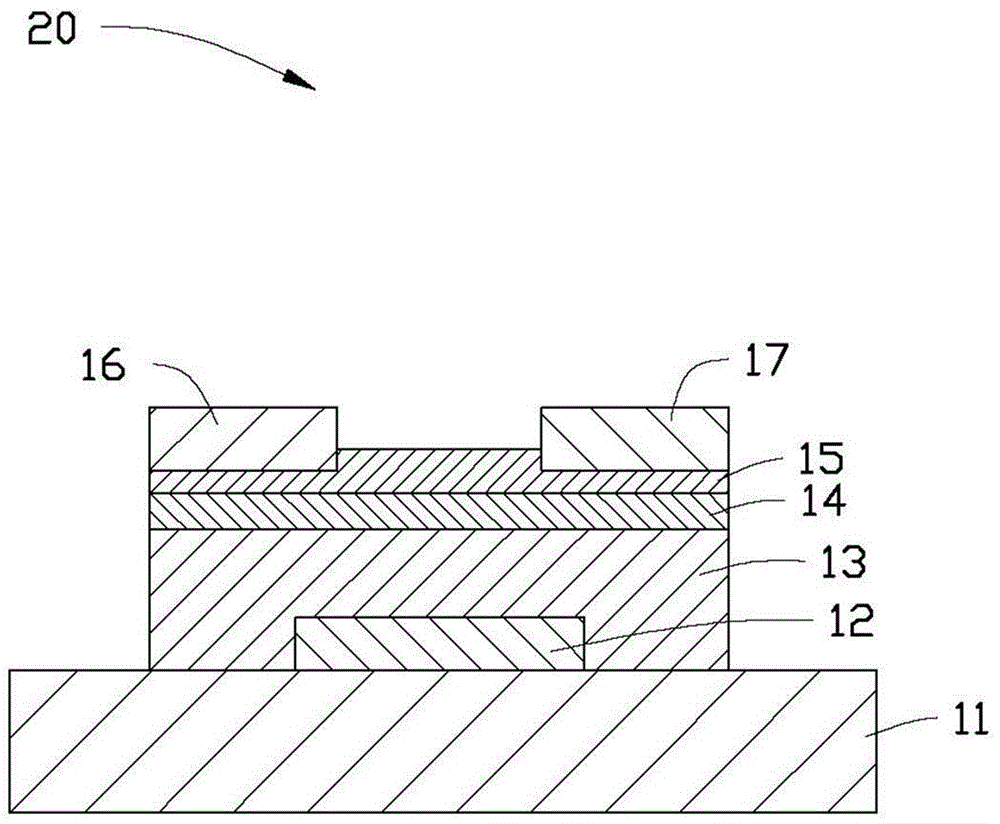

The invention discloses a single-electron transmission avalanche photodiode structure including a substrate, a P-type InAlGaAs contact layer, a P-type InGaAs absorption layer, an unintentionally dopedInGaAlAs gradient layer, a P-type InAlAs field control layer, an unintentionally doped InAlAs multiplication layer, an N-type InAlAs field control layer, an N-type InAlAs buffer layer and an N-type InGaAs contact layer are grown on the substrate in sequence. The invention also discloses a manufacturing method of the single-electron transmission avalanche photodiode structure, another single-electron transmission avalanche photodiode structure and a manufacturing method thereof. According to the invention, the InGaAs absorption layer is designed to be P-type doped, photo-generated holes are majority carriers, the photo-generated holes participate in carrier transmission in a relaxation process, only electrons are generated in carrier migration, and the frequency and saturation characteristics of a device are greatly improved through the electrons with high mobility.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

Silicon solar cell with hot spot laser etching ring and preparing method thereof

InactiveCN100559613CReduce scrap rateReduce manufacturing costFinal product manufacturePhotovoltaic energy generationLaser etchingOptoelectronics

The invention relates to a silicon solar energy cell with hot spot laser etching ring. A metal electrode layer and a Pn joint layer are on a surface. The hot spots are on a surface of the cell. A laser etching ring is arranged in periphery of the hot spot, separating the metal electrode or penetrating the Pn joint in depth. The preparation method is: finding out position and size of the hot pot on the surface of the silicon solar cell with the hot spot and marking; coating a refrigerant on periphery of the hot spot or refrigerating the cell; etching a circle on the periphery of the hot spot by the laser beam to form the laser etching ring, separating the metal electrode or penetrating the Pn joint in depth; separating the Pn joints on other parts of the hot spot and the cell. Because the laser etching ring separates the hot spot and the metal electrode and the Pn joint, the drainage current caused by the hot spot is extremely reduced, even eliminated, which reduces a defective index in cell production and cost of production.

Owner:CHINA SUNERGY CO LTD

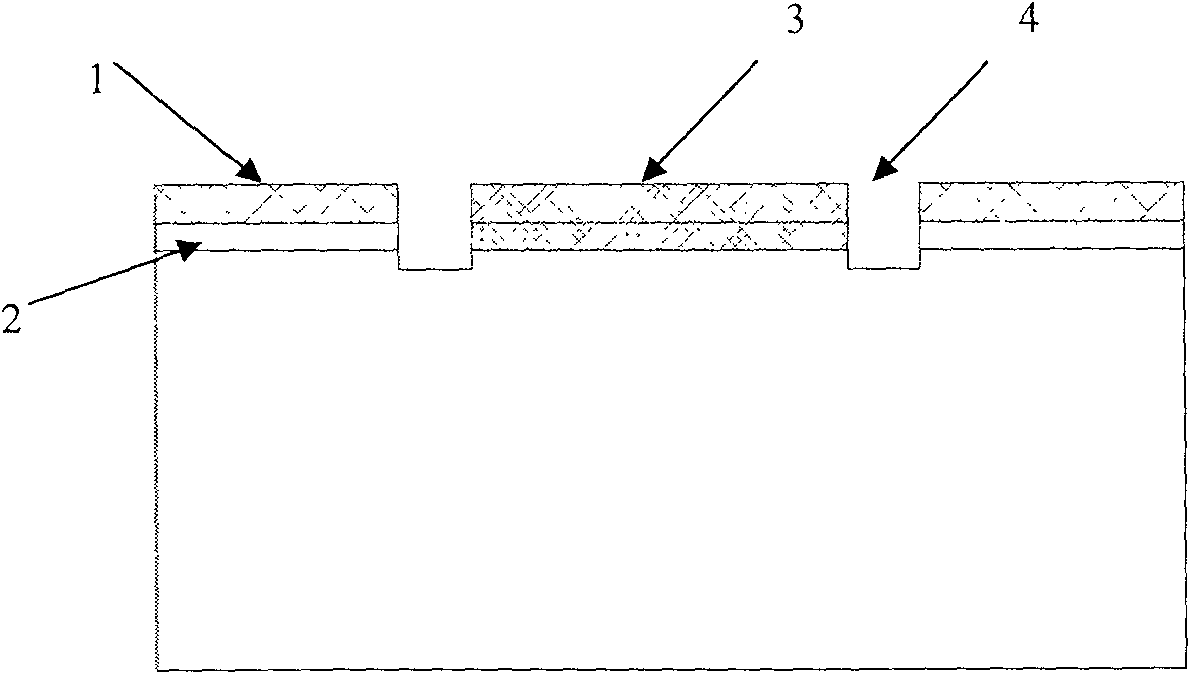

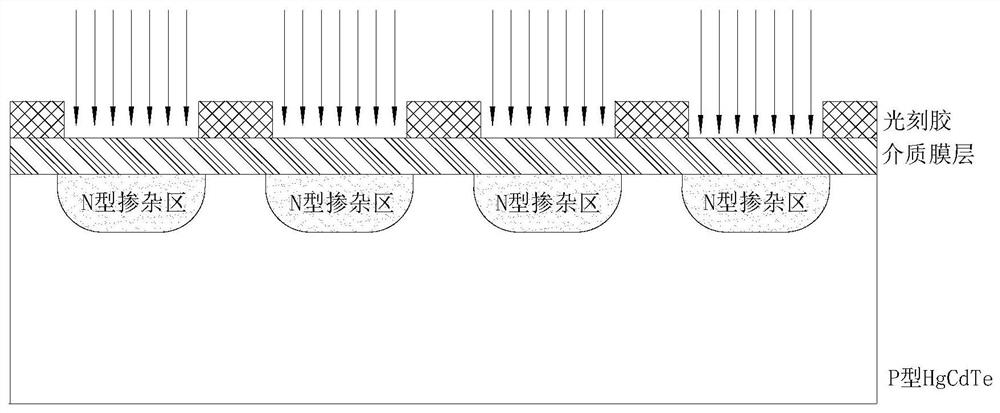

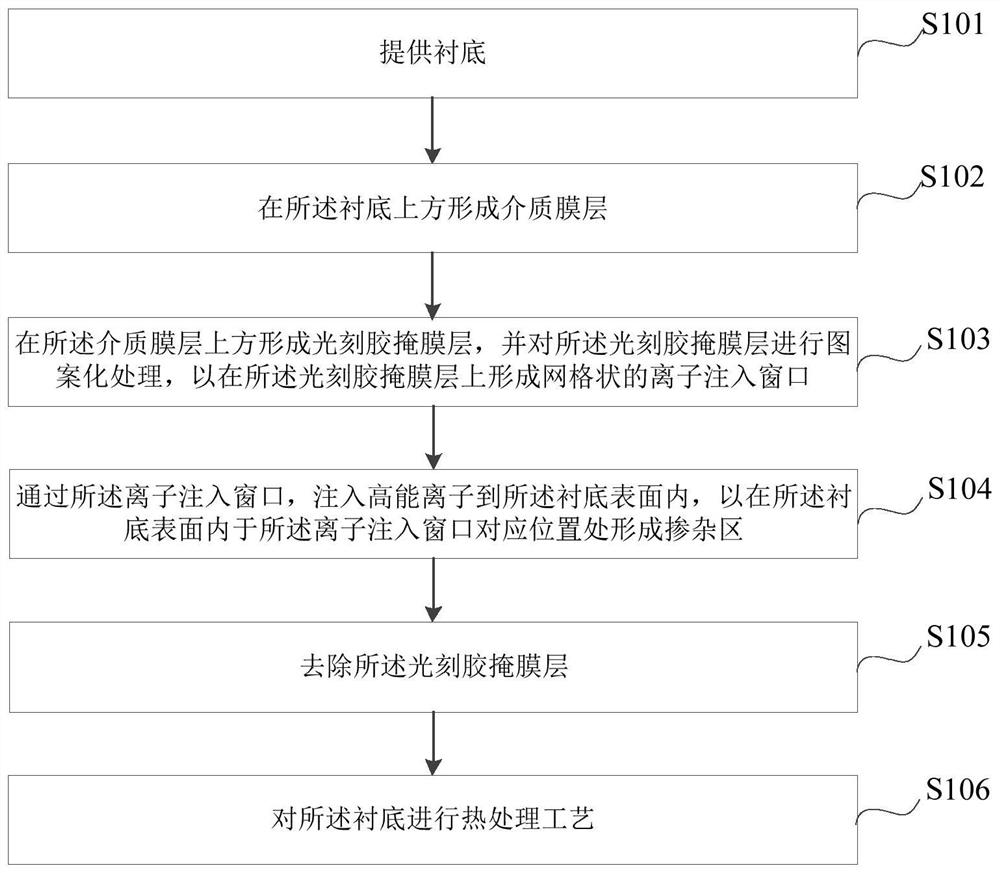

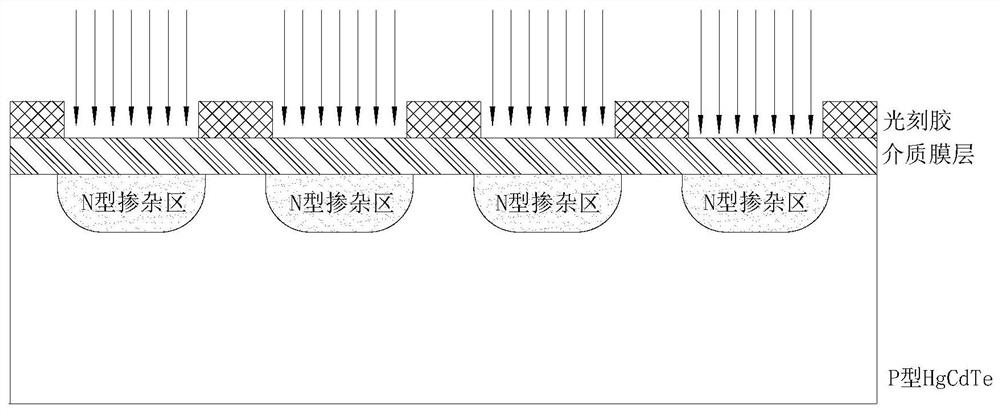

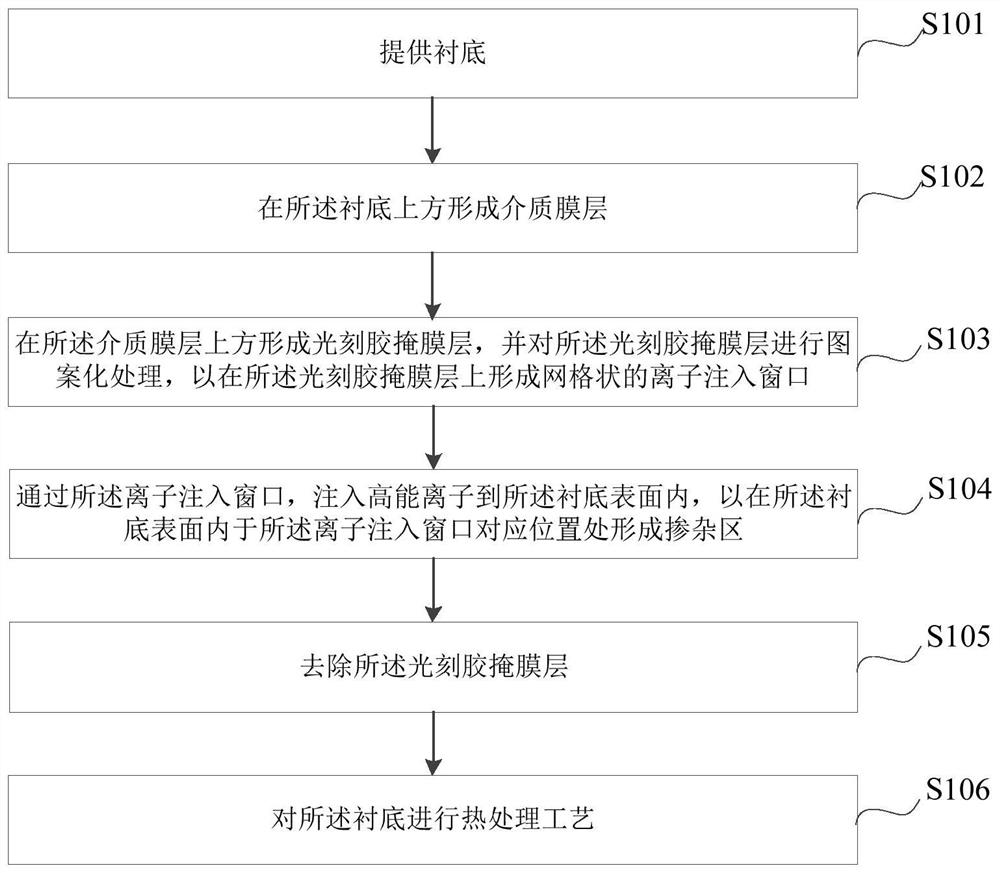

Ion implantation method, preparation method of mercury cadmium telluride chip, and mercury cadmium telluride chip

ActiveCN112086363BAvoid damageLow densityFinal product manufactureSemiconductor/solid-state device manufacturingMercury cadmium tellurideEngineering

The disclosure provides an ion implantation method, a method for preparing a mercury cadmium telluride chip, and a mercury cadmium telluride chip. The preparation method for the mercury cadmium telluride chip includes: forming a dielectric film layer on the P-type mercury cadmium telluride substrate; The P-type mercury cadmium telluride substrate and the dielectric film layer are subjected to a heat treatment process; a photoresist mask layer is formed above the dielectric film layer, and the photoresist mask layer is patterned to A grid-shaped ion implantation window is formed on the photoresist mask layer; through the ion implantation window, high-energy ions are implanted into the surface of the P-type HgCdTe substrate, so that the P-type HgCdTe Forming an N-type doped region in the surface of the mercury substrate; removing the photoresist mask layer; performing a heat treatment process on the P-type HgCdTe substrate. This method effectively protects the dielectric film layer in the implantation region that is not bombarded by high-energy ions, and reduces the damage to the good interface formed by heat treatment between the dielectric film layer and HgCdTe.

Owner:北京智创芯源科技有限公司

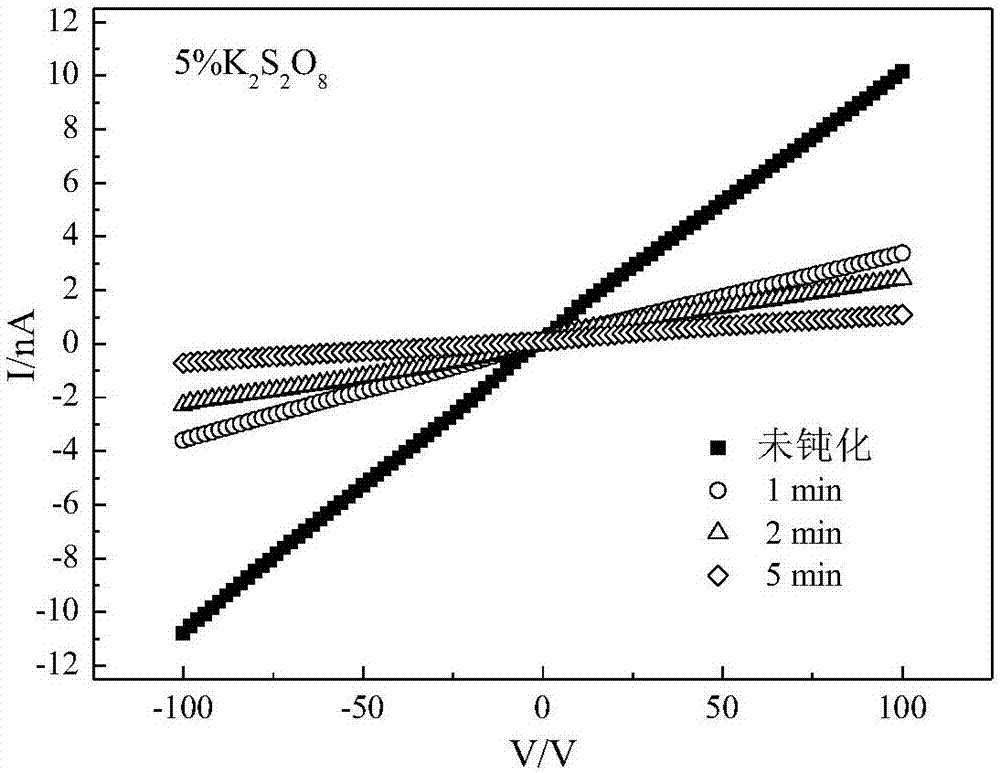

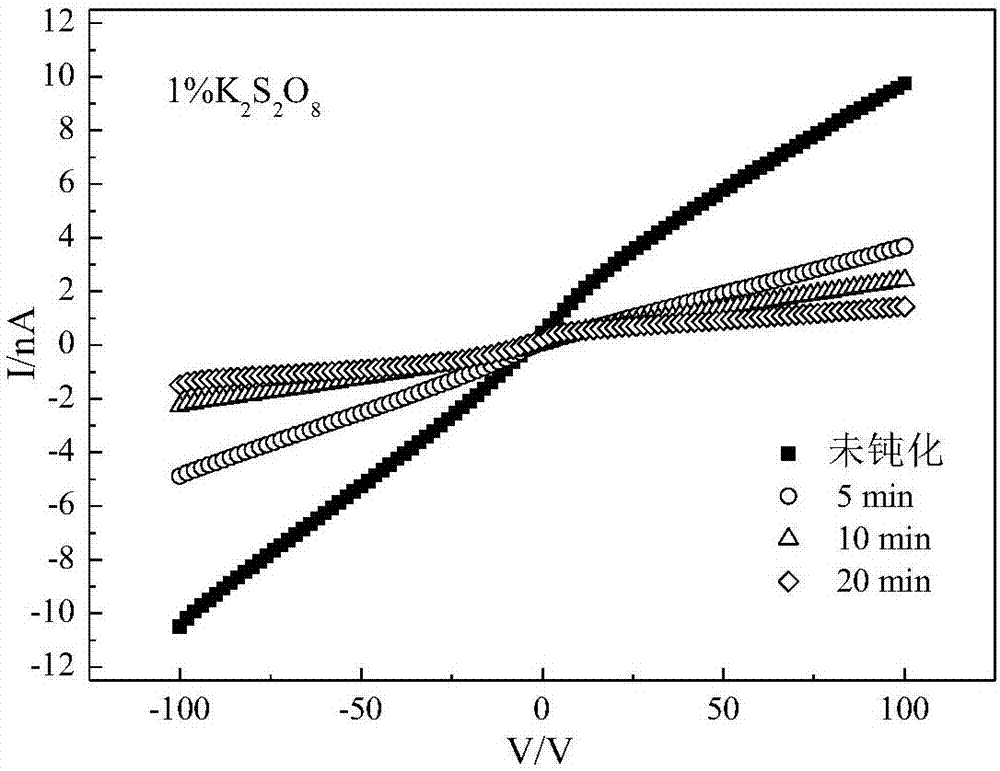

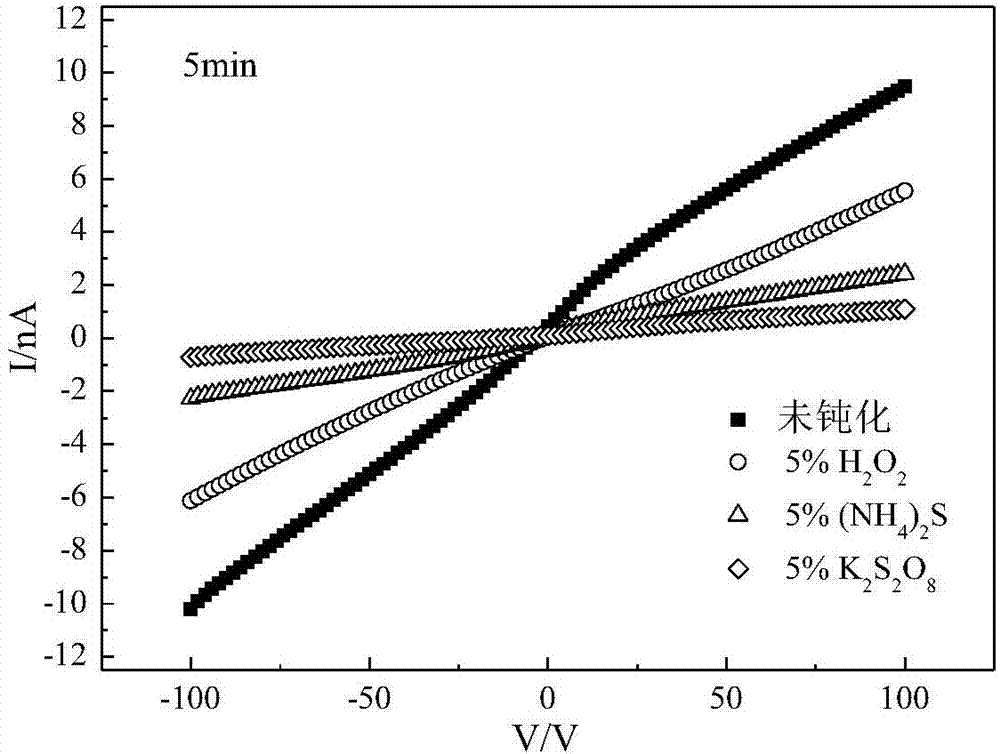

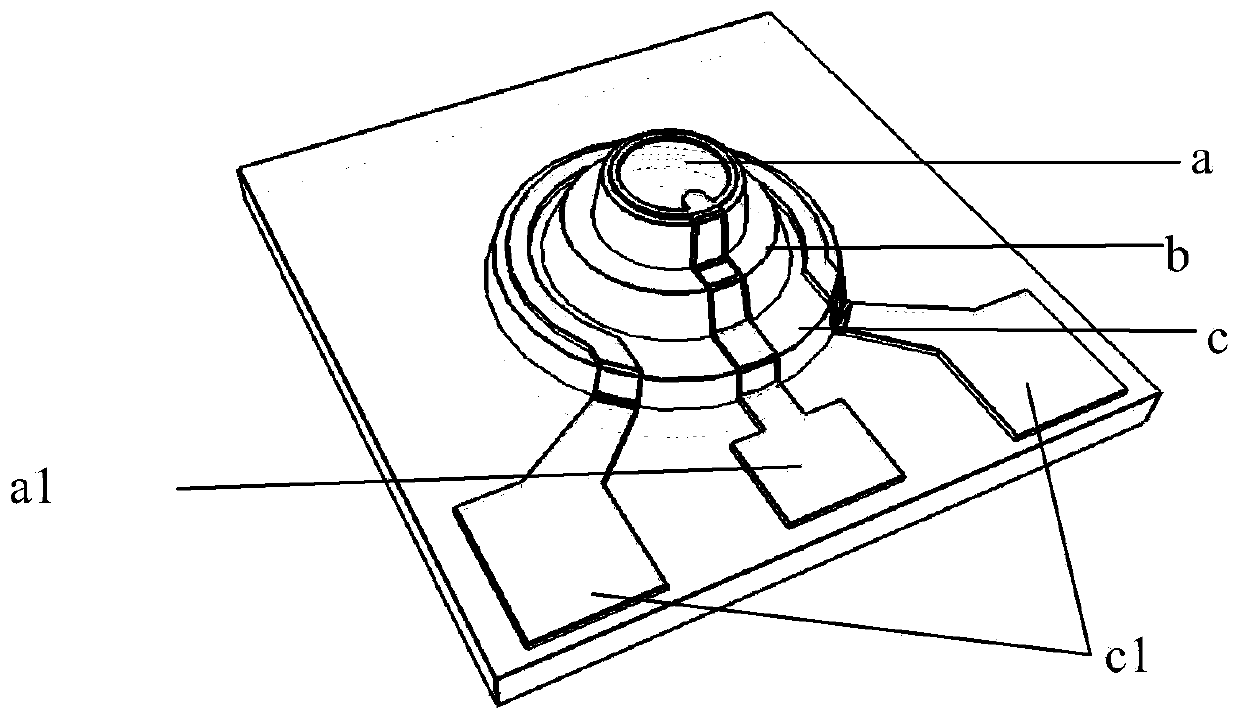

Surface passivation liquid and application of surface passivation liquid to CMT crystal surface passivation

ActiveCN107393820AReduce surface leakage currentSimple processSemiconductor/solid-state device manufacturingSemiconductor devicesPotassium persulfateHigh resistance

The invention relates to surface passivation liquid and application of the surface passivation liquid to surface passivation of CMT crystal. The mass percent content of the passivation liquid is 1%-5% potassium persulfate passivation liquid, namely a mass ratio of the potassium persulfate and de-ionized water is 1:99-5:95. When the passivation liquid is applied, a CMT crystal plate of which two surfaces are plated with gold electrodes through a chemical method is placed into the prepared passivation liquid for passivation for 1-20min, and then the CMT crystal plate is cleaned up by the de-ionized water and finally is dried through nitrogen, thereby obtaining the surface passivated CMT crystal. According to the surface passivation liquid and the application, the passivation technology and operation are simple, and the cost is low. After the CMT crystal is passivated, a high-resistance oxide layer can be formed on the surface of the CMT crystal and a leakage current is effectively reduced, so the performance of a detector is improved.

Owner:CHANGAN UNIV

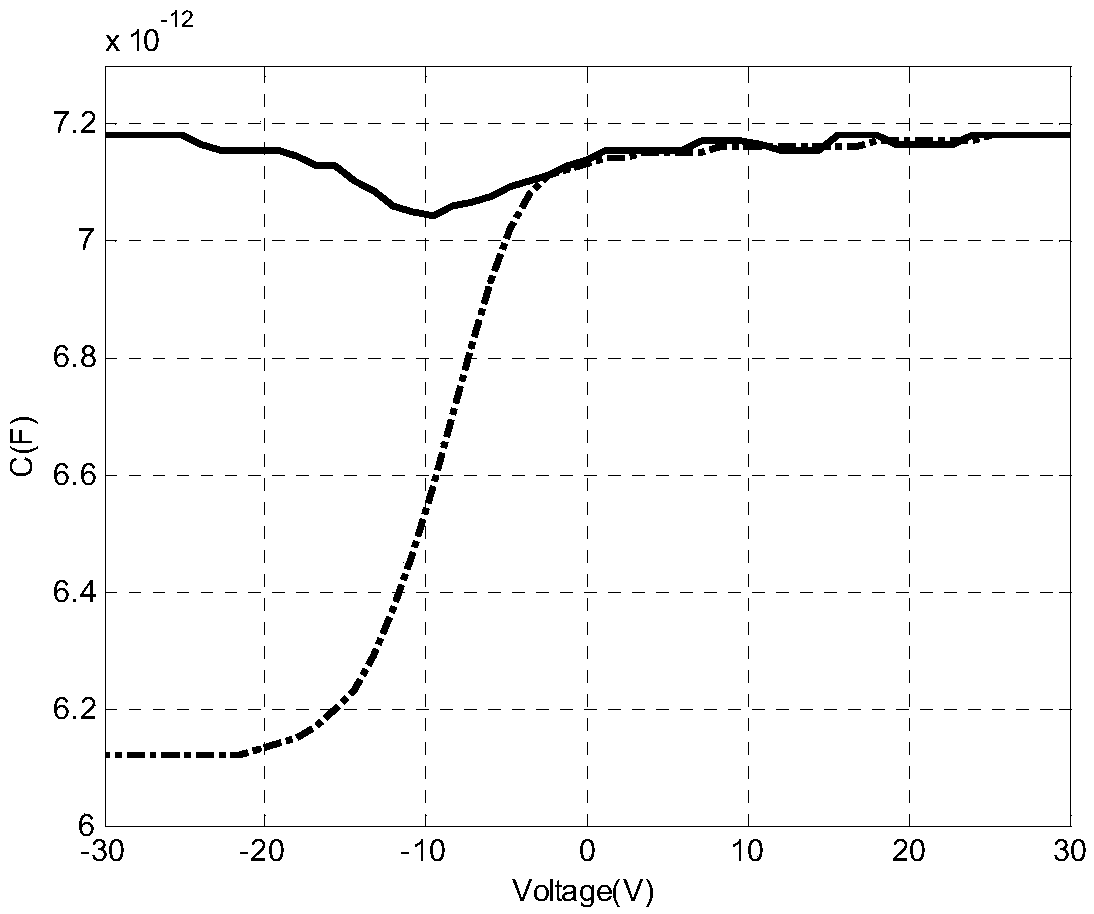

Graded barrier low-dark-current mesa type photodiode and manufacturing method thereof

ActiveCN110808298AReduce surface leakage currentReduce bulk dark currentSemiconductor devicesPlanar electrodeEngineering

The invention belongs to the technical field of detector chip manufacturing, and relates to a graded barrier low-dark-current mesa type photodiode. The mesa type photodiode comprises an N-type mesa, an absorption mesa and a P-type mesa which are connected in a stacked manner from top to bottom; the surface of each mesa is covered with a passivation layer; a graded barrier layer is arranged in an absorption mesa of the mesa type photodiode, and the graded barrier layer is of a nine-layer structure from top to bottom; an N electrode is arranged on the N-type mesa; a P electrode is arranged on the P-type mesa; and the P electrode and the N electrode form a coplanar electrode. By adopting the graded barrier structure, the surface leakage current and the body dark current of the mesa type photodiode are reduced, so that the reliability of the mesa type photodiode is improved.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

A mesa-type photodiode with graded barrier and low dark current and its manufacturing method

ActiveCN110808298BReduce surface leakage currentImprove reliabilitySemiconductor devicesPlanar electrodeEngineering

The invention belongs to the technical field of detector chip manufacture, and relates to a mesa-type photodiode with low dark current in a graded potential barrier; an N-type mesa, an absorption mesa and a P-type mesa connected from top to bottom of the mesa-type photodiode; each mesa The surface of the mesa photodiode is covered with a passivation layer; a graded barrier layer is arranged in the absorption mesa of the mesa photodiode, and the graded barrier layer has a nine-layer structure from top to bottom; an N electrode is arranged on the N-type mesa, and the The P-type mesa is provided with a P electrode, and the P electrode and the N electrode form a coplanar electrode; the present invention reduces the surface leakage current and the bulk dark current of the mesa photodiode by adopting a hierarchical barrier structure, thereby improving the mesa photodiode. reliability.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

Surface passivation method of InAlSb infrared detector

ActiveCN109585601AReduce surface recombination rateReduce surface leakage currentAfter-treatment detailsFinal product manufactureAnodizingOrganic solvent

The invention relates to a surface passivation method of an InAlSb infrared detector. The method comprises the steps of 1, immersing an InAlSb detector chip in an organic solvent; 2, immersing the InAlSb detector chip in an acidic solution; 3, putting the InAlSb detector chip into an anodizing solution, setting a anodizing current, turning on a metal electrode, and turning off an anodizing power source to form an anodized film when the resistance value of the chip surface reaches a set value; 4, cleaning the InAlSb detector chip; and 5, then placing the InAlSb detector chip in a PECVD device to prepare a dielectric film. The method can reduce the leakage current on the surface of the infrared detector and increases the device impedance.

Owner:CHINA AIR TO AIR MISSILE INST

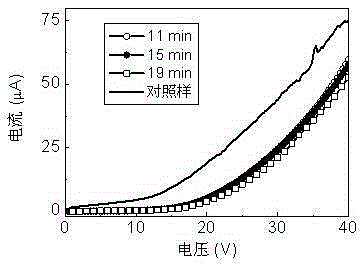

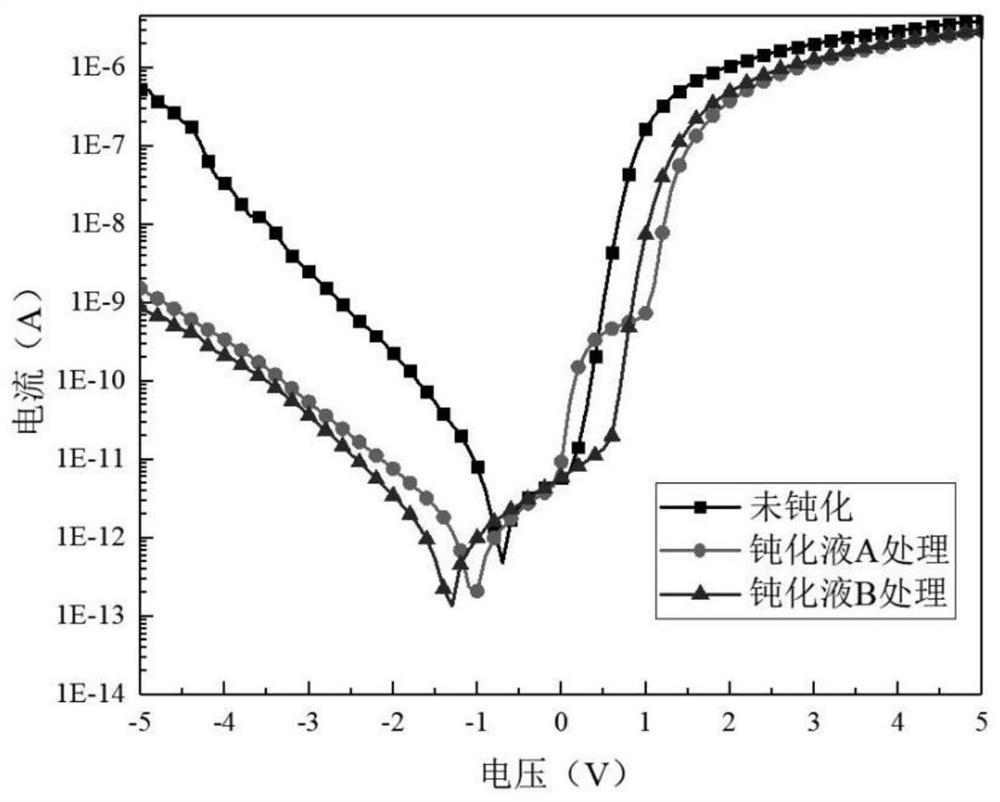

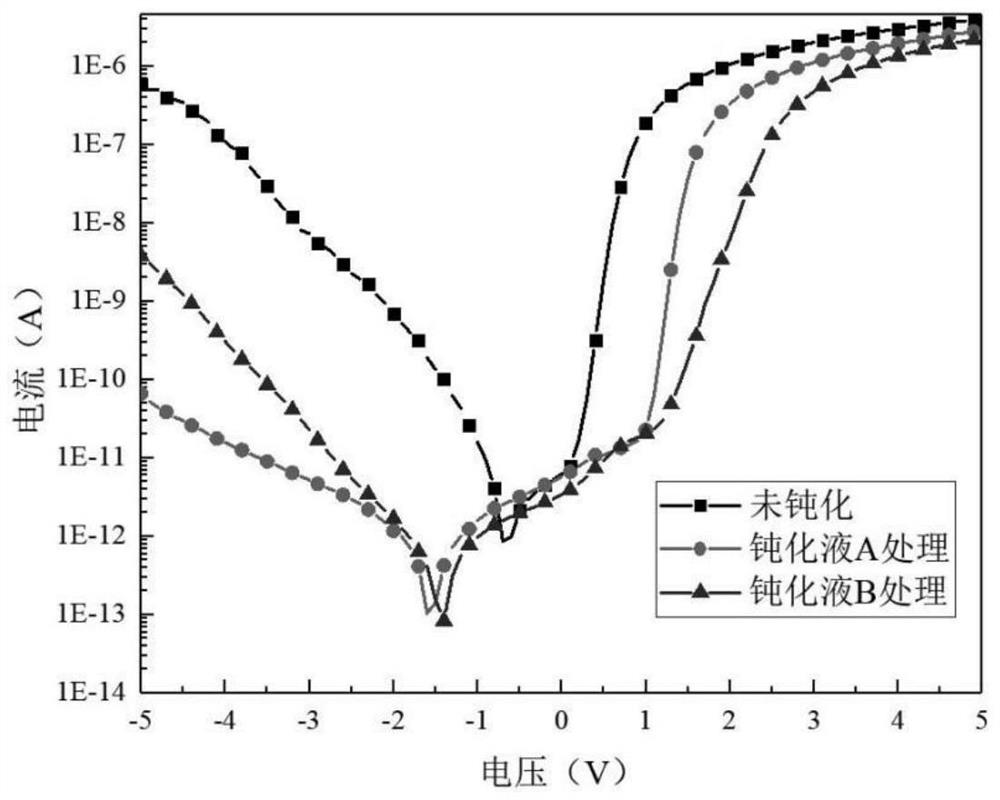

A kind of passivation method of cadmium zinc telluride crystal surface

InactiveCN103887370BReduce surface leakage currentSimple passivation processFinal product manufactureSemiconductor devicesWaferingThiourea

The invention discloses a passivation method for the surface of cadmium zinc telluride crystal, that is, the passivation solution is firstly prepared and calculated according to the mass ratio, that is, the aqueous solution of thiourea: deionized water is 9:100, and then the prepared Put the cadmium zinc telluride chip of the electrode into the passivation solution for passivation for 11-19 minutes, immediately wash it with a large amount of deionized water for 3-5 times, then wash it once with absolute ethanol, and finally dry it with an ear washing ball, that is Complete passivation of the CdZnTe crystal surface. The passivation method for the surface of the cadmium zinc telluride crystal has the advantages of simple passivation process and low processing cost, and effectively reduces the surface leakage current of the cadmium zinc telluride crystal.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER

Refrigeration infrared detector and preparation method thereof

PendingCN114256378AStrong adhesionReduce surface leakage currentFinal product manufactureSemiconductor devicesPhysicsIr detector

The invention provides a refrigeration infrared detector and a preparation method thereof, and the preparation method comprises the following steps: providing a substrate, and forming a superlattice composite layer on the substrate; executing a first cleaning and surface treatment process; forming a first passivation layer on the superlattice composite layer; forming a hard mask layer with an opening on the first passivation layer, sequentially etching the first passivation layer and the superlattice composite layer by taking the hard mask layer as a mask to form a groove and a table surface, and removing the hard mask layer; executing a second cleaning and surface treatment process; forming a second passivation layer on the first passivation layer, wherein the second passivation layer also covers the groove and the mesa; and etching the first passivation layer and the second passivation layer to form an open pore, and forming a metal electrode in the open pore. According to the invention, cleaning and surface treatment processes are carried out before the passivation layer is formed each time, so that the surface leakage current of the device can be reduced, and the performance of the device is improved.

Owner:SHANGHAI LEXVU OPTO MICROELECTRONICS TECH

Passivation process method for gallium nitride and gallium nitride ternary alloy

InactiveCN113054057AReduce surface leakage currentImprove performanceFinal product manufactureSemiconductor devicesGallium nitrideRuthenium chloride

The invention discloses a passivation process method for gallium nitride and gallium nitride ternary alloy. The process method comprises the following steps: carrying out primary passivation on clean gallium nitride and gallium nitride ternary alloy by taking nitric acid, ruthenium trichloride or sodium sulfide as a passivation solution; after first passivation cleaning, epitaxially growing a silicon dioxide or silicon nitride film for second passivation; and after the device is formed, carrying out third passivation by taking nitric acid, ruthenium trichloride or sodium sulfide as a passivation solution. By using the passivation process provided by the invention, a surface leakage current and a dark current of gallium nitride and gallium nitride ternary alloy device are effectively reduced, and the performance of the device is improved.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

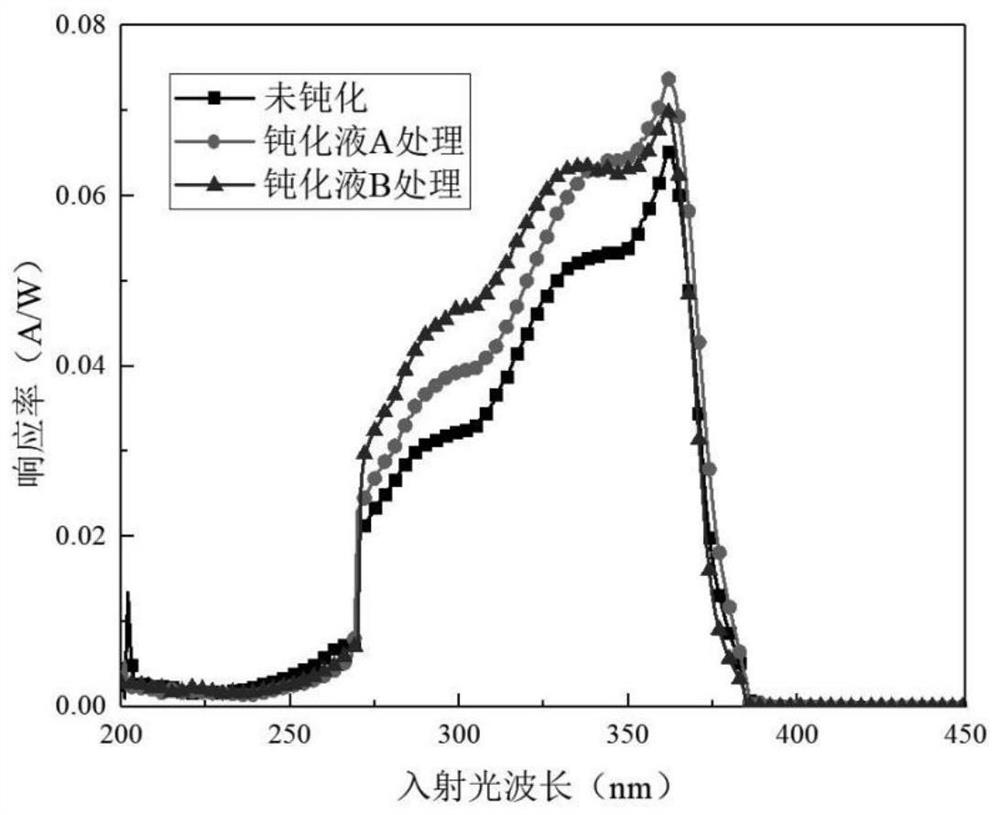

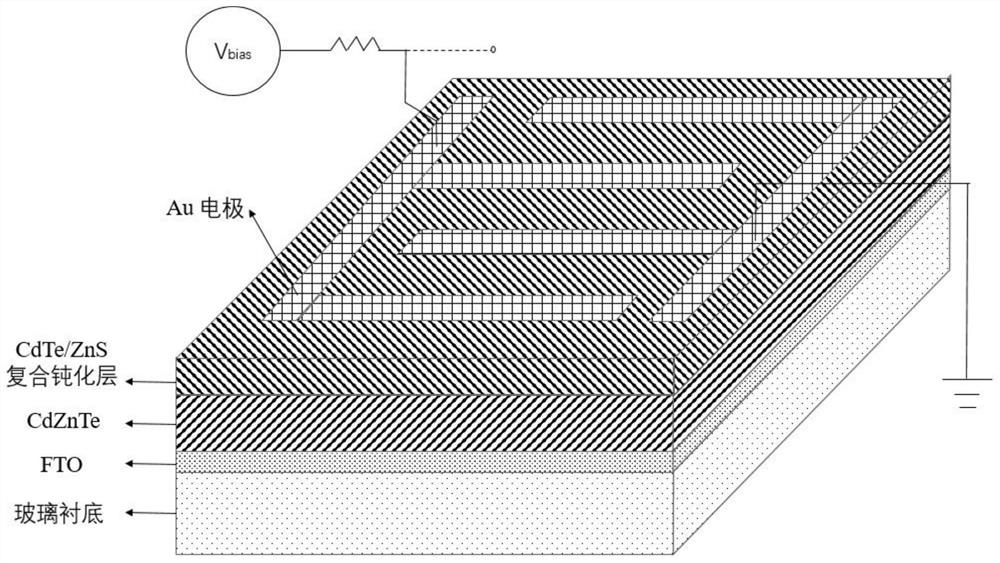

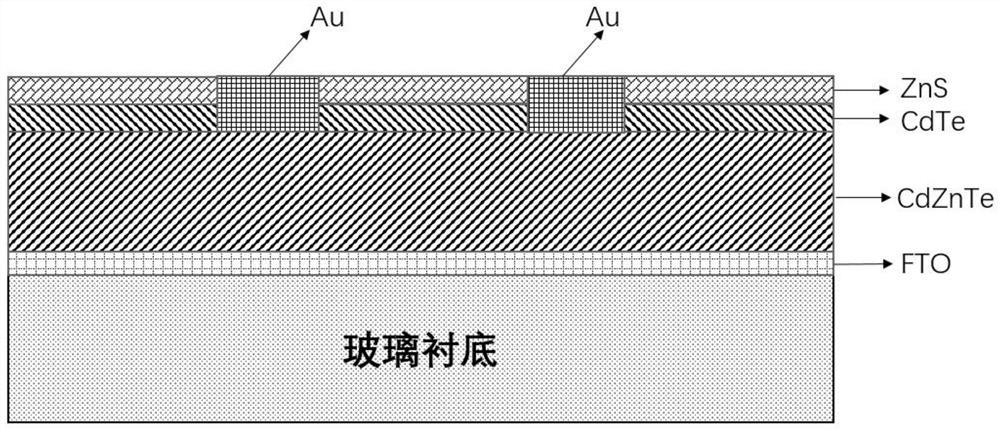

CZT film composite material with composite passivation layer, nuclear radiation detection device and preparation method thereof

InactiveCN112103350AReduce surface leakage currentHigh resistivityFinal product manufactureSemiconductor devicesThin membraneRadiation protection

The invention discloses a CZT film composite material with a composite passivation layer, a nuclear radiation detection device and a preparation method thereof, which belong to the technical field ofsemiconductor detection material manufacturing. According to the method, a cadmium zinc telluride film is deposited on a conductive glass substrate through a near-space sublimation method, and after polishing and corrosion, a cadmium zinc telluride and zinc sulfide composite passivation layer is sequentially deposited on the cadmium zinc telluride film through a magnetron sputtering method. And then annealing is carried out in an N2 atmosphere. And after photoetching and dry etching, a gold electrode is continuously deposited on the film by using an electron beam evaporation method. Due to theexistence of the passivation layer, the surface of the polished and corroded cadmium zinc telluride film is well protected, and the leakage current of the surface of the cadmium zinc telluride film is reduced, so that the performance of a cadmium zinc telluride detector is improved; the film material prepared by the invention has an important significance and application prospect in the aspects of safety monitoring and radiation protection in the fields of public safety, military affairs, nuclear industry, nuclear medicine, scientific research, aerospace and the like.

Owner:SHANGHAI UNIV

Ion implantation method, preparation method of mercury cadmium telluride chip and mercury cadmium telluride chip

ActiveCN112086363AAvoid damageLow densityFinal product manufactureSemiconductor/solid-state device manufacturingMercury cadmium telluridePhysical chemistry

The invention provides an ion implantation method, a preparation method of a tellurium-cadmium-mercury chip and the tellurium-cadmium-mercury chip. The preparation method of the tellurium-cadmium-mercury chip comprises the following steps: forming a dielectric film layer above a P-type tellurium-cadmium-mercury substrate; performing a heat treatment process on the P-type mercury cadmium telluridesubstrate and the dielectric film layer; forming a photoresist mask layer above the dielectric film layer, and performing patterning processing on the photoresist mask layer to form a latticed ion implantation window on the photoresist mask layer; injecting high-energy ions into the surface of the P-type mercury cadmium telluride substrate through the ion injection window so as to form an N-type doped region in the surface of the P-type mercury cadmium telluride substrate; removing the photoresist mask layer; and carrying out a heat treatment process on the P-type mercury cadmium telluride substrate. According to the method, the dielectric film layer which is not bombarded by high-energy ions in the injection area is effectively protected, and damage to a good interface formed between thedielectric film layer and mercury cadmium telluride through heat treatment is reduced.

Owner:北京智创芯源科技有限公司

A Group III Nitride Semiconductor Avalanche Photodiode Detector

InactiveCN106711253BSimple structure and processSimple preparation processSemiconductor devicesMarginal leakageAlloy

The invention discloses an III-nitride semiconductor avalanche photodetector which comprises a substrate and an epitaxial layer that grows above the substrate. According to a sequence from bottom to top, the epitaxial layer is successively provided with an unintentional adulteration nitride buffer layer, an unintentional adulteration nitride transition layer, a heavy adulteration n-type nitride ohmic electrode contact layer, a heterogeneous light adulteration p-type nitride active layer, a p-type adulteration nitride layer and a heavy adulteration p-type nitride ohmic electrode contact layer. Simultaneously, the invention discloses a device manufacturing method, the method comprises the steps of taking advantage of multiple times of photoetching and dry etching to make steps on the periphery of a device, respectively carrying out vapor deposition of p-type and n-type metal electrodes on the p-type ohmic contact layer and the n-type ohmic contact layer, and forming ohmic contact with a semiconductor through an alloy. According to the device structure, the electric field intensity of an avalanche photodiode active area can be enhanced, and the properties of low dark current, high gain and high detection responsivity of the nitride avalanche photodetector can be realized by effectively increasing the field intensity of the active area and reducing the marginal leakage current of the device.

Owner:江苏华功第三代半导体产业技术研究院有限公司

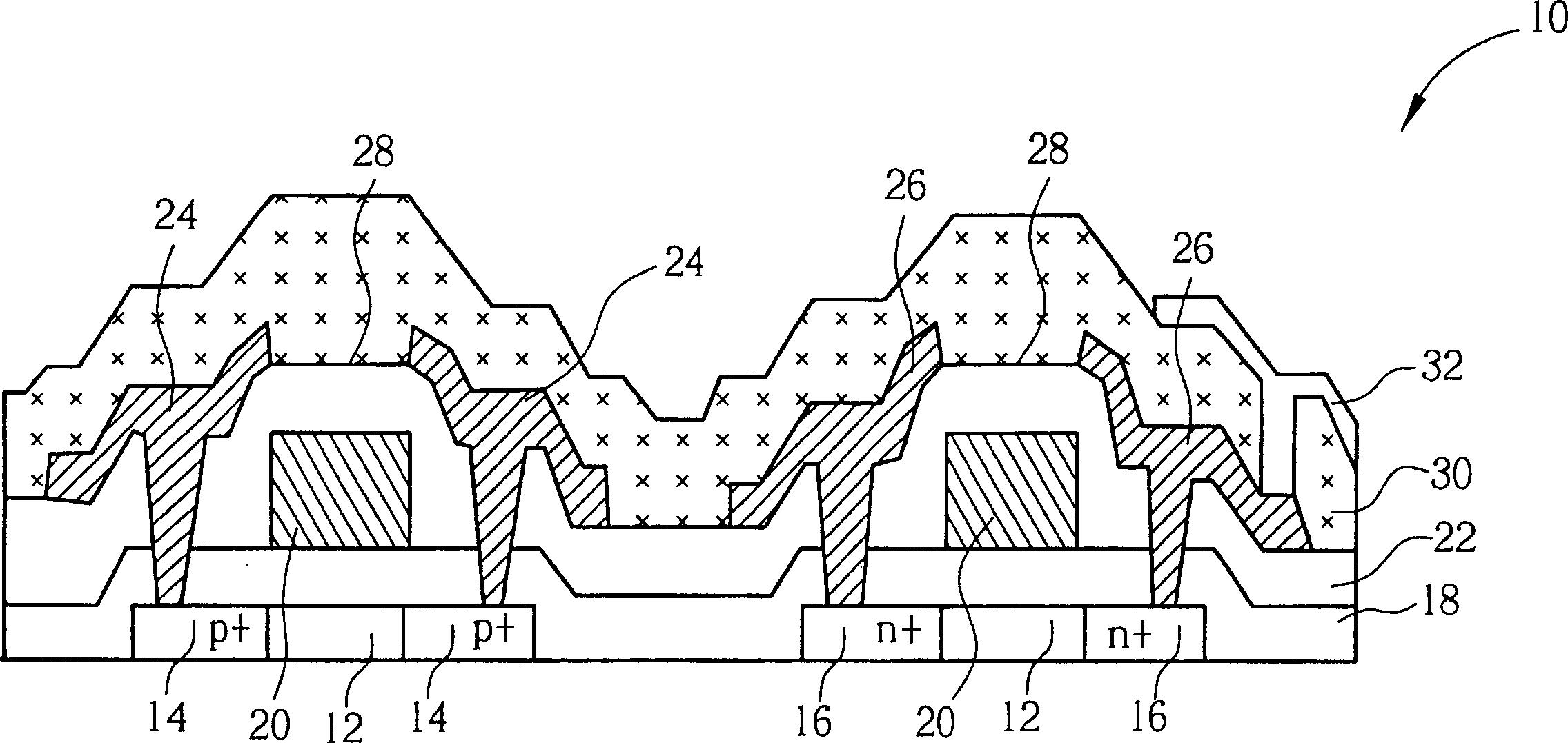

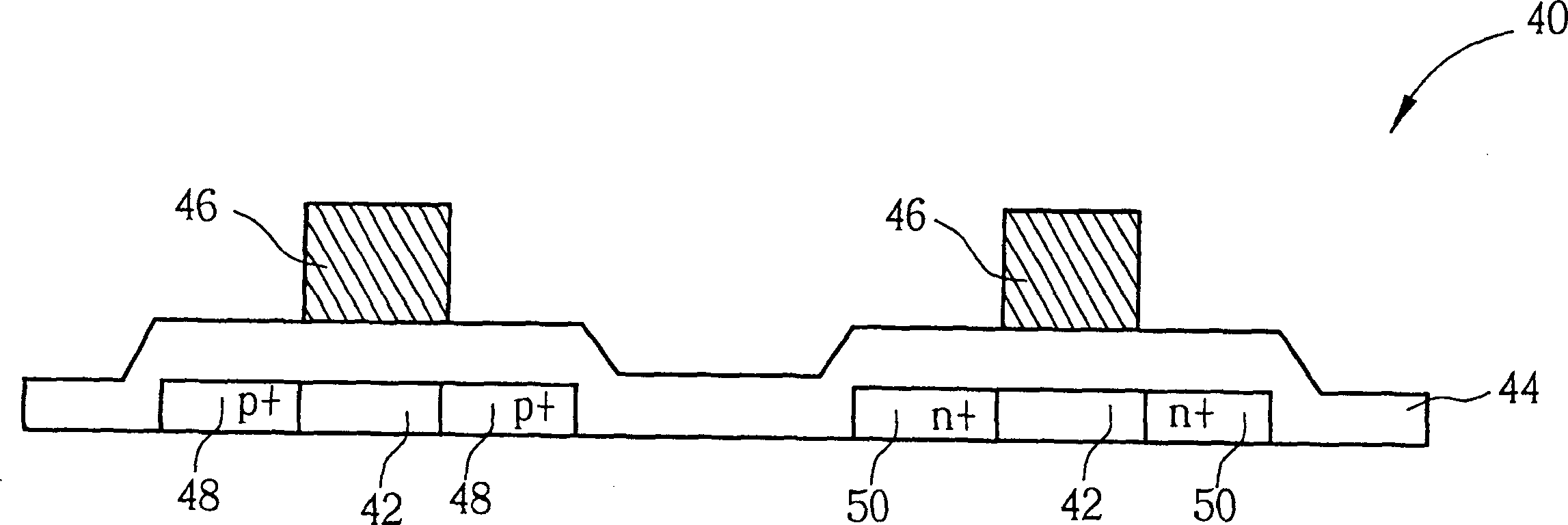

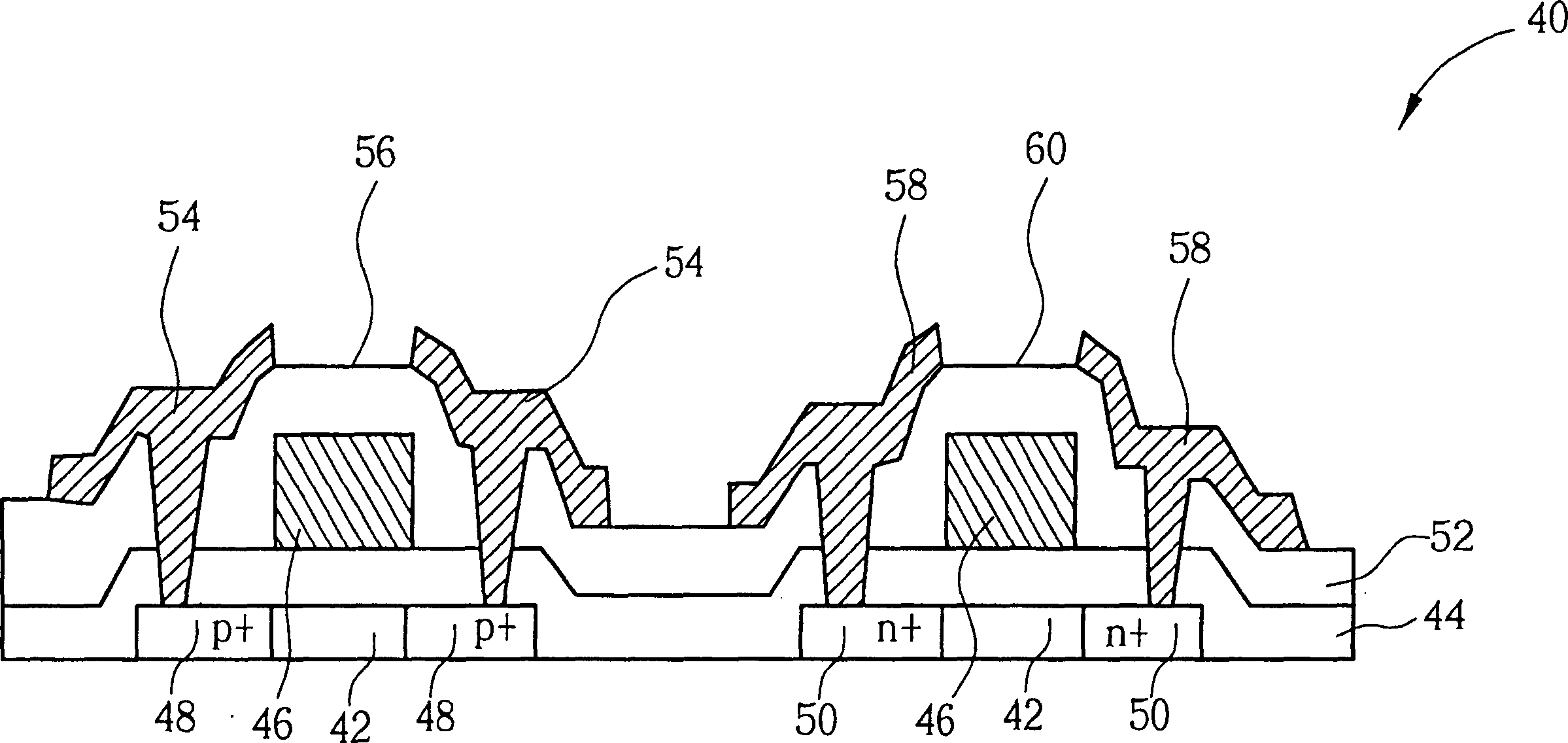

Method for reducing leakage current on surface of base plate in thin film transistor

InactiveCN1275303CIncreasing the thicknessImprove electrical performanceStatic indicating devicesSemiconductor/solid-state device manufacturingInsulation layerMaterials science

First, multiple Thin Film Transistors (TFT) are formed on a base plate. Next, an insulation layer and a metal layer are formed on TFT in sequence. The metal layer includes a source pole and a drain pole connected to each TFT, and there is a channel region between the source pole and the drain pole. Then, an organic material layer is covered on the metal layer and the insulation layer, and a transparent conducting layer is formed on the organic material layer. In the procedure of forming the organic material layer, since the insulation layer is densified synchronistically, route of current leakage of the base plate is blocked out so as to reduce current leakage on surface.

Owner:AU OPTRONICS CORP

A Visible-Ultraviolet Dual Color Detector

ActiveCN112490305BReduce dark currentImprove monolithic integrationSemiconductor devicesMetallic electrodePhotodetector

The invention belongs to the technical field of semiconductor photodetectors, and specifically relates to a visible-ultraviolet dual-color detector. The visible-ultraviolet dual-color detector adopts a vertically integrated structure, including an nGaN substrate, an n-type GaN contact layer, a lower metal electrode, and an AlGaN Matching layer, AlGaN ultraviolet absorbing layer, two-dimensional boron nitride thin film barrier layer, topological insulator visible light absorbing layer, n-type topological insulator thin film contact layer, upper metal electrode and passivation layer. The detectors of the two bands in the detector have a bottom-up integrated structure, which can realize visible and ultraviolet dual-color detection by controlling the bias voltage, reduce the false alarm rate, reduce the size of the device, and reduce the cost of the preparation process and detection system. Complexity.

Owner:TIANJIN JINHANG INST OF TECH PHYSICS

thin film transistor

ActiveCN103904126BCurrent switch ratio improvementReduce concentrationTransistorIndium gallium zinc oxideZinc

The invention provides a thin-film transistor comprising a substrate, a grid electrode which is arranged on the substrate, a grid insulating layer which is arranged on the substrate and covers the grid electrode, an indium gallium zinc oxide channel layer which covers the surface of the grid insulating layer, and a gallium oxide zinc layer which is arranged on the surface of the channel layer. A source electrode and a drain electrode are formed on the two opposite sides of the gallium oxide zinc layer. The thin-film transistor with the structure has advantages of being low in surface leakage current and great in current switch ratio.

Owner:深圳市金誉半导体股份有限公司

SiC Schottky power diode and preparation method thereof

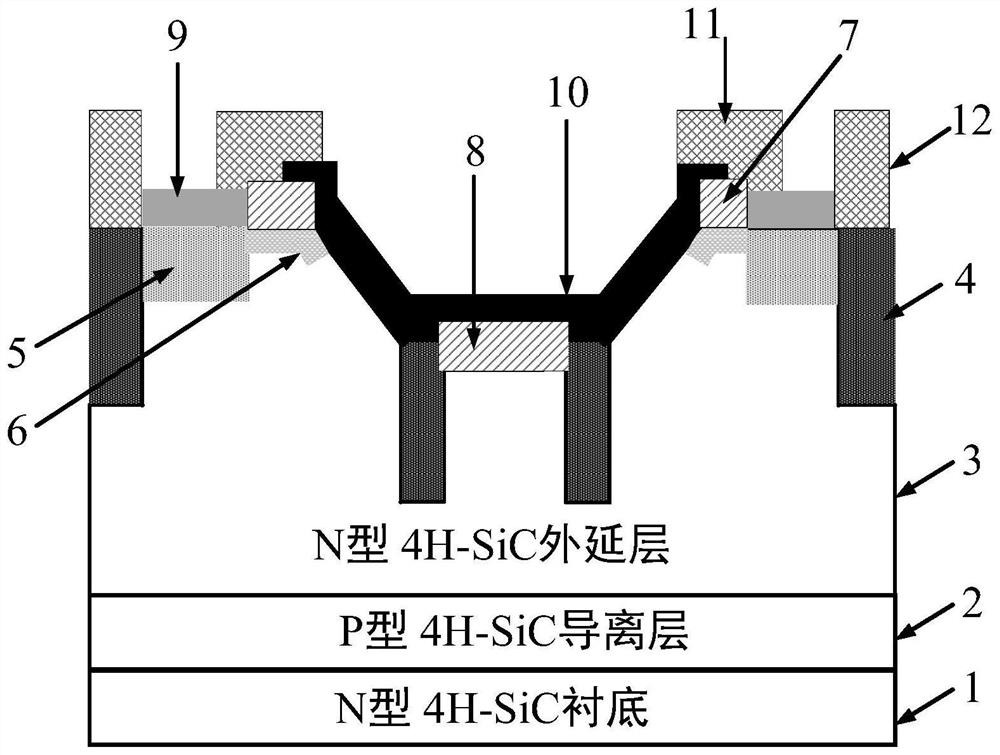

PendingCN113823698AIncrease current conduction areaImprove forward conduction abilitySemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactPower diode

The invention discloses a SiC Schottky power diode. The SiC Schottky power diode comprises an N-type 4H-SiC substrate, a P-type 4H-SiC isolation layer and an N-type 4H-SiC epitaxial layer, wherein the thickness of the N-type 4H-SiC epitaxial layer is 4-6 [mu]m; an inverted trapezoidal anode groove and an isolation groove are engraved in the middle of the epitaxial layer, and the tops of two ends of the epitaxial layer avoid inwards to form an isolation region; the isolation region and the isolation groove are filled with an insulating medium to form a current dredging structure; and the epitaxial layer is provided with an N+ injection region and a P+ injection protection region. The SiC Schottky power diode comprises: a cathode ohmic contact metal layer covering the N+ injection region; a first passivation layer arranged on the P+ injection protection region; a second passivation layer arranged at the bottom of the anode groove; an anode Schottky contact metal layer covering part of the surface of the first passivation layer, the surface of the anode groove and the surface of the second passivation layer; and a third passivation layer covering the remaining surface of the first passivation layer and extending towards the metal layers on the two sides. According to the invention, the performance and yield of the Schottky power diode under high working voltage are improved.

Owner:瑶芯微电子科技(上海)有限公司

Diffusion-free avalanche photodiode and preparation method thereof

ActiveCN103094398BSimple designEasy to manufactureSemiconductor devicesControl layerSelective leaching

Owner:WUHAN TELECOMM DEVICES

A kind of inalsb infrared detector surface passivation method

ActiveCN109585601BReduce surface recombination rateReduce surface leakage currentAfter-treatment detailsFinal product manufactureAnodizingMetallic electrode

The invention relates to a method for passivating the surface of an InAlSb infrared detector. The steps are as follows: step 1: soaking the InAlSb detector chip in an organic solvent; step 2: soaking the InAlSb detector chip in an acidic solution; step 3 : Put the InAlSb detector chip into the anodizing solution, set the anodizing current and connect the metal electrode, when the resistance value on the surface of the chip reaches the set value, cut off the anodizing power supply to form an anodizing film; step 4: cleaning InAlSb detector chip; step five: put it into PECVD equipment, and prepare a dielectric film. The method can effectively reduce the leakage current on the surface of the infrared detector and improve the impedance of the device.

Owner:CHINA AIR TO AIR MISSILE INST