Chip and forming method thereof

A chip and gate technology, applied in the field of chip and its formation, can solve problems such as difficult to achieve breakdown current, large resistance, affecting chip repair efficiency, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

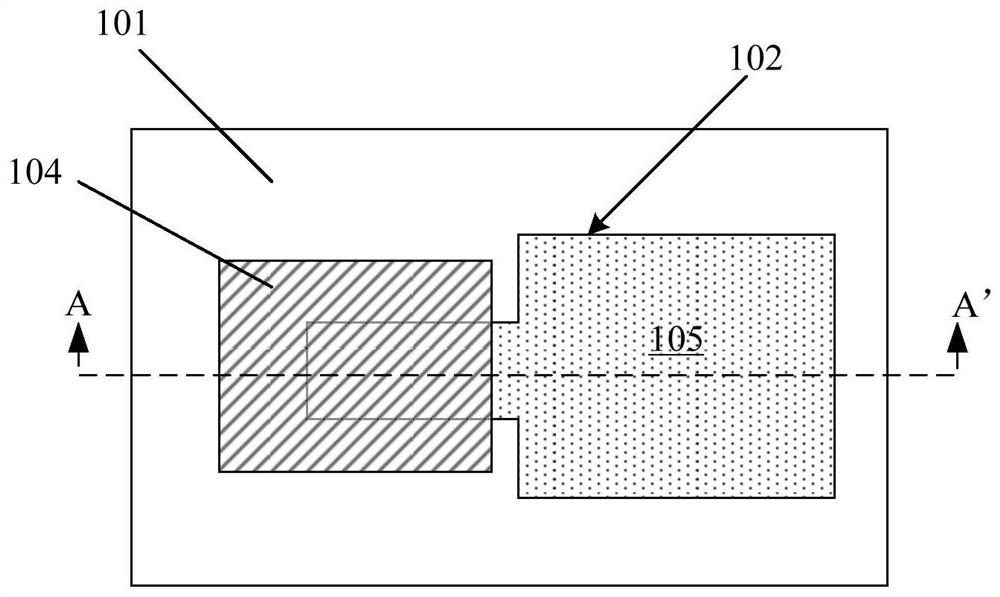

[0020] Specific implementations of the antifuse device and its forming method, the memory and its forming method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

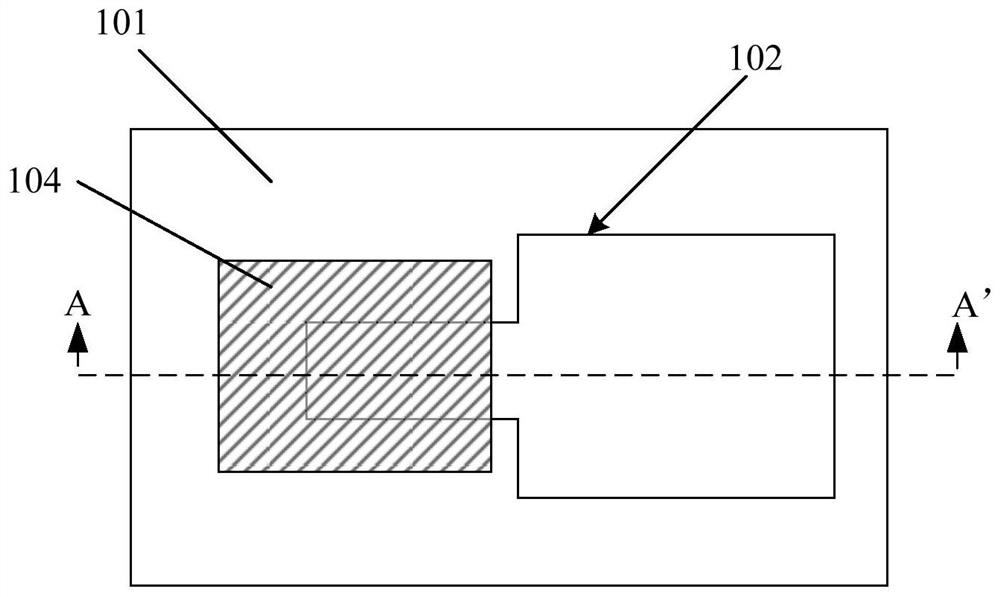

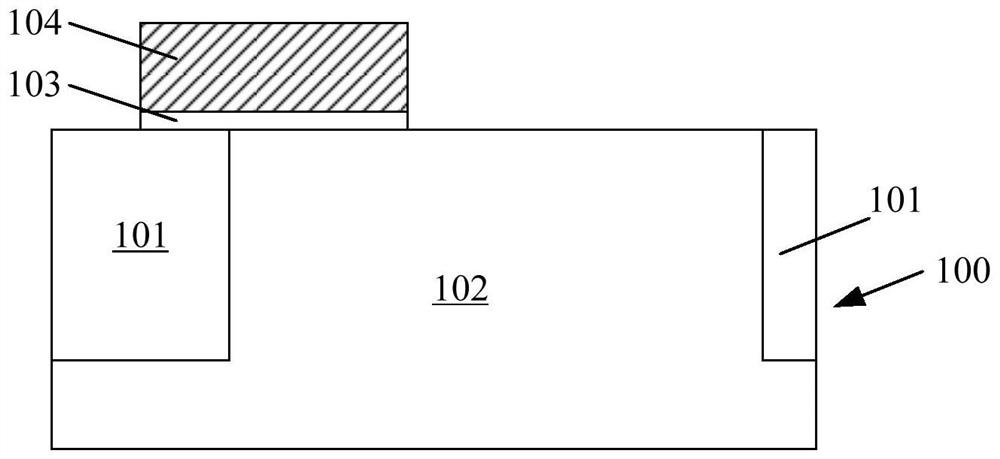

[0021] Please refer to Figure 1 to Figure 4 , is a structural schematic diagram of the formation process of the anti-fuse device according to a specific embodiment of the present invention.

[0022] Please refer to figure 1 and figure 2 ,in figure 2 for along figure 1 Schematic cross-sectional view of the secant line AA'.

[0023] A substrate 100 is provided, and a gate structure is formed on the surface of the substrate 100 . The gate structure includes a gate dielectric layer 103 on the surface of the substrate 100 and a gate 104 on the surface of the gate dielectric layer 103 .

[0024] The substrate 100 may be a semiconductor substrate, such as a single crystal silicon substrate, a single crystal germanium substrate, and the like. The su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More