Semiconductor device with separated planar field plate structure and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as limiting the final characteristics of high-voltage devices, achieve the effects of shortening the current path in the drift region, achieving compatibility, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

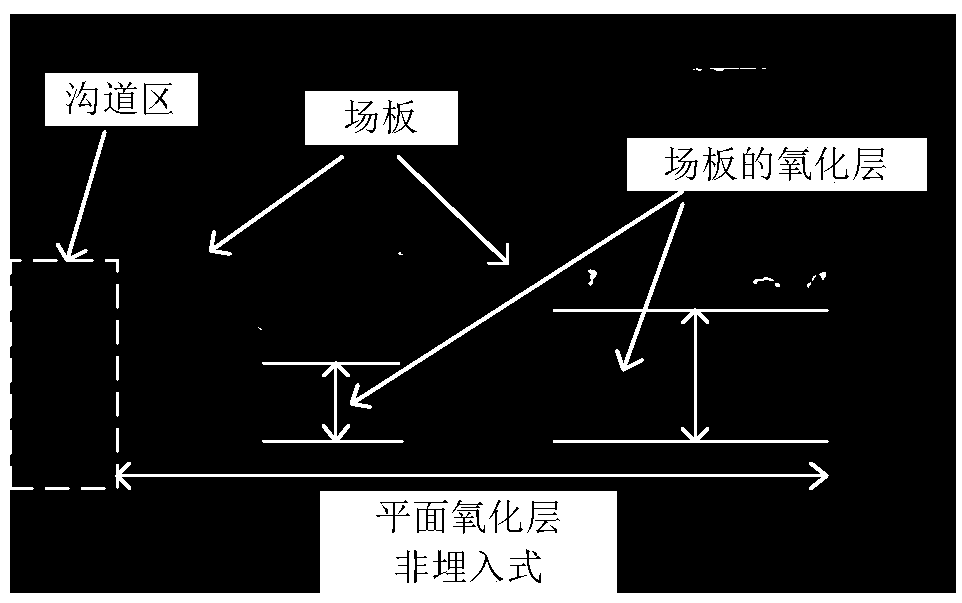

[0059] In order to solve the problems in the prior art, the invention provides a method for manufacturing a semiconductor device, such as image 3 As shown, it includes the following main steps:

[0060] Step S1, providing a semiconductor substrate, forming a source, a drain, and a gate on the semiconductor substrate, and forming a drift region in the semiconductor substrate between the gate and the drain,

[0061] Step S2, forming a first dielectric layer to cover the surface of the semiconductor substrate and the source, drain and gate,

[0062] Step S3 , forming a first field plate layer on the first dielectric layer, and the first field plate layer is at least partially located above the drift region and close to the side of the gate.

[0063] According to the manufacturing method of the present invention, during the process of depositing the dielectric layer, the steps of depositing the dielectric layer and forming the field plate layer are alternately performed to form ...

Embodiment 2

[0130] The present invention also provides a semiconductor device, which can be the semiconductor device prepared by using the method in the first embodiment above.

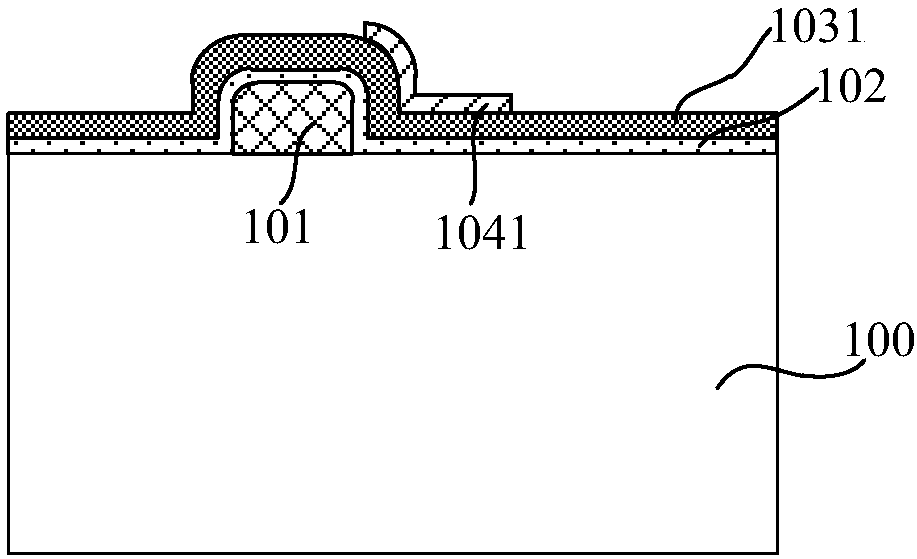

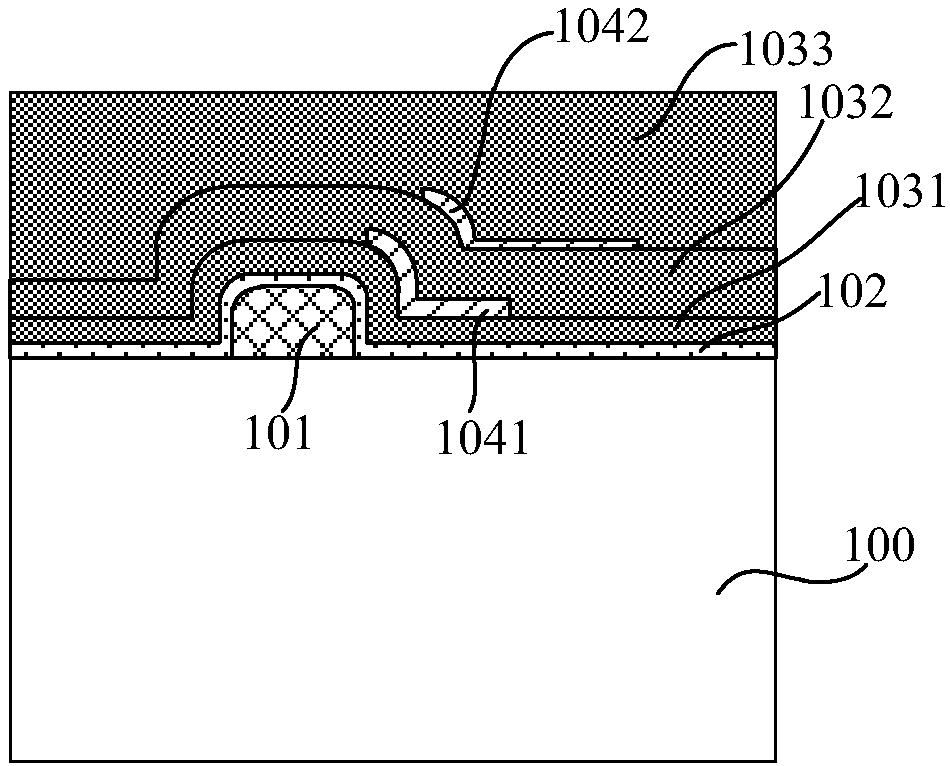

[0131] In one embodiment, as Figure 1A As shown, the semiconductor device of the present invention includes:

[0132] A semiconductor substrate 100, on which a source, a drain, and a gate 101 are formed, and a drift region is formed in the semiconductor substrate between the gate 101 and the drain;

[0133] The first dielectric layer 1031 covers the surface of the semiconductor substrate 100 and the source, drain and gate 101;

[0134] The first field plate layer 1041 is formed on the first dielectric layer 1031, the first field plate layer is at least partially located above the drift region and close to the side of the gate 101, for example, the The first field plate layer 1041 is partly located above the gate 101, and the first field plate layer 1041 includes a part located on the gate and a part located on ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More