Trench LDMOS transistor with convex extended buried oxide region

A technology of transistors and trenches, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of reducing the size of device cells and reducing the on-resistance of devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with drawings and embodiments.

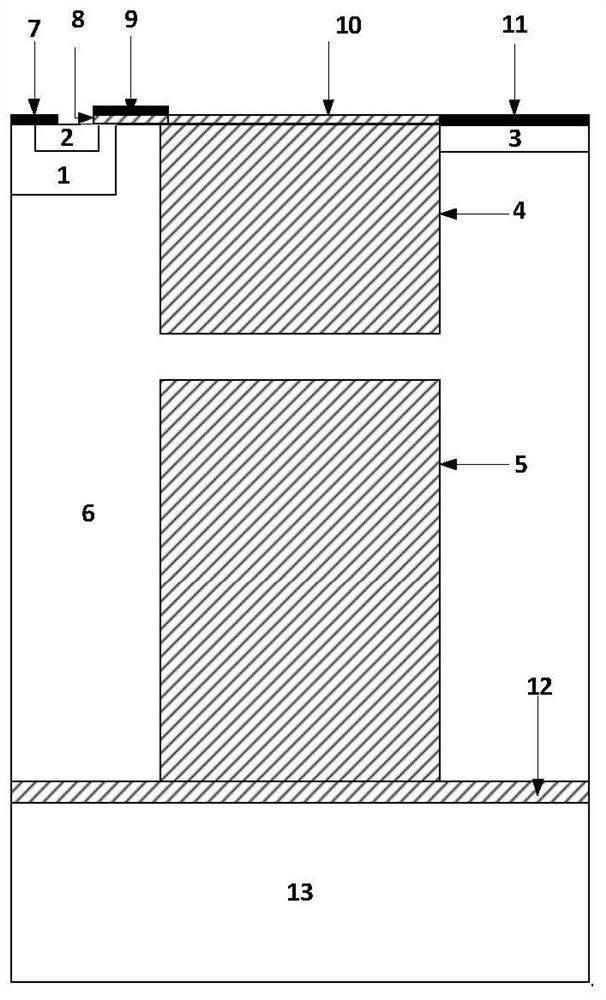

[0020] Such as figure 1 As shown, the trench LDMOS transistor with a convex extended buried oxide region includes a substrate layer 13, a buried oxide layer 12, a silicon film layer and a device top layer. The substrate layer 13 is located at the bottom, the material is silicon, and P-type doping is adopted; the buried oxide layer 12 is located above the substrate layer, and the material is silicon dioxide; the silicon film layer is located above the buried oxide layer 12, and the silicon film layer includes a silicon body 1, Source region 2, drain region 3, oxidation trench 4, convex extended buried oxide region 5 and drift region 6; silicon body 1 and drain region 3 are located on different sides of the top of the silicon film layer; silicon body 1 is concave, and the material is silicon , using P-type doping; the source region 2 is located in the groove of the silic...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More