High-speed circuit board serial port debugging method based on FPGA and DSP

A debugging method and serial debugging technology, which is applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as failure of simulation, errors, and the inability of the simulator to complete hardware simulation, and the method is simple and convenient. less error-prone effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

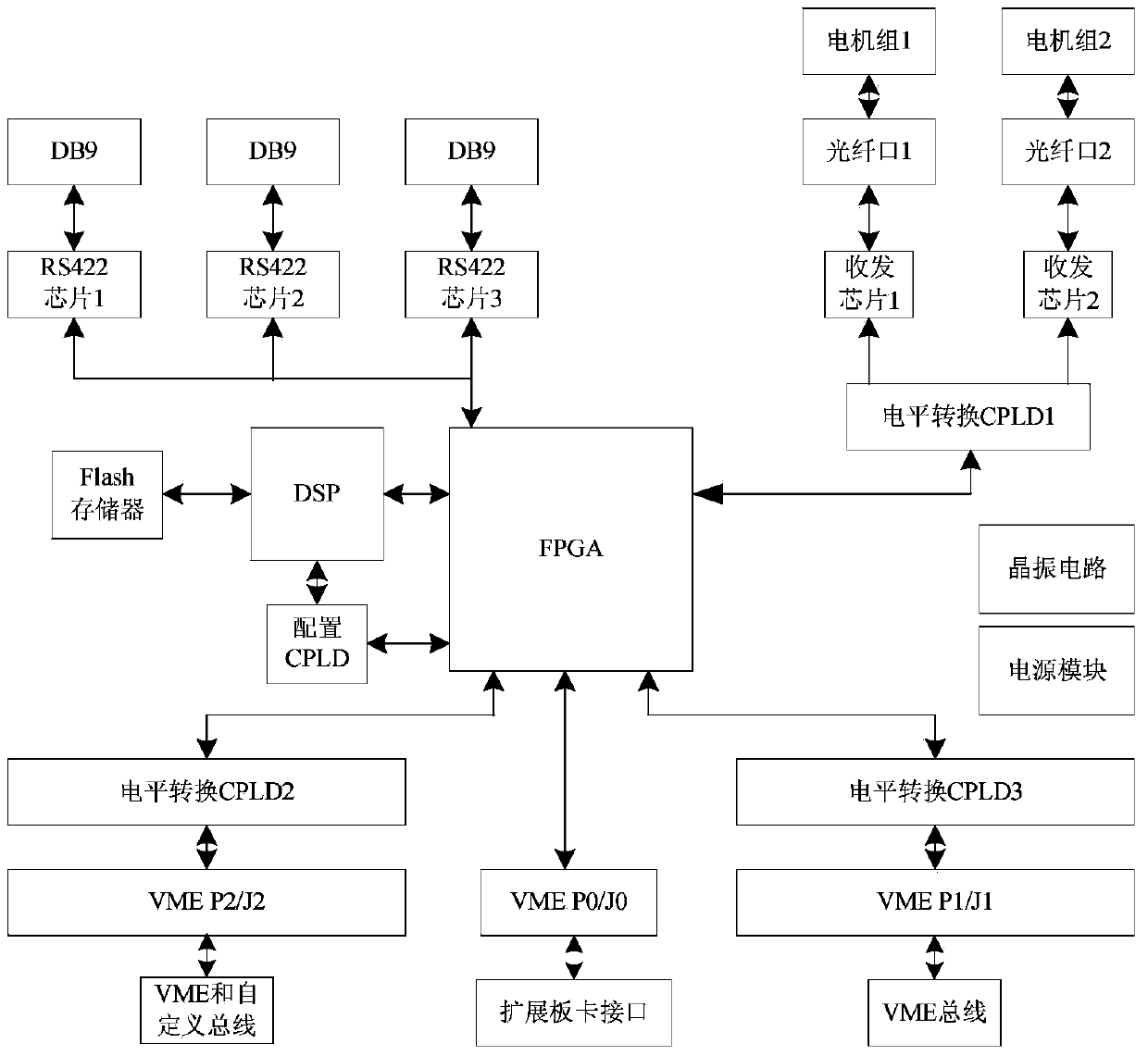

[0028] Specific implementation mode one: combine figure 1 Describe this embodiment, the debugging method of the high-speed circuit board serial port based on FPGA and DSP described in this embodiment,

[0029] Described method is realized based on FPGA, DSP and CPLD, and described method comprises:

[0030] Adopting FPGA to determine the timing of running DSP to carry out serial port debugging, the timing includes the steps of receiving timing and sending timing;

[0031] According to the determined timing, the steps of using DSP to realize serial port debugging;

[0032] Steps to use CPLD to provide normal level range for DSP and FPGA.

[0033] In this embodiment, the function of CPLD is to provide normal level range for DSP and FPGA, including:

[0034] Define various ports, such as connection lines with FPGA, etc.

[0035] Write a high-low level conversion program to provide external operating conditions for FPGA and VME bus.

specific Embodiment approach 2

[0036] Specific embodiment two: this embodiment is a further limitation to the debugging method of the high-speed circuit board serial port based on FPGA and DSP described in specific embodiment one, and described receiving sequence comprises:

[0037] Steps for setting clock input, high-level reset signal, RS422 data receiving terminal and data receiving flag bit interface definition;

[0038] It is used to set when the input signal encounters the corresponding edge, the serial signal edge detection module detects that the signal is set to a high level for one cycle;

[0039] It is used to set the steps of sampling data by the baud rate module when the clock drops;

[0040] Steps for setting the idle line detection module;

[0041] It is used to set the state machine and set the corresponding processing steps after the state machine.

specific Embodiment approach 3

[0042] Specific embodiment three: present embodiment is the further limitation to the debugging method of the high-speed circuit board serial port based on FPGA and DSP described in specific embodiment two,

[0043] The receiving sequence includes:

[0044] Steps for setting clock input, high-level reset signal, RS422 data receiving terminal and data receiving flag bit interface definition;

[0045] It is used to set when the input signal encounters the corresponding edge, the serial signal edge detection module detects that the signal is set to a high level for one cycle;

[0046] It is used to set the steps of sampling data by the baud rate module when the clock drops;

[0047] Steps for setting the idle line detection module;

[0048] It is used to set the state machine and set the corresponding processing steps after the state machine;

[0049] Steps for reading and writing signal settings and sending data.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com