SMT ((Surface Mount Technology) closed-loop integrated optimization system and optimization method thereof

An optimization method and optimization scheme technology, applied in manufacturing computing systems, instruments, data processing applications, etc., can solve problems such as unstable placement pressure, missing components, re-optimization, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

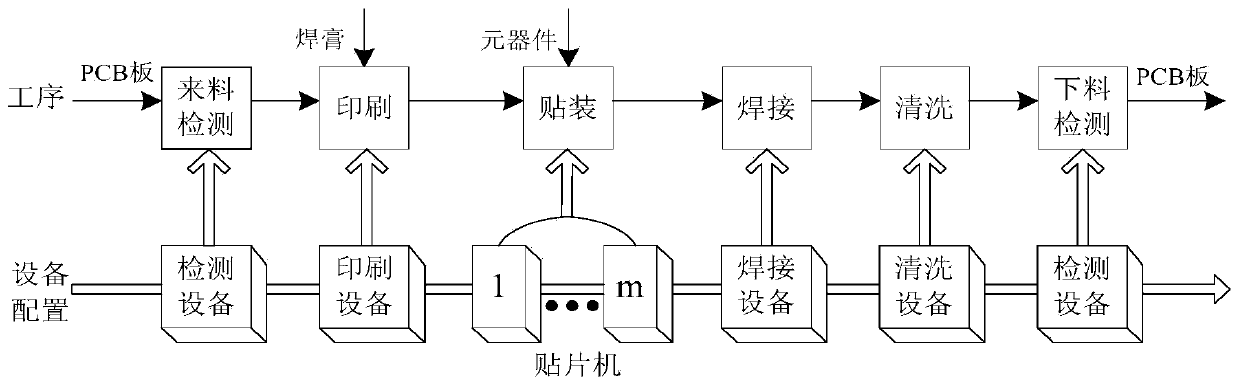

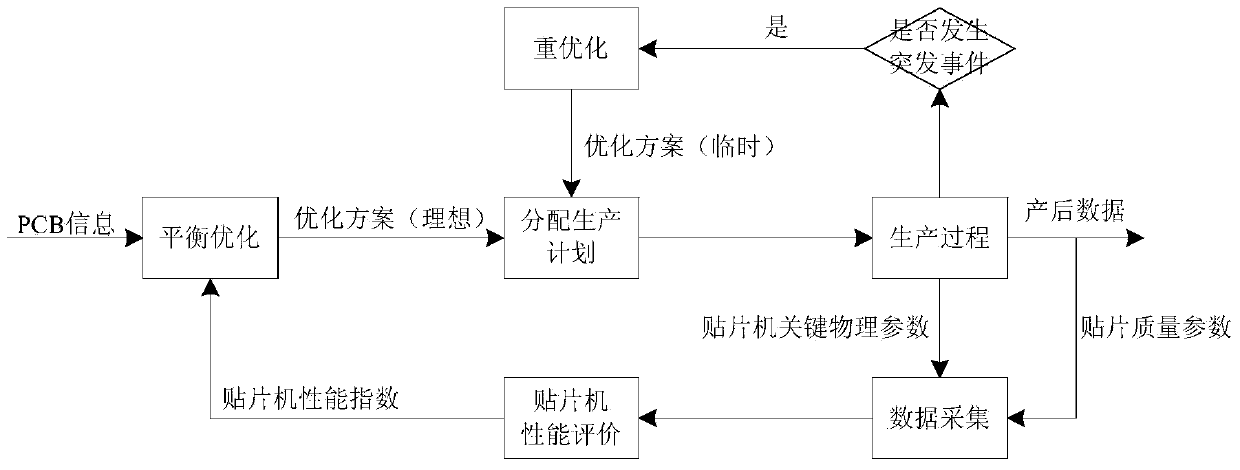

[0058] Such as figure 1 The typical SMT production process and equipment configuration are shown, mainly including 6 processes of PCB board incoming inspection, printing, mounting, welding, cleaning and unloading inspection, consisting of inspection equipment, printing equipment, placement machine, welding equipment , cleaning equipment, etc. to complete the PCB board printing, placement, welding, cleaning, and finished product testing process.

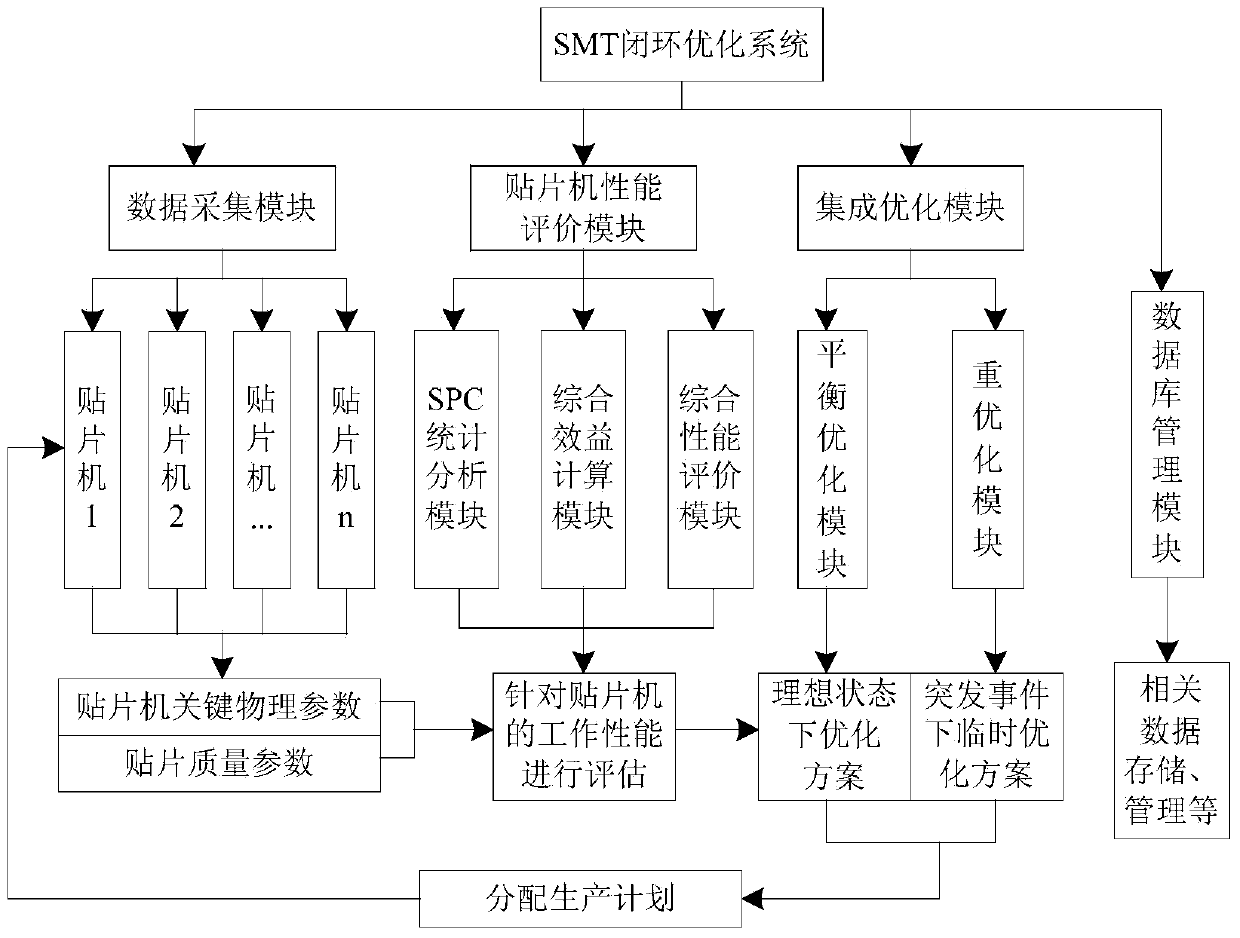

[0059] Such as figure 2 As shown, this embodiment discloses an SMT closed-loop integrated optimization system, including a data acquisition module, a placement machine performance evaluation module, an integrated optimization module and a database management module.

[0060] The data acquisition module of this embodiment directly collects the physical parameters during the placement operation of the placement machine and the placement quality parameters after production through the monitoring of the placement machine system; wherein...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More