Interference-mitigation word line driving circuit, flash memory and erasing method

A word line driving and memory technology, applied in the field of semiconductor memory, can solve the problems of information being susceptible to interference and voltage difference, and achieve the effect of reducing interference and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

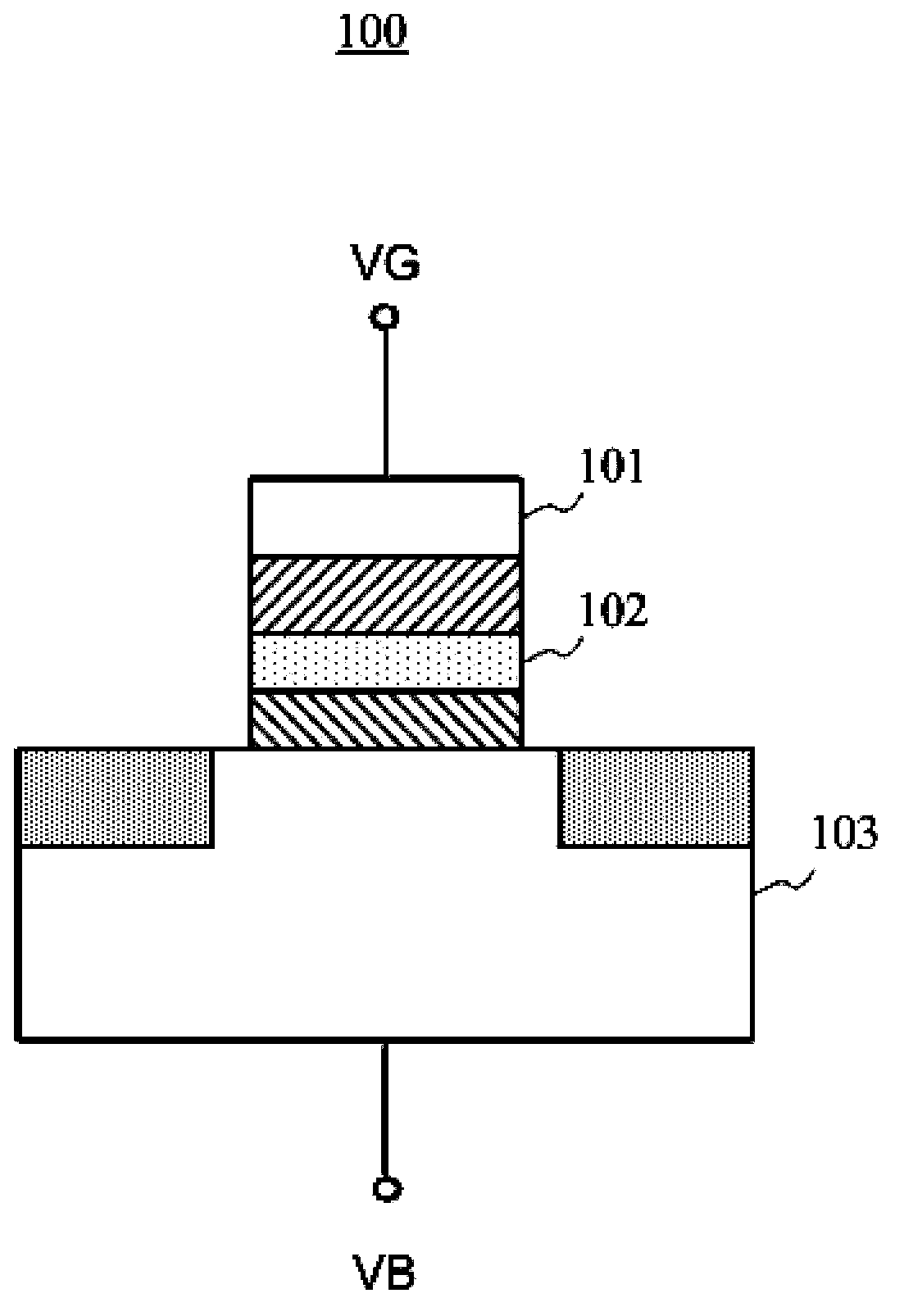

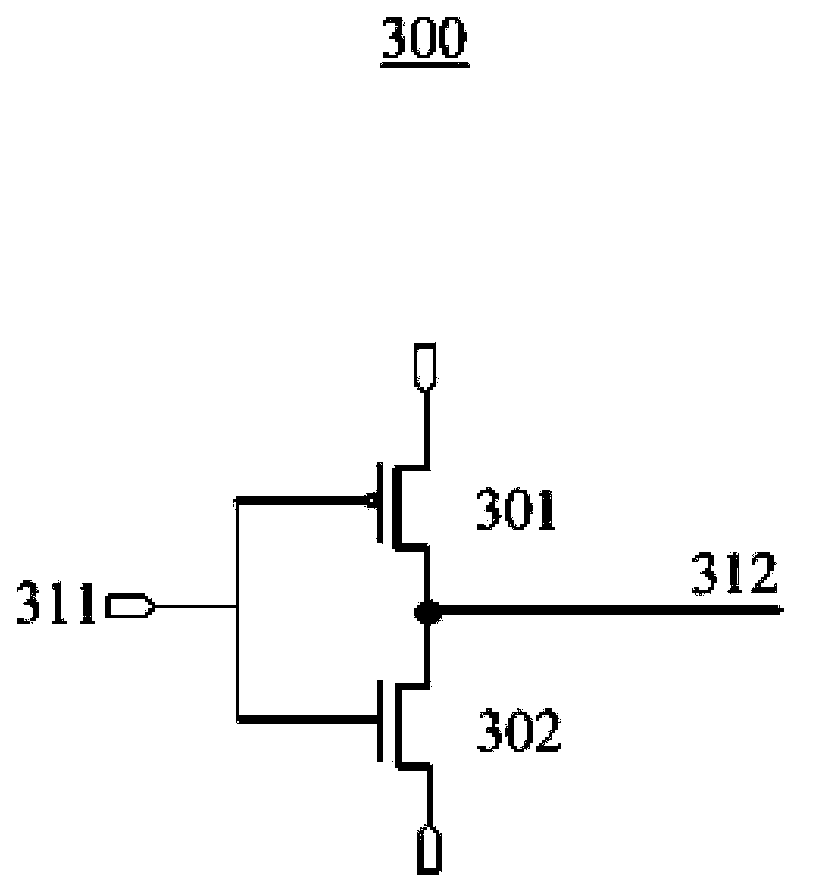

[0029] The technical solutions of the present invention are further described below with reference to the accompanying drawings and through specific embodiments.

[0030] It should be understood that although implementations of the invention described herein may be implemented using P-channel metal-oxide-semiconductor (PMOS) and N-channel metal-oxide-semiconductor transistor devices formed by complementary metal-oxide-semiconductor (CMOS) fabrication processes, It should be appreciated, however, that the present invention is not limited to such transistor arrangements and / or such fabrication processes, and those skilled in the art will appreciate that other suitable arrangements may similarly be employed, such as bipolar junction transistors (BJTs), etc. , and / or fabrication process (eg, bipolar BiCMOS, etc.). Additionally, although the preferred embodiments of the present invention are typically fabricated in silicon wafers, embodiments of the present invention may alternativ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com