Integrated circuit with backside structure reducing substrate warpage

A technology of integrated circuits and substrates, applied in the field of integrated circuits with backside structures, can solve problems such as difficulty in development

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

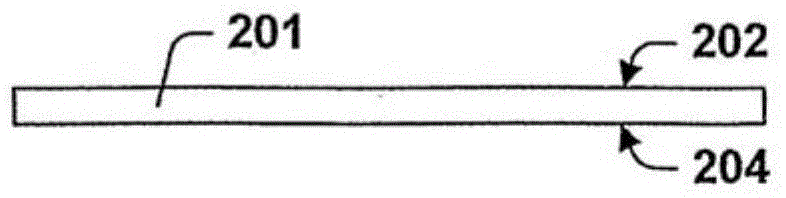

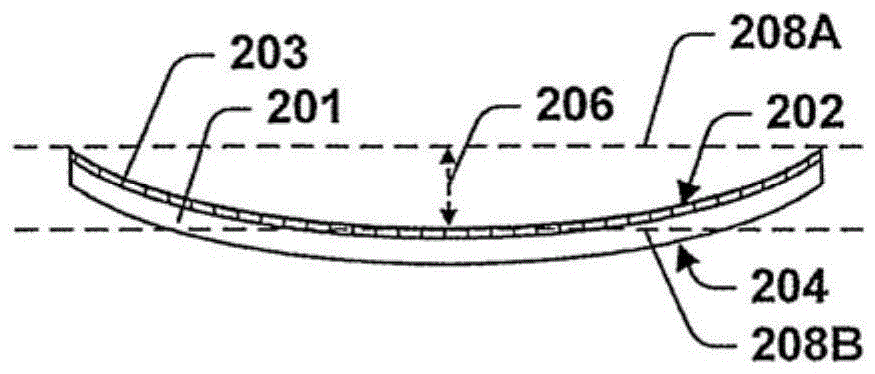

[0043] During the fabrication of integrated circuit devices having deep trench capacitors, the wafer on which the capacitors are formed may become warped. The inventors have found that this bending phenomenon is particularly severe for deep trench capacitors with multiple conductive layers. Bowing can be to the extent that it can adversely affect subsequent processes such as chemical mechanical polishing. Such bowing can be especially problematic for wafers from which 3D-IC devices are formed.

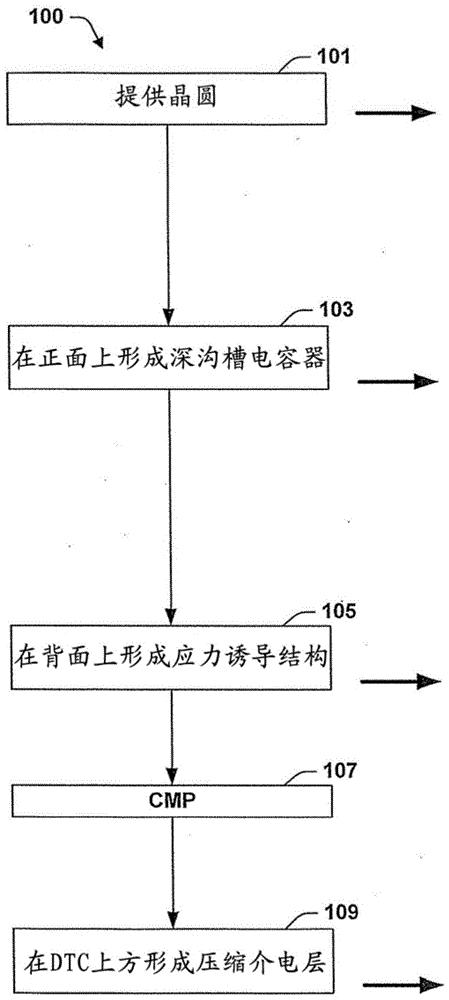

[0044] The inventors solved this problem by forming structures with tensile stress on the backside of the wafer. In some embodiments, these structures are tensile membranes. In some embodiments, these structures include trenches filled with tensile material. Structures located on the backside of the wafer can sufficiently reduce wafer bow to allow further processing. In some embodiments, bowing is further reduced by forming one or more compressive films over the capacitors on the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More