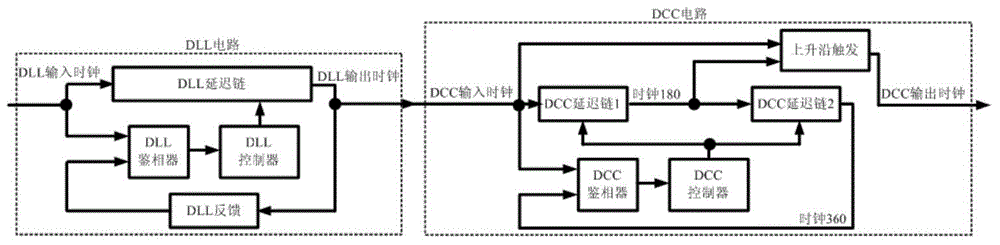

Delay phase-locked loop (DLL) and duty ratio rectification circuit (DCC) structure

A technology of delay phase-locked loop and circuit structure, applied in the direction of electrical components, automatic power control, etc., can solve the problem of inaccurate output duty cycle, and achieve the effect of improving the duty cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Such as image 3 As shown, the delay phase-locked loop and the duty ratio correction circuit of the present invention: first input the first duty ratio correction circuit DCC1 (hereinafter referred to as the DCC1 circuit), then through the delay phase locked loop DLL (hereinafter referred to as the DLL circuit), and finally through the The second duty cycle correction circuit DCC2 (hereinafter referred to as DCC2 circuit) outputs the final clock.

[0026] The first duty ratio correction circuit DCC1 includes a first DCC delay chain and a rising edge trigger, the output end of the first DCC delay chain is connected to the input end of the rising edge trigger, and the DCC input signal is simultaneously input to the first DCC delay chain and the rising edge trigger. Rising edge trigger;

[0027] The delay-locked loop DLL includes a DLL delay chain, a DLL phase detector, a DLL controller and a DLL feedback circuit. The output end of the DLL delay chain is connected to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More