Memory access method and device for a message-based memory module

A message-based memory and memory module technology, applied in static memory, instrumentation, error detection/correction, etc., can solve problems such as power loss and lack of flexibility, and achieve low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] Please refer to figure 1 , an embodiment of the present invention provides a memory access device for a message-based memory module. The device can be deployed in a peripheral control circuit of a memory module, or in a memory controller; the memory controller can be integrated in a central processing unit (Central Processing Unit, CPU) or integrated on a computer motherboard.

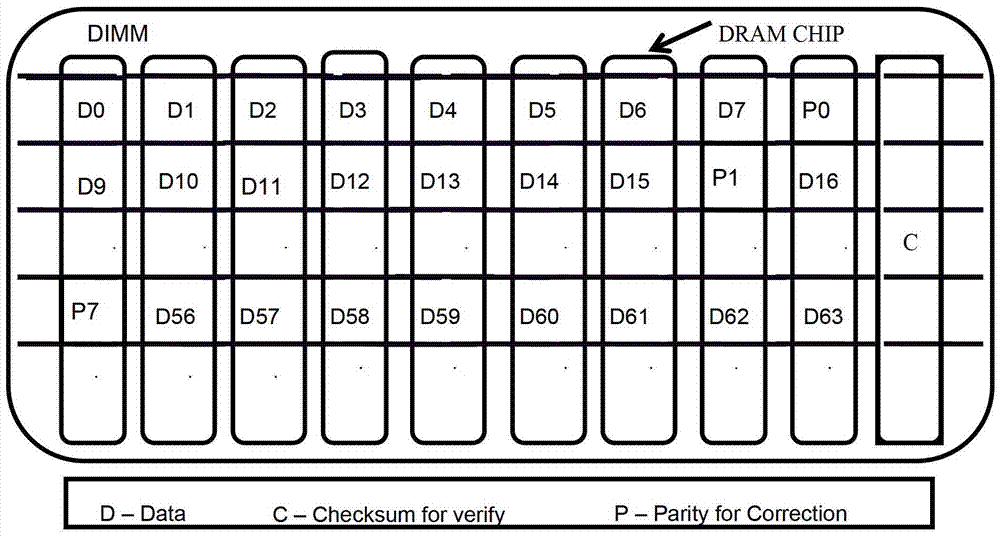

[0030] The memory module may specifically be a DIMM, and the DIMM includes multiple DRAMs. In this paper, it is assumed that the bit width of DRAM is N bits, N is equal to the nth power of 2, and n is a positive integer; the burst length (Burst Length, BL) of DRAM is Q, and Q is a positive integer, preferably Q is equal to several times of 2 Square, for example, it is equal to 4 or 8; assuming that DIMM includes (M+2) blocks of DRAM, (M×N) is the bit width of the entire memory module, because the bit width (M×N) of a computer memory module is generally 2 A number of powers, such as usually 32 ...

Embodiment 2

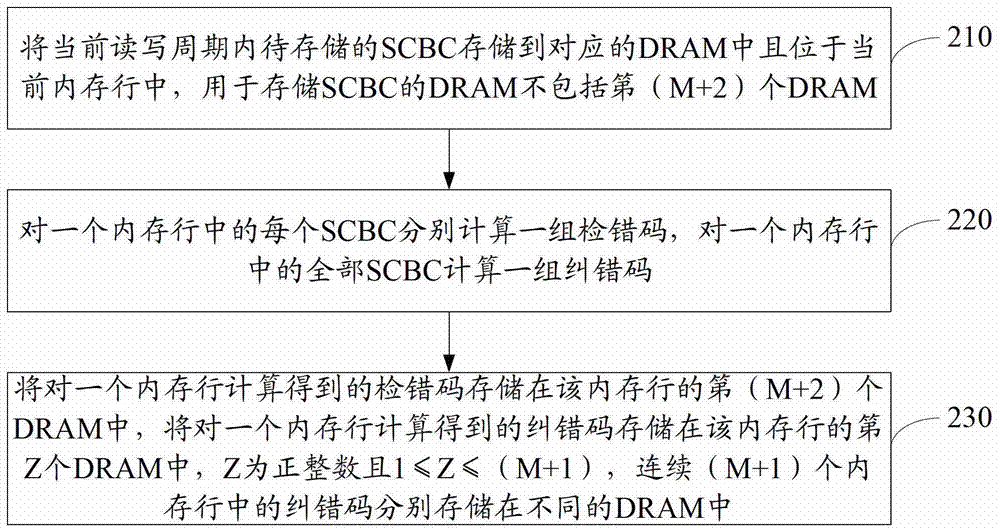

[0065] Please refer to image 3 , the embodiment of the present invention also provides a memory access method of a message-based memory module. The method is executed by a peripheral control circuit or memory controller of the memory module, specifically the memory access device as described in Embodiment 1 deployed in the peripheral control circuit or memory controller. The memory module includes (M+2) block dynamic random access memory (DRAM), M is equal to the m power of 2, and m is a positive integer; The data is called single-chip burst cluster SCBC, and the collection of data stored in all DRAMs that can be accessed in the same read and write cycle forms a memory row.

[0066] The methods include:

[0067] 210. Store the SCBC to be stored in the current read-write cycle into the corresponding DRAM and locate it in the current memory row, and the DRAM used to store the SCBC does not include the (M+2)th DRAM;

[0068] 220. Calculate a set of error detection codes for e...

Embodiment 3

[0080] The embodiment of the present invention also provides a memory control system.

[0081] In one embodiment, as Figure 4a As shown, the system includes a message memory module 310, and the memory module 310 includes a peripheral control circuit 3101 and (M+2) block DRAM 3102;

[0082] Among them, M is equal to the m power of 2, and m is a positive integer; the data stored in each DRAM that can be accessed within one read and write cycle is called single-chip burst cluster SCBC, and the data stored in all DRAMs can be stored in the same The collection of data accessed during a read / write cycle forms a memory row. The memory controller can be integrated on the main board of the computer or in the CPU of the computer.

[0083] The peripheral control circuit performs the following steps:

[0084]The SCBC to be stored in the current read-write cycle is stored in the corresponding DRAM and is located in the current memory row, and the DRAM used to store the SCBC does not in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More