Multi-channel FIFO (First In First Out) buffer and control method thereof

A control method and buffer technology, applied in the fields of instruments, data conversion, electrical digital data processing, etc., can solve the problems that the storage space cannot be effectively used, the data processing bandwidth is reduced, the application is not flexible enough, etc. Fast processing speed, multi-resource or area effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be described in detail below in conjunction with various embodiments shown in the drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

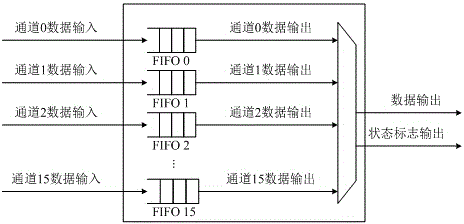

[0052] The FIFO buffer of the present invention includes a plurality of control logics to realize first-in first-out of data of multiple channels.

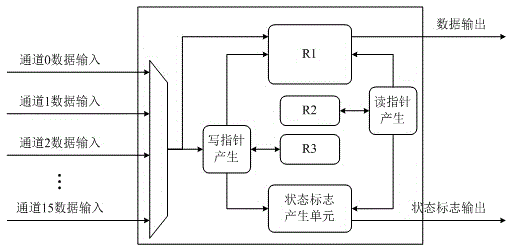

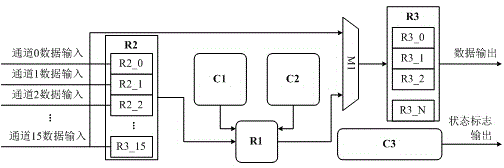

[0053] combine image 3 , Figure 4 As shown, the multi-channel FIFO buffer according to an embodiment of the present invention includes: a data storage module 100 , a read / write pointer control module 200 , a state identification module 300 , and a data selection module 400 .

[0054] In this embodiment, the storage module 100 is used to store data; including: an internal storage unit R1, an input register array R2, an output register array R3, and a first multiplexe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More