A layout processing method for improving photolithography process window

A processing method and technology of photolithography technology, applied in the field of semiconductor manufacturing, can solve the problems of exposing active regions or polysilicon patterns, reducing the yield of finished products, and defects of finished products, so as to reduce the risk of defects, improve the yield of finished products, and increase the optical quality. The effect of engraving the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0026] Please refer to FIG. 1a to FIG. 2b, a layout processing method for improving the photolithography process window of the present invention includes the following steps:

[0027] providing a photolithographic layout, and the photolithographic layout includes a photolithographic layout pattern of a shallow ion implantation layer;

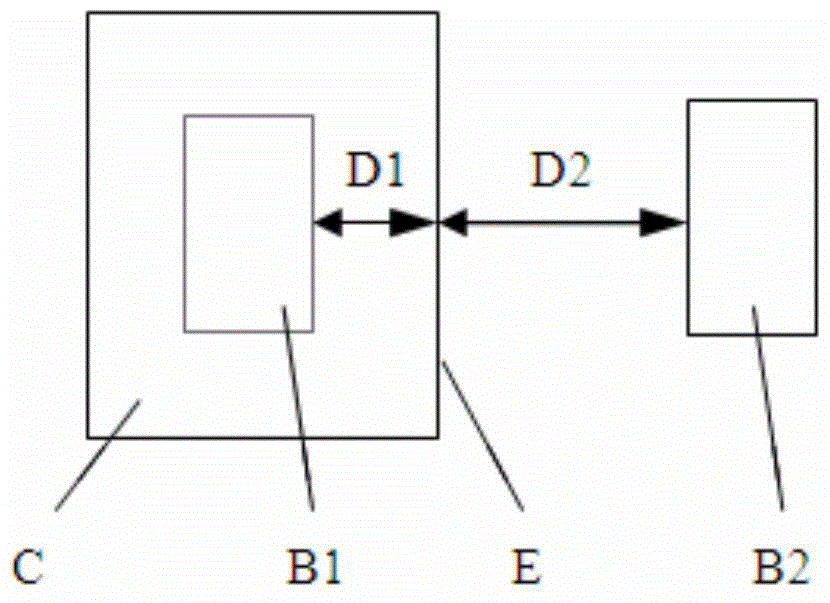

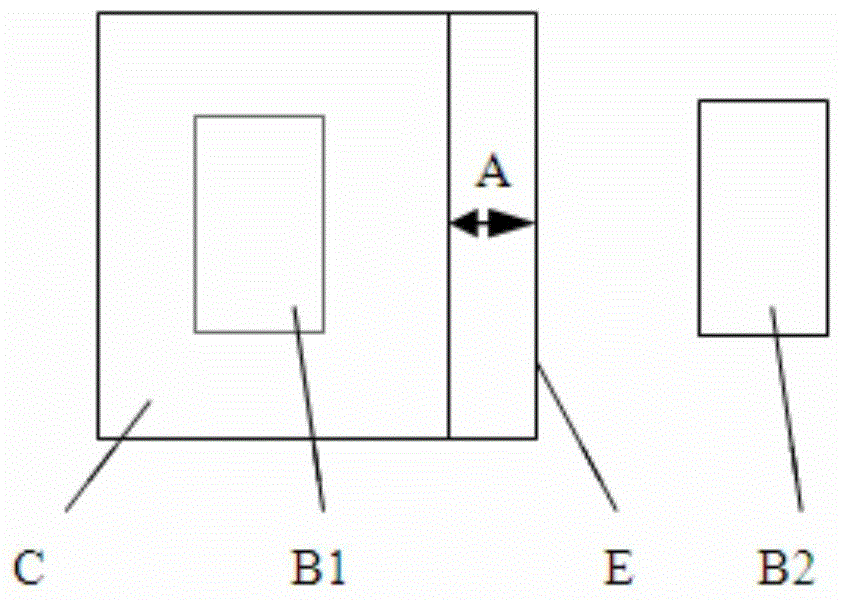

[0028] Find the graphic boundary E falling on the shallow trench isolation region from the photolithographic layout graphics; and the distance from the graphic boundary E to the first front-layer graphic B1 located in the photoresist open area C is the first dimension D1, and at the same time to the first front layer graphic B1 located in the photoresist open area C. The distance of the second front-layer pattern B2 in the photoresist-covered area is the second dimension D2;

[0029] Among them, if the value of the first dimension D1 is smaller than the value of the second dimension D2, the graphic boundary E is moved towards the direction of th...

Embodiment 2

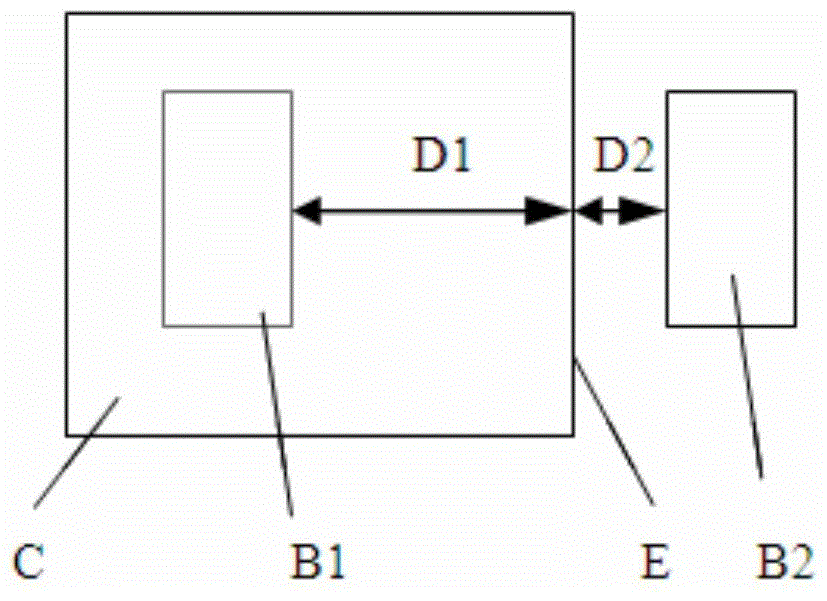

[0048] See Figures 2a and 2b:

[0049] The photolithography layout pattern of the ion implantation layer, the open area of the photoresist pattern is C, and the other area is the coverage area of the photoresist pattern;

[0050] Step 1: Select the pattern boundary E that falls on the shallow trench isolation region, and its distance to the front-layer pattern B1 in the open area C of the photoresist pattern satisfies D1, and the distance to the front-layer pattern in the photoresist pattern coverage area The distance of B2 satisfies D2;

[0051] D1 needs to be selected and adjusted according to the design rules and actual process capabilities, and is the distance from the graphic boundary E to the front-layer graphic B1 in the photoresist pattern opening area C, which is used to select whether it does not meet or is not conducive to the actual process requirements, or is sufficient The boundary that satisfies or far satisfies the actual process requirements; D2 needs to be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com