Multi-core on-chip communication network realization method based on ring bus

A ring bus and on-chip communication technology, which is applied to instruments, electrical digital data processing, etc., can solve the problems of complex layout and wiring, high power consumption, and low connection utilization efficiency, so as to reduce challenges, increase bandwidth, and achieve realizability enhanced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in detail below in conjunction with the accompanying drawings.

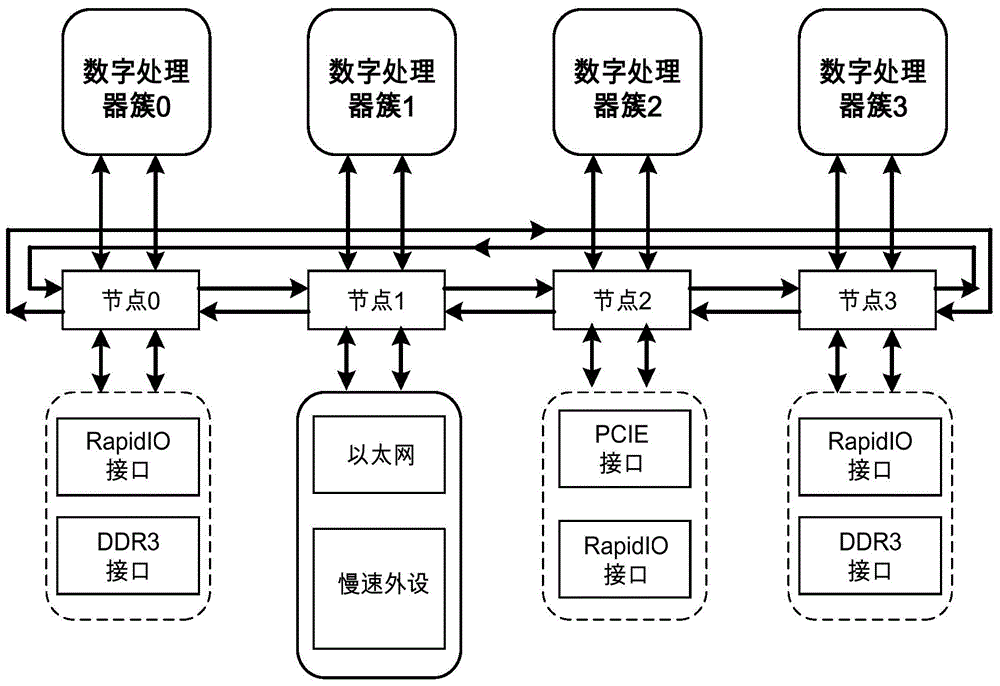

[0027] Such as figure 1 As shown, the ring bus includes 4 nodes, each node is divided into four directions: up, down, left and right, each direction provides 2 channel interfaces, and the left and right direction interfaces are used as bus channels. The upper and lower direction interfaces are used as the interconnection interface between each functional module and the bus. The data width of each interface is 256bit. In addition to the data line, the interface also has some additional control lines for handshaking and Packet start / stop control.

[0028] In the ring bus, above the 4 nodes are digital signal processing (DSP) kernel modules, a total of 4 DSP kernel modules, and multiple DSP kernels can be placed in each DSP kernel module, and these DSP kernels multiplex two and The interface the node is connected to. The bottom of each node is connected to all other ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More