Semiconductor structure and formation method thereof

A semiconductor and interconnection structure technology, applied in the field of semiconductor structure and its formation, can solve the problems of volume increase and chip thickness increase, and achieve the effects of volume reduction, production cost reduction and high integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

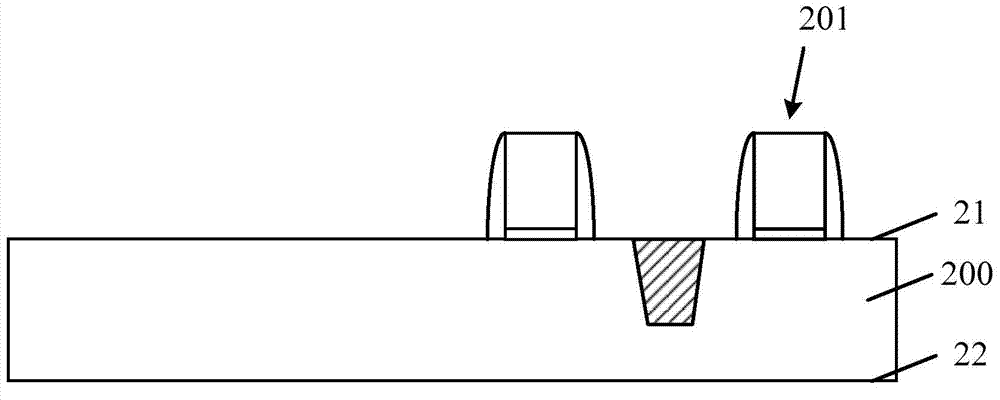

[0031] As mentioned in the background technology, the existing integrated passive devices are integrated on the first substrate, the corresponding CMOS devices are integrated on the second substrate, and then the first substrate and the second substrate are packaged together, but this packaging structure occupies The size is still very large.

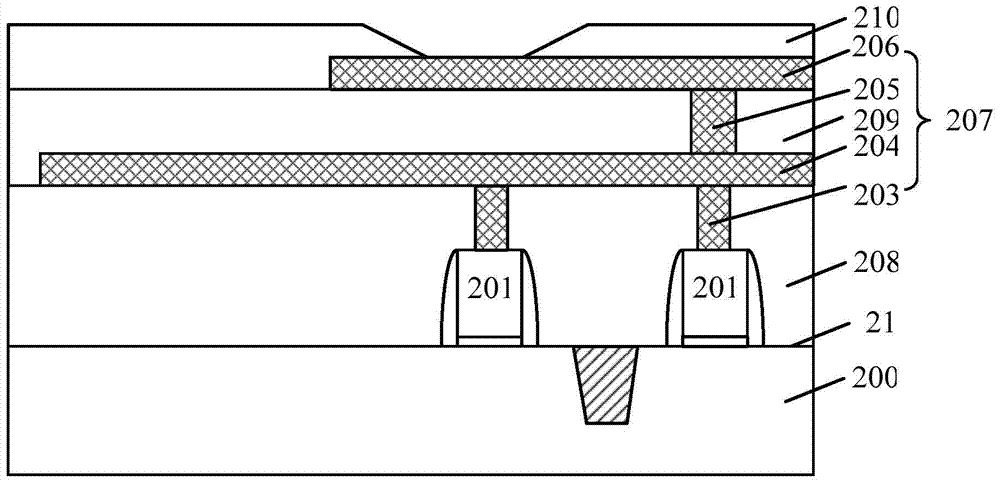

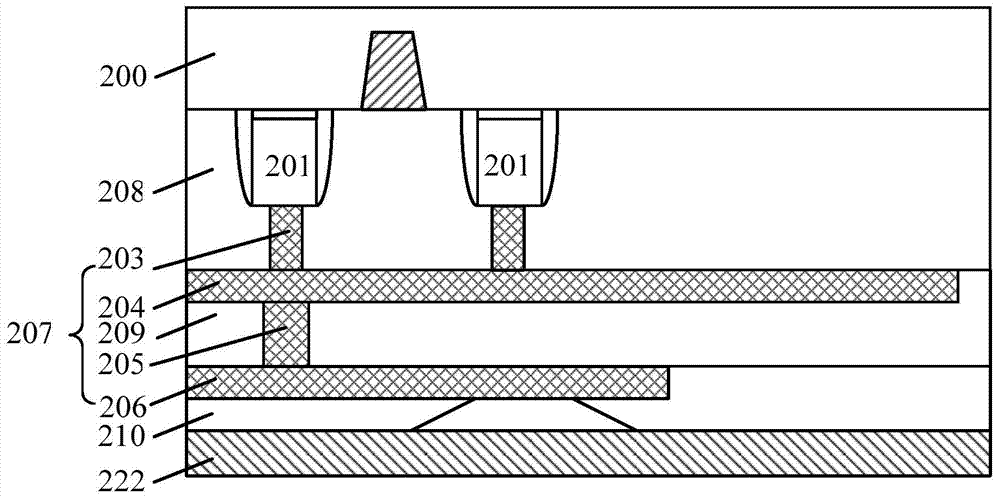

[0032] The present invention proposes a semiconductor structure and its manufacturing method. A CMOS device is formed on the first surface of the semiconductor substrate, and then a passive device is formed on the second surface of the semiconductor substrate. By penetrating the semiconductor substrate and part of the first medium The second metal interconnection layer of the second layer connects the passive device and the CMOS device together, while ensuring the integration of the device, it reduces the volume occupied by the entire semiconductor structure and reduces the manufacturing cost.

[0033] In order to make the above objects...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More