Fan-out wafer level chip packaging method

A chip packaging, wafer-level technology, applied in the direction of electrical components, electrical solid devices, semiconductor/solid device manufacturing, etc., can solve the problems of low I/O terminal density, single structure, high cost, etc., to achieve wide application and multiple structures The effect of changing and enhancing the support strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

[0033] The first specific embodiment: a fan-out wafer-level chip packaging method includes the following steps:

[0034] Such as figure 1 As shown, a carrier plate 1 is prepared, and the carrier plate 1 is made of a glass sheet or a silicon sheet or a ceramic sheet.

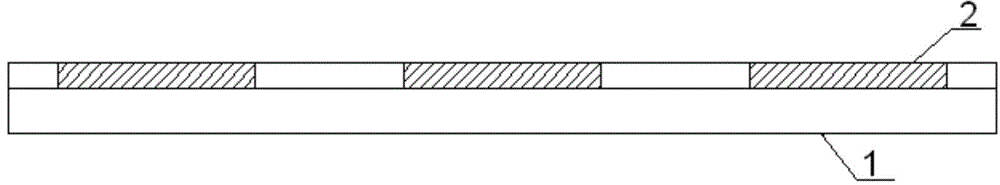

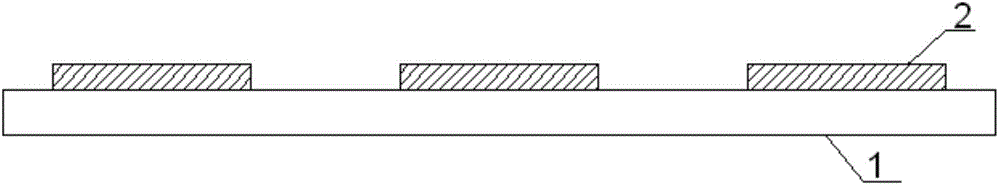

[0035] A conductive base material and a sticking film are formed on the carrier board 1 . A conductive substrate 2 is formed on the carrier 1 . Such as figure 2 as shown, figure 22 in is the conductive substrate 2, where the conductive substrate 2 is preferably a metal coating. Metal plating can be made on the carrier 1 by means of electroplating, electroless plating or sputtering. A film is pasted on the metal coating side of the carrier plate 1 so that the film material is distributed in a certain shape, and part of the metal coating is removed through exposure and development.

[0036] In another optional solution, the step of forming the conductive substrate 2 and the step of affixing a film on the ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More