Clock delay method, clock delay device, delay-locked loop and digital clock management unit

A delay-locked loop and clock delay technology, applied in the field of electronics, can solve the problem of a large difference between the input clock and the output clock, and achieve the effects of low risk, low technical difficulty and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

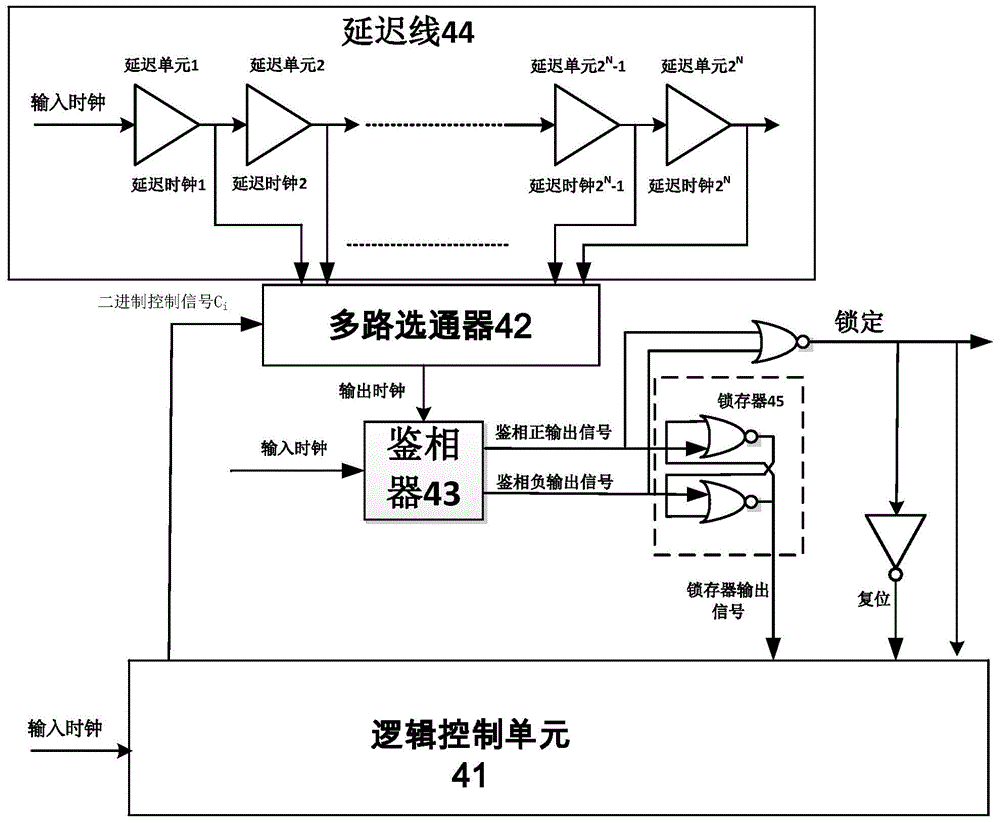

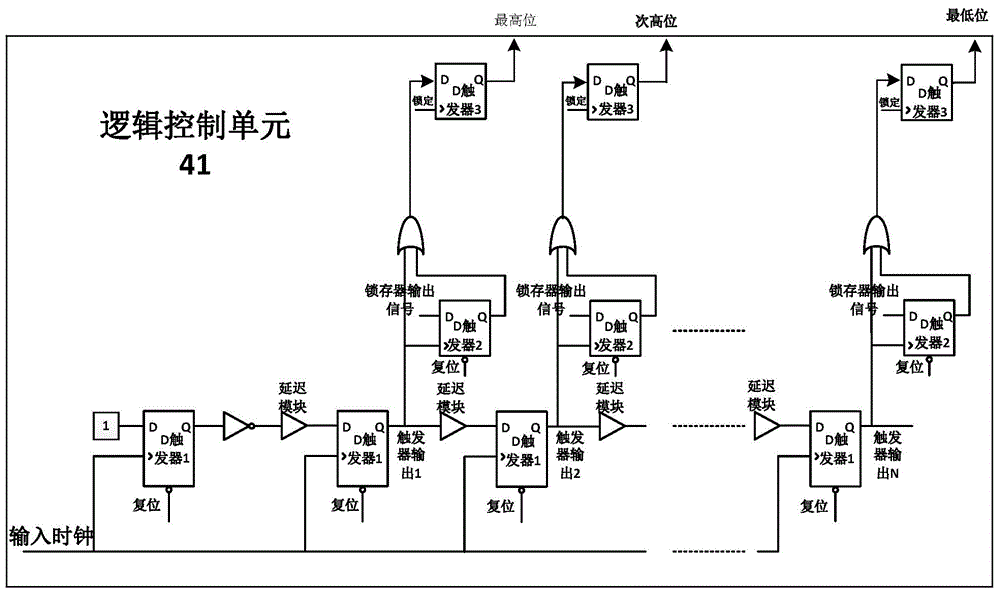

[0027] In order to improve the alignment speed of the input clock and the output clock and speed up the locking speed of the DLL, the present invention proposes the following idea: i Compared with the input clock, the output clock obtained after the input clock still lags behind the output clock, and the input clock is delayed by T through the delay line again. i+1 ,T i+1 for (T i +T x ) / 2, when the input clock is still ahead of the output clock, the input clock is delayed by T′ through the delay line again i+1 , T′ i+1 for (T y +T i ) / 2, and so on until the input and output clocks are aligned. In the case where the input clock still lags behind the output clock, the delay T i is not enough, so at T i with T x This interval takes the middle value (T i +T x ) / 2 re-delay, the input clock is still ahead of the output clock, then the delay T i too large, so the T y with T i This interval takes the middle value (T y +T i ) / 2 to re-delay, and so on, continue to divid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More