Binary capacitor array applied to single-terminal SARADC (Successive Approximation Analog-to-Digital Converter) and redundancy calibrating method of binary capacitor array

A capacitor array and binary technology, applied in the field of SAR ADC calibration, can solve the problems that non-binary capacitor arrays are difficult to achieve matching design, cannot be applied to SARADC, and affect the linearity of SARADC, etc., to achieve good power supply voltage rejection ratio, improve accuracy and linearity The effect of small changes in degree and structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described below in conjunction with the accompanying drawings.

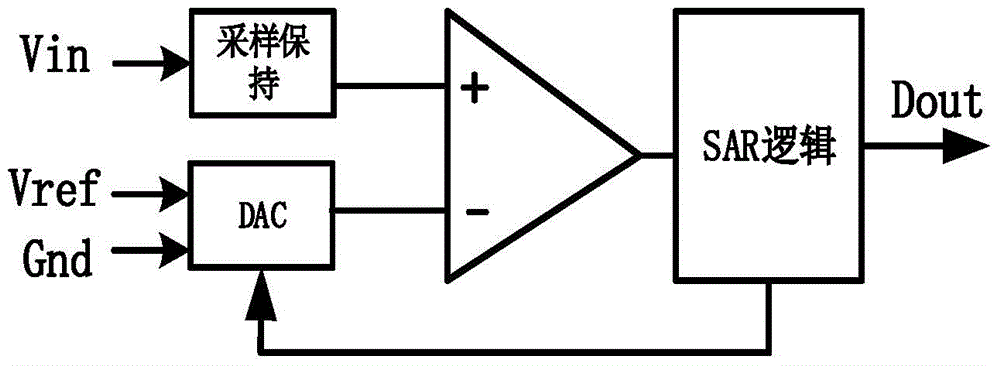

[0036] figure 1 Block diagram of single-ended SAR ADC, including sample-and-hold circuit, comparator, SAR logic, and DAC capacitor array. This structure is easy to understand and is explained in the following operating instructions. The DAC is a binary capacitor array, and its high and low reference levels are Vref and Gnd.

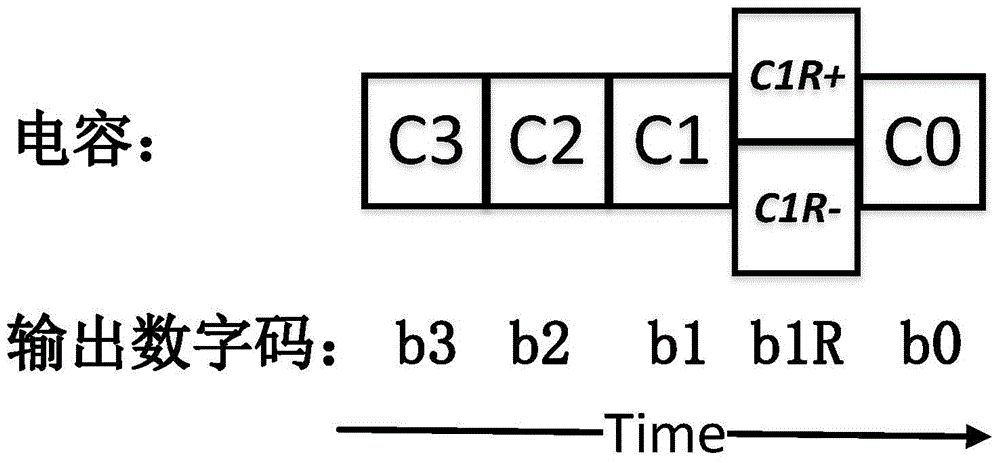

[0037] figure 2 It is a structural diagram of a 4bitDAC redundant capacitor array applied to a single-ended SAR ADC of the present invention, and an additive redundant calibration capacitor C1R+ and a subtractive redundant calibration capacitor C1R- are added after the capacitor C1 of the 4bit binary capacitor array.

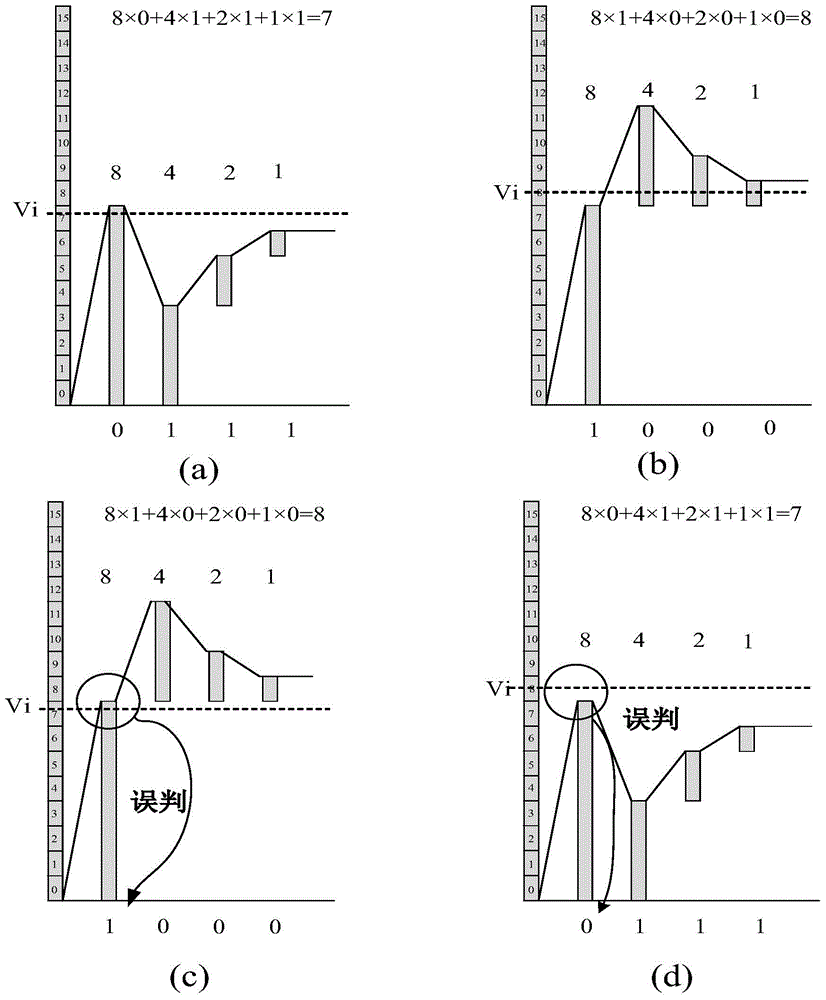

[0038] image 3 It is a 4-bit schematic diagram of the conversion process of single-ended SAR ADC without redundancy calibration. The ordinate represents the input analog signal of the comparator, the straight line correspondi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More