Optimization method for local layout of FPGA chips

An optimization method and layout technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as no good solutions have been proposed, and achieve the effect of realizing FPGA layout and taking into account efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

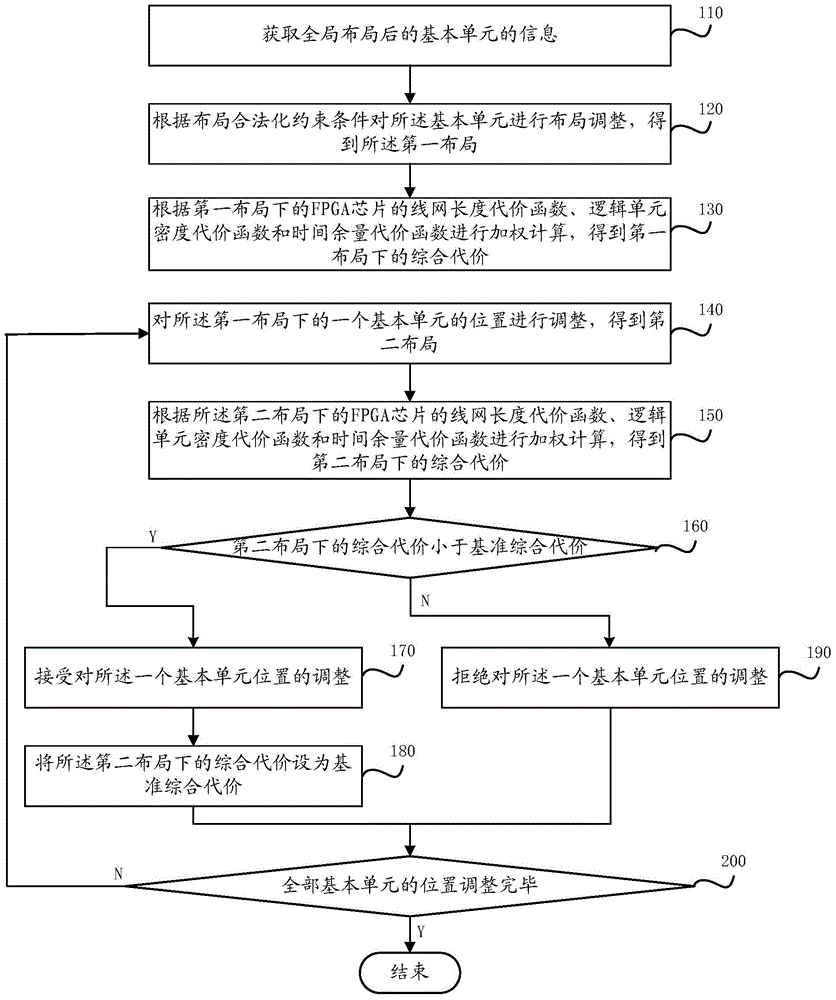

[0036] figure 1 It is a flowchart of a method for optimizing a local layout of an FPGA chip provided by an embodiment of the present invention. As shown in the figure, the method includes the following steps:

[0037] Step 110, obtaining the information of the basic unit after the global layout;

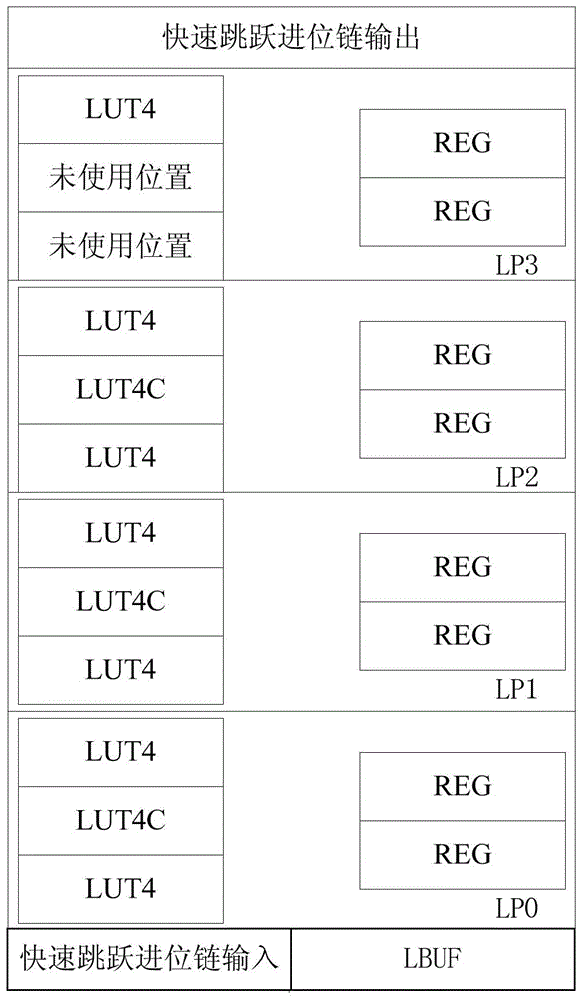

[0038] Specifically, according to the user design, circuit synthesis and library mapping are performed on the user design to obtain the basic unit of the global layout. In an example, the basic unit may include three basic forms: a four-input look-up table (LUT4, LUT4C) and a register (REG), a separate four-input look-up table, and a separate register.

[0039] After the global layout, the lookup tables and registers between the logic elements (Logic Elements, LEs) inside the FPGA chip and within the logic elements are all...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More