Test system for ADC chip characteristic parameter test precision

A technology for testing accuracy and characteristic parameters, applied in the direction of analog/digital conversion calibration/testing, etc., it can solve the problems of complex operation, the performance index of ADC chip cannot meet the accuracy requirements, and the flexibility of logic analyzer is poor, and achieve accurate characteristic test results. , Improve the output driving ability and ensure the effect of accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The specific embodiments of the present invention will be described in more detail below in conjunction with the schematic diagram. According to the following description and claims, the advantages and features of the present invention will be clearer. It should be noted that the drawings are in a very simplified form and all use imprecise proportions, which are only used to conveniently and clearly assist in explaining the purpose of the embodiments of the present invention.

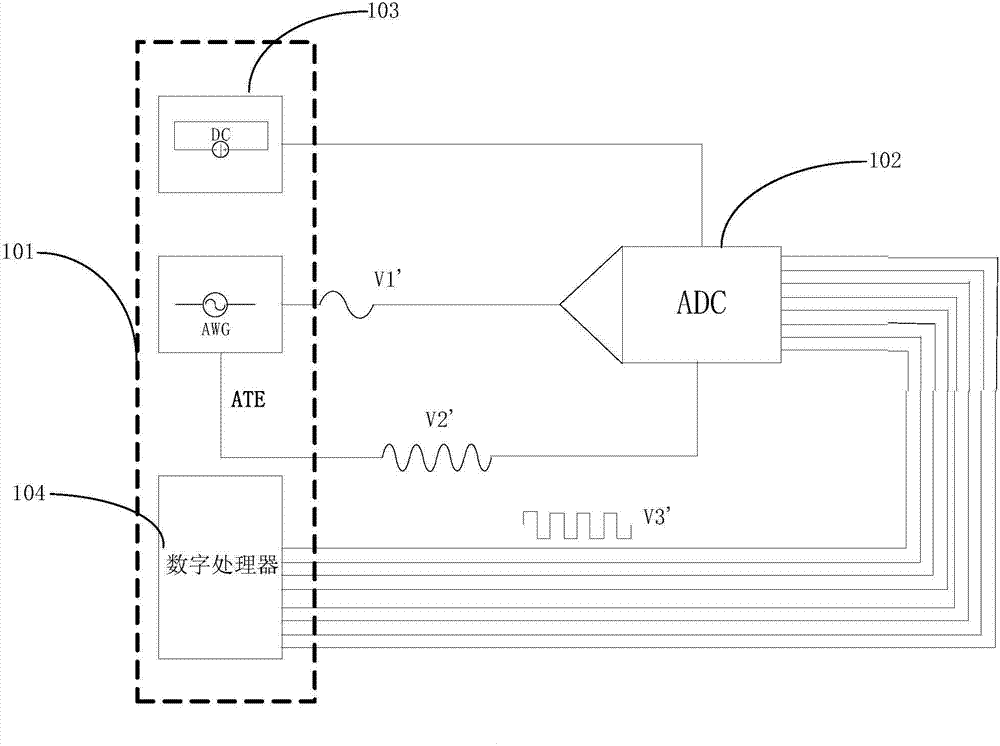

[0028] Such as Image 6 As shown, the present invention provides a test system for testing accuracy of ADC chip characteristic parameters, including: ATE test equipment 201 connected to the input and output ends of the ADC chip 202 under test, and the output of the ADC chip 202 under test A buffer 203 is connected between the terminal and the ATE test equipment 201. The buffer 203 is a high-speed and low-capacitive input buffer that meets the bandwidth requirements of the ADC chip 202 output signal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More