A detection structure and detection method for wafer bonding quality

A detection structure, wafer bonding technology, applied in the direction of semiconductor/solid-state device testing/measurement, electrical components, electric solid-state devices, etc., can solve problems such as inability to accurately measure bonding contact resistance, inability to accurately reflect bonding, etc. , to achieve the effect of simple test structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0054] The test structure of the present invention will be further described below in conjunction with the accompanying drawings.

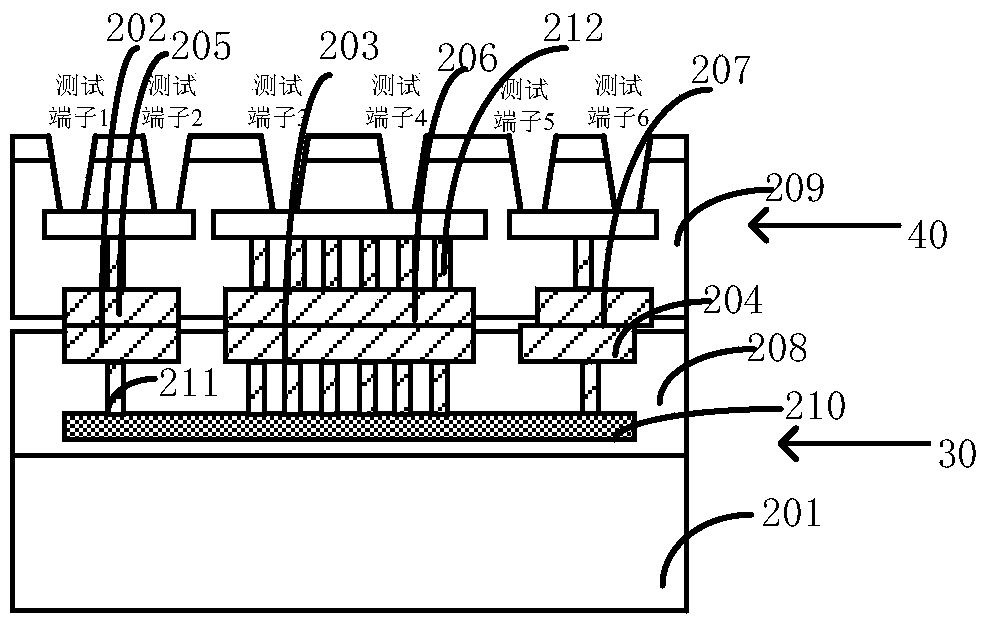

[0055] First, refer to Figure 2a-2b , in the test structure, including a semiconductor substrate 201, the semiconductor substrate 201 may be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI) , Silicon germanium on insulator (S-SiGeOI), silicon germanium on insulator (SiGeOI) and germanium on insulator (GeOI), etc. Active regions may be defined on the semiconductor substrate.

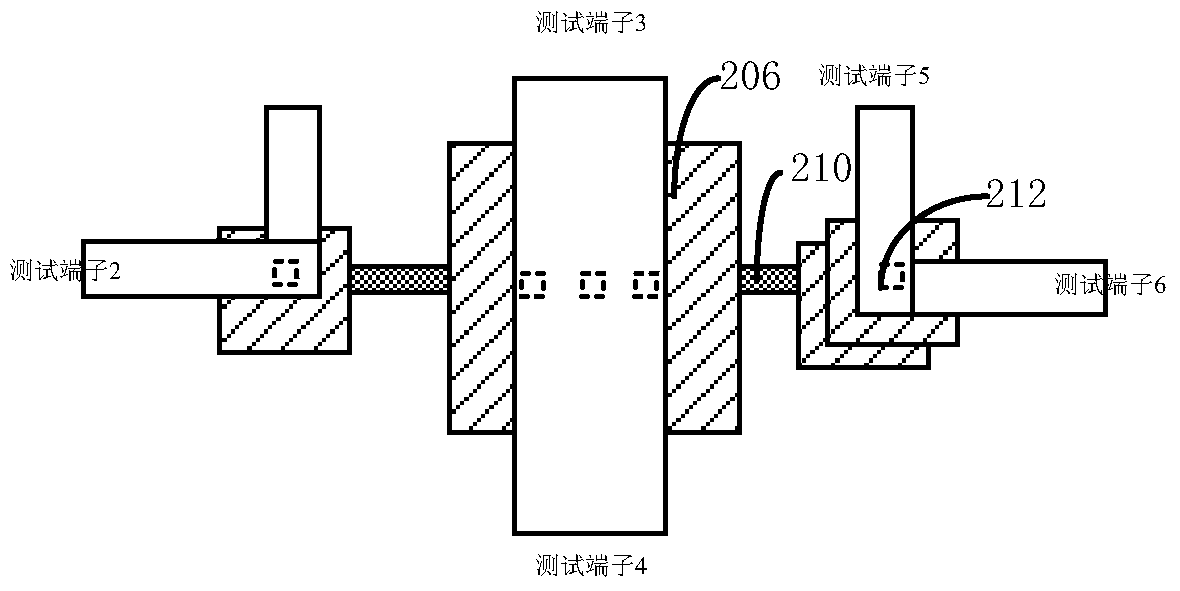

[0056] The test structure includes a bottom wafer 30 and a top wafer 40 bonded to each other, the bottom wafer 30 and the top wafer 40 are bonded to each other through pads, and the bonding of the pads includes a plurality of mutually isolated solder pads. pad, wherein, in the bottom wafer 30, it includes a first bottom pad 202, a second bottom pad 203, and a third bottom pad 204, and a first bottom pad 204 is ...

Embodiment 2

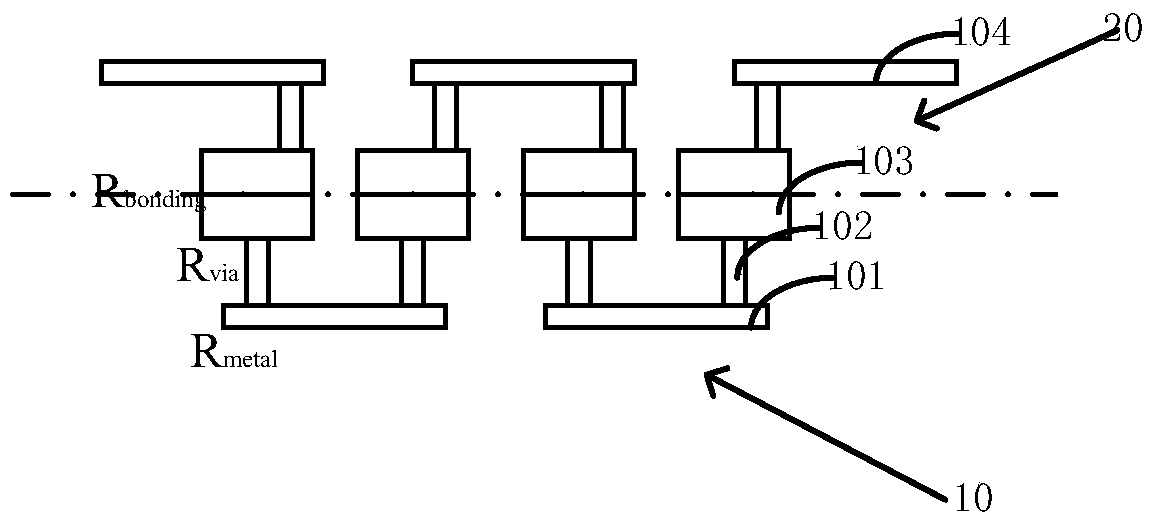

[0080] The present invention also provides a method for selecting the above test structure to detect the bonding of the bottom wafer and the top wafer, wherein image 3 It is an equivalent circuit diagram of the detection structure of the wafer bonding quality in a specific implementation manner.

[0081] The methods include:

[0082] Step (a) applying a voltage on the first test terminal and the third test terminal, testing the voltage between the third test terminal and the fourth test terminal, and calculating a resistance value R1;

[0083] Step (b) applying a voltage on the third test terminal and the fifth test terminal, testing the voltage between the fourth test terminal and the sixth test terminal, and calculating the resistance value R2;

[0084] Step (c) calculating a junction resistance between said third top pad and said third bottom pad based on R1 and R2.

[0085] Specifically, the step (c) also includes the following sub-steps:

[0086] Step (c-1) said R1=R ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More