Flip Chip Stacked Package

A flip-chip and chip technology, applied to electrical components, electrical solid devices, circuits, etc., can solve the problems of poor heat dissipation efficiency of the bottom chip, and achieve the effects of improving heat dissipation efficiency, reducing manufacturing costs, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the advantages, spirit and characteristics of the present invention more easily and clearly understood, the following will be described and discussed in detail with reference to the accompanying drawings. It should be noted that these embodiments are only representative embodiments of the present invention, and the specific methods, devices, conditions, materials, etc. exemplified therein are not intended to limit the present invention or the corresponding embodiments.

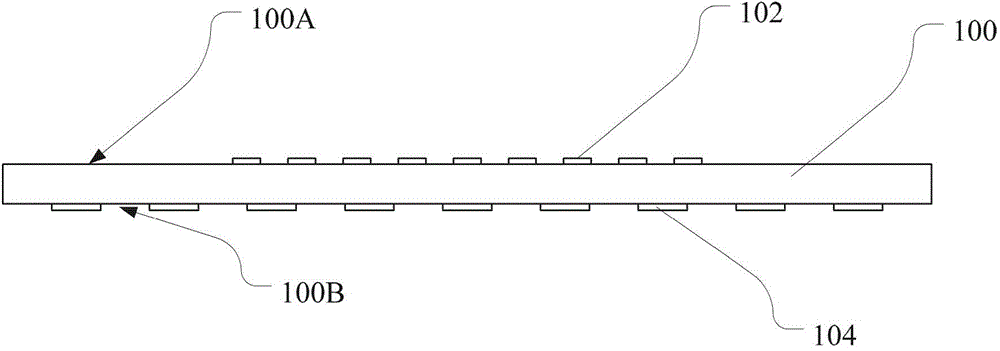

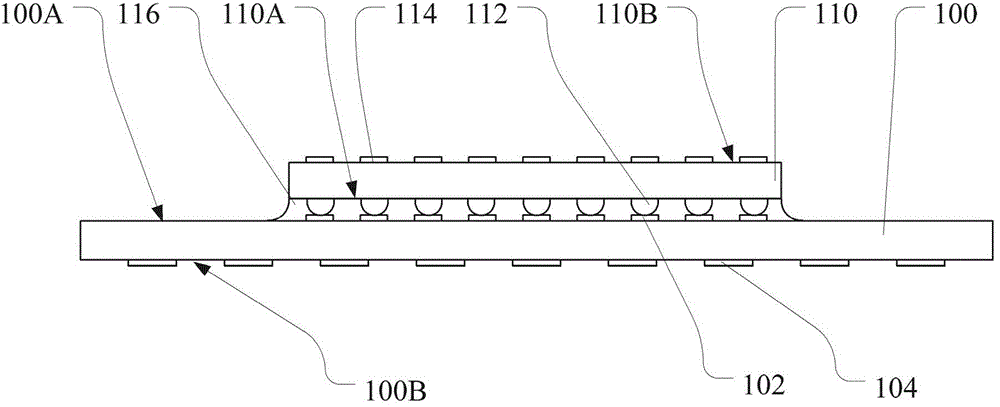

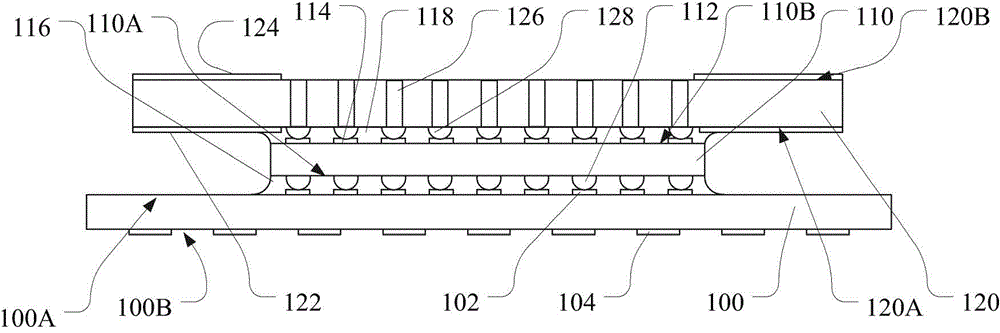

[0040] Please refer to Figure 1 to Figure 4 , Figure 1 to Figure 4 A schematic cross-sectional view showing various steps of a method for manufacturing a flip-chip stack package according to an embodiment of the present invention. The manufacturing method of the flip-chip stacked package of the present invention comprises the following steps: first please refer to figure 1, providing a packaging substrate 100, the packaging substrate 100 has an inner surface 100A and a corresponding ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com