Capacitance mismatch calibrating circuit and calibrating method applied to single-end SAR ADC

A capacitance mismatch and calibration circuit technology, which is applied in the field of SAR ADC calibration, can solve the problems of establishment time limit, power consumption increase, chip cost increase, etc., and achieve the effects of saving power consumption and area, calibrating dynamic errors, and being easy to implement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be further described below in conjunction with the accompanying drawings.

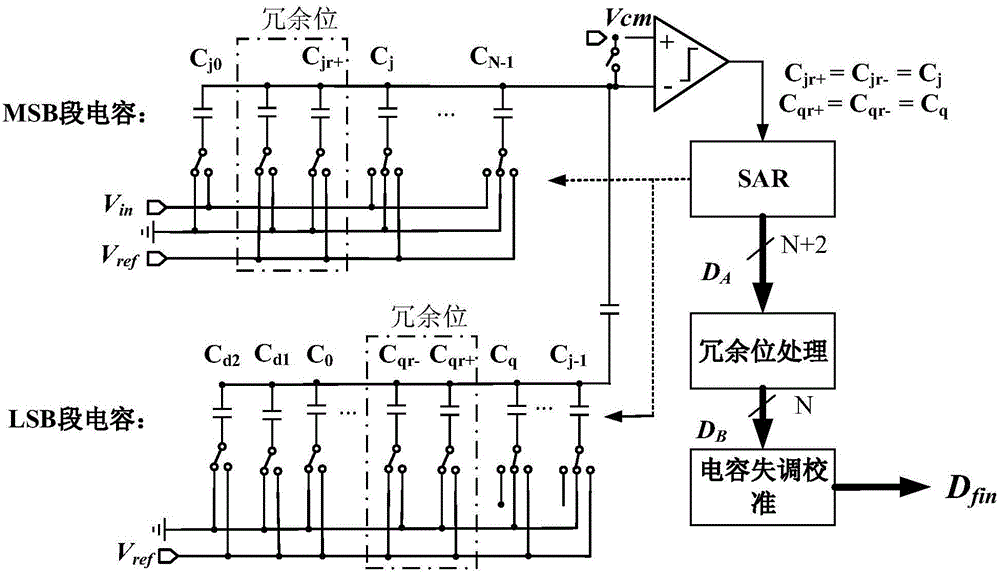

[0045] The invention proposes to calibrate the capacitance array based on the single-end 14bit binary redundancy, and calibrates the capacitance array to improve the precision of the ADC. Since the invention is based on redundant capacitance calibration. Therefore, the redundant capacitance calibration of the single-ended SAR ADC will be described first.

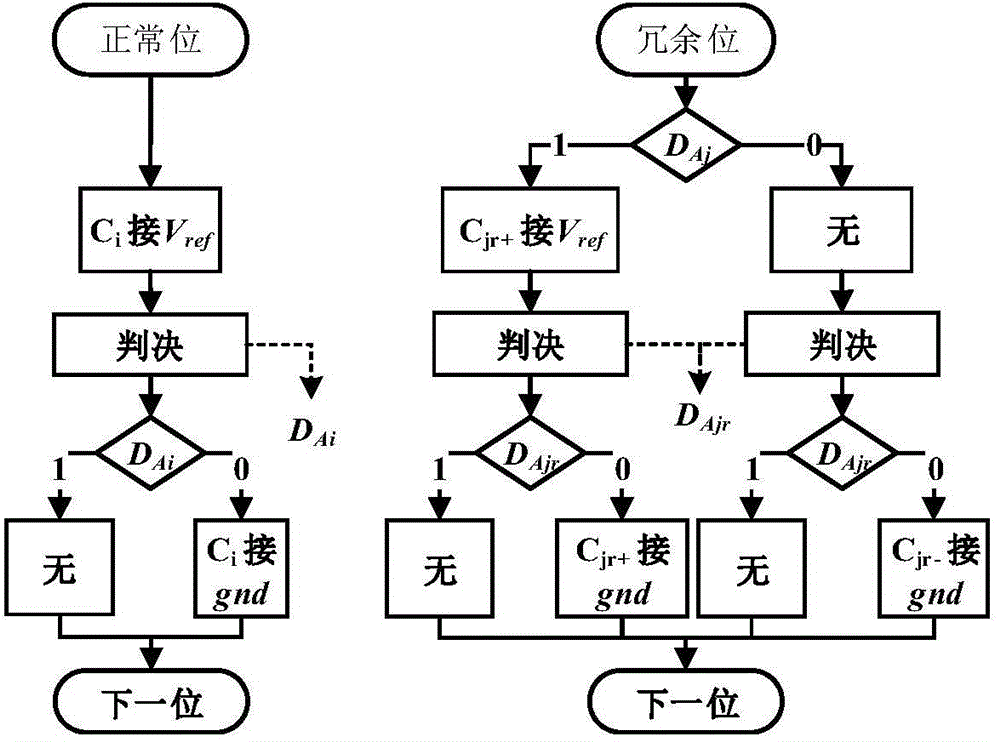

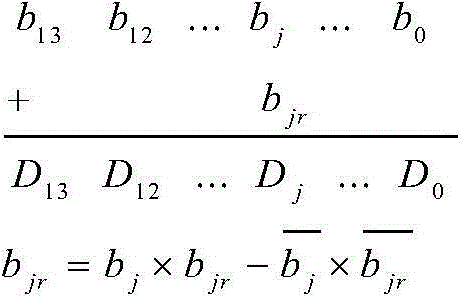

[0046] figure 1 Calibration procedure for single-ended SAR ADC redundancy. It can be seen from the figure that the operation process of its non-redundant bit is exactly the same as that of a normal single-ended SAR ADC. And when converted to redundant bit C jr+ and C jr- When , first check the C in front of the redundant bit j Make a judgment, if bj is 1, enter the branch of positive compensation, namely Cjr+; if bj is 0, enter the branch of negative compensation, namely Cjr-. When entering the positive compen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More