Configurable fractional frequency divider

A fractional frequency divider, counting value technology, applied in pulse counters, counting chain pulse counters, special data processing applications, etc. and other issues, to achieve the effect of improving versatility and flexibility, low circuit complexity, and reducing area and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further elaborated below in conjunction with embodiment.

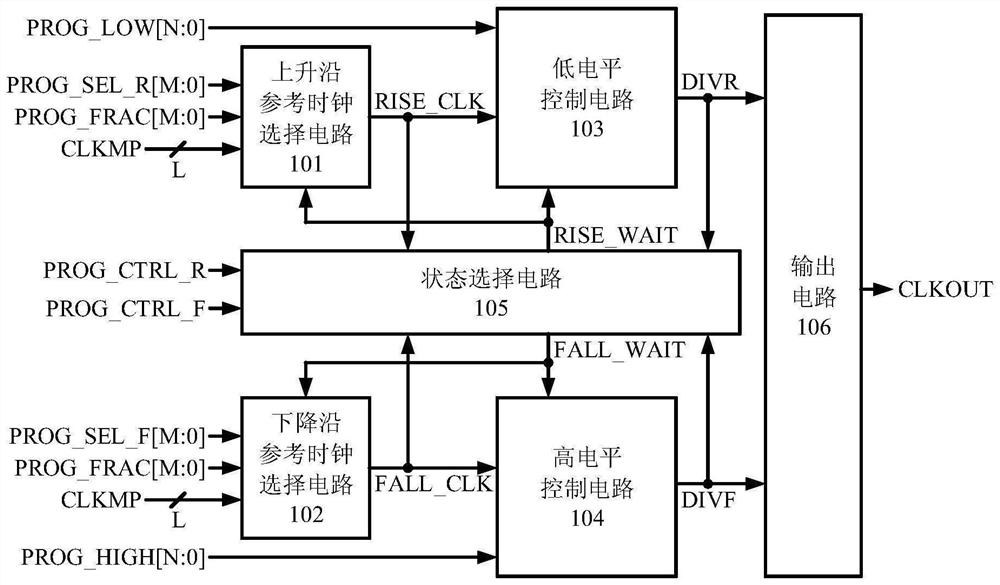

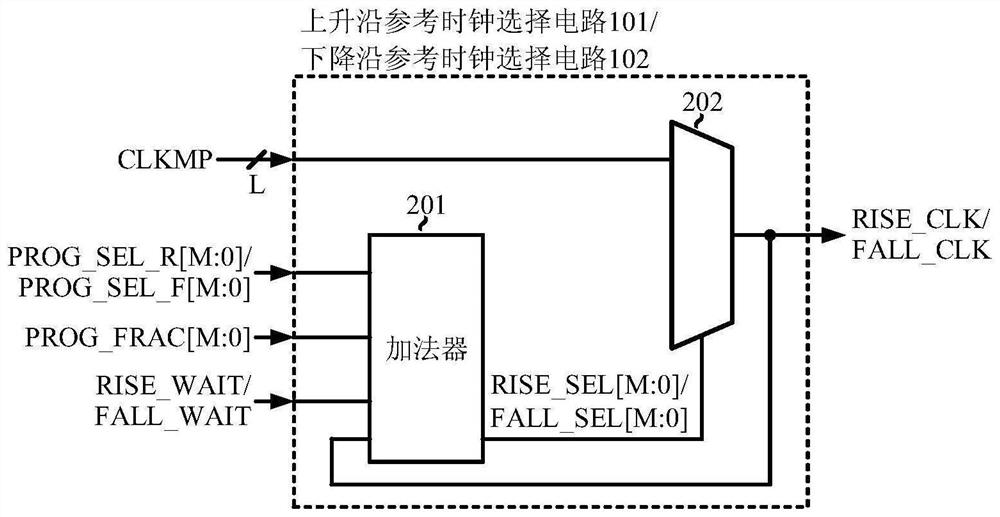

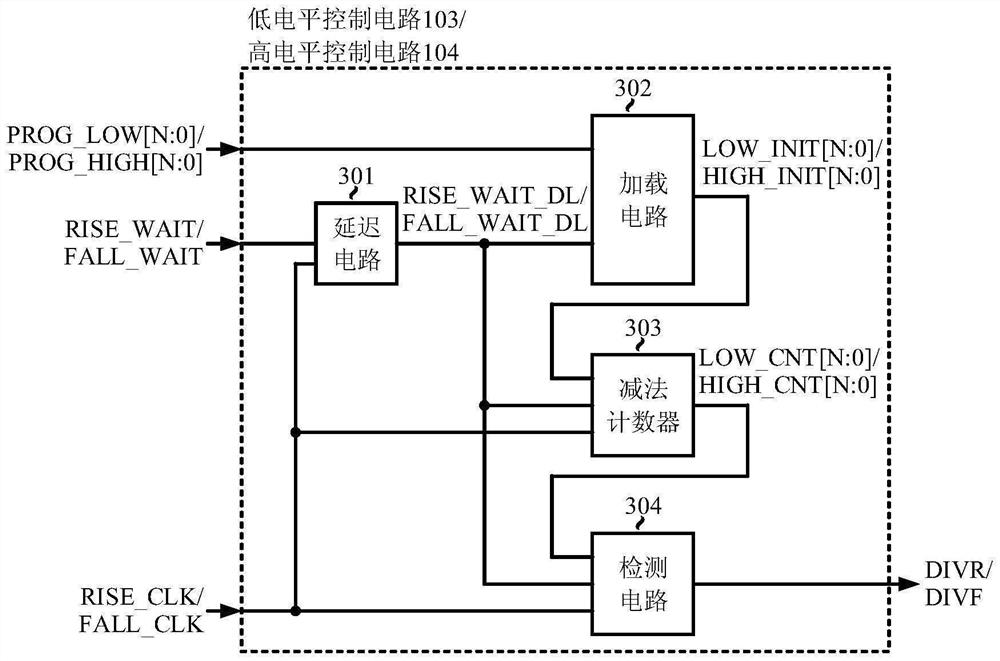

[0026] figure 1 It is a schematic diagram of the overall structure of the configurable fractional frequency divider of the present invention. The fractional frequency divider includes a rising edge reference clock selection circuit 101 , a falling edge reference clock selection circuit 102 , a low level control circuit 103 , a high level control circuit 104 , a state selection circuit 105 and an output circuit 106 . Wherein, the rising edge reference clock selection circuit 101 and the falling edge reference clock selection circuit 102 adopt the same circuit structure, and the low level control circuit 103 and the high level control circuit 104 adopt the same circuit structure.

[0027] Define the fractional frequency division value as I.F, where I is the integer part of the frequency division value and F is the fractional part of the frequency division value. The configurable fra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More