Automatic chip power-on reliability detection device and detection method

An automatic detection device and reliability technology, applied in the direction of electronic circuit testing, etc., can solve problems such as errors, unsuitability, and inaccurate measurement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0073] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

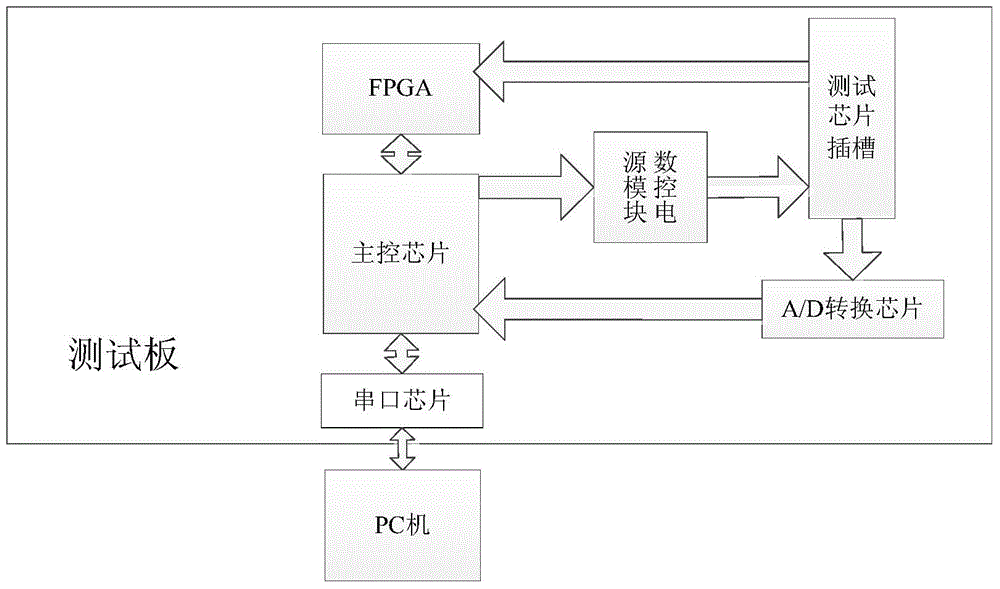

[0074] Such as figure 1 As shown, the present invention provides an automatic detection device for chip power-on reliability, including a PC for running test software and a test board for chip testing. The PC is connected with the test board through a serial port cable and communicates.

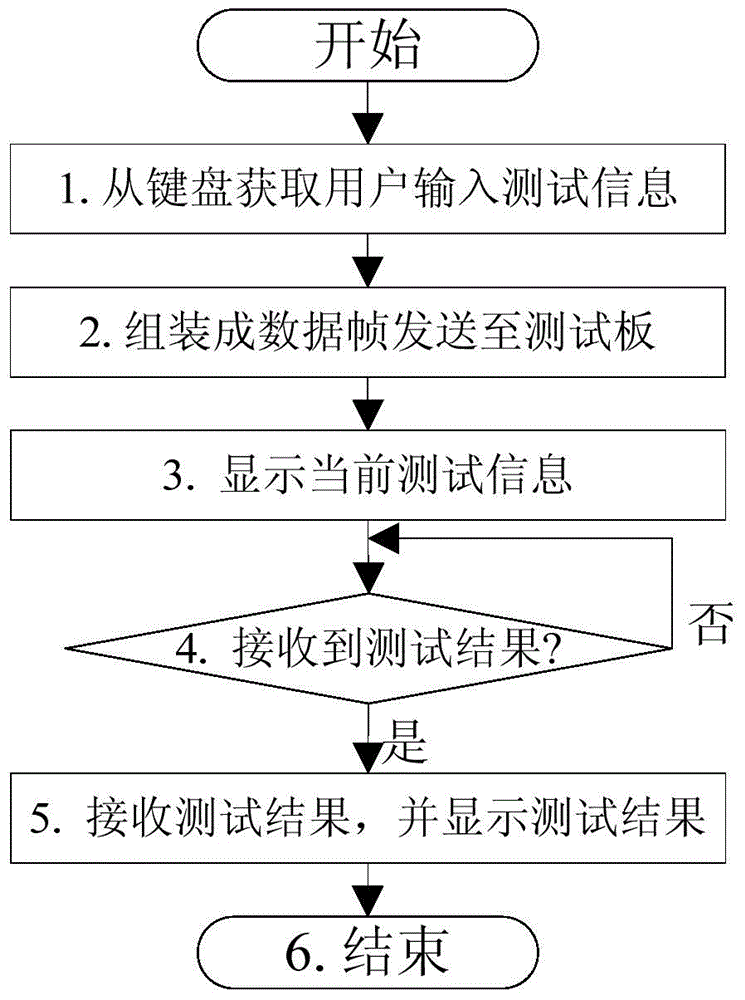

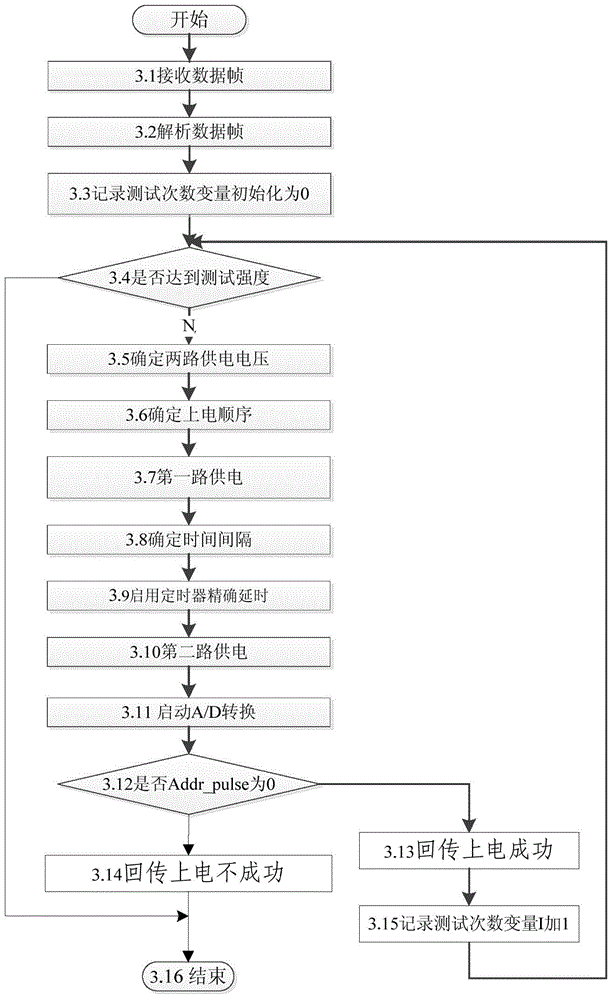

[0075] The test software is installed in the PC, and the test software receives the chip type, test intensity (that is, the number of repeated power-on times), power-on sequence (core power supply first, then I / O power supply, or vice versa) and power-on voltage value input by the tester. And the control information of the time interval (that is, the time difference between power-on of the core and I / O, in order to avoid damage to the chip caused by too long interval, the time difference is limited to 1s by software judgment), and the test software ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More