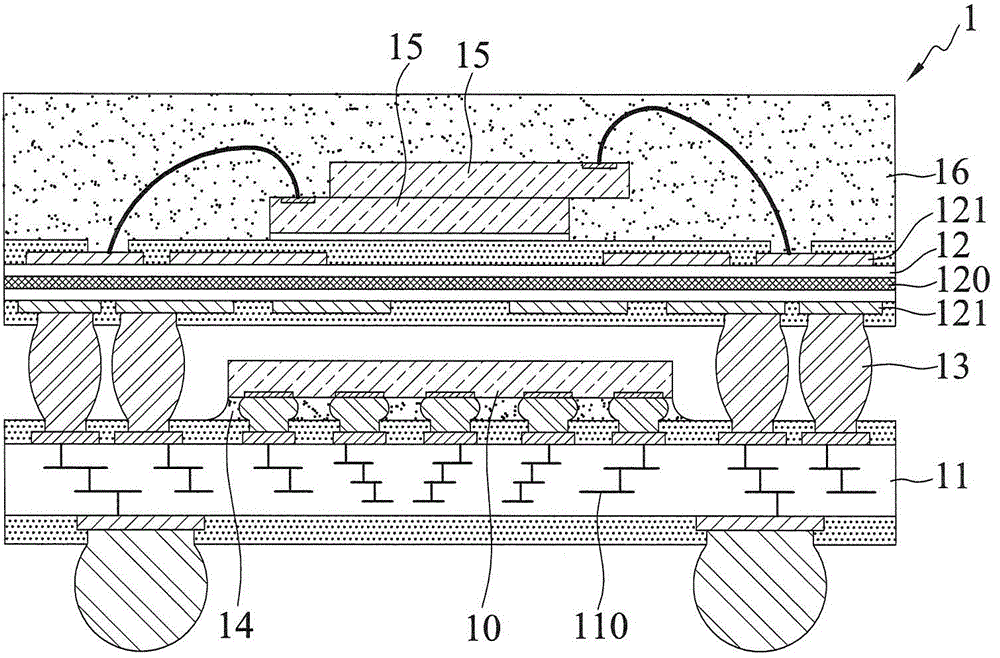

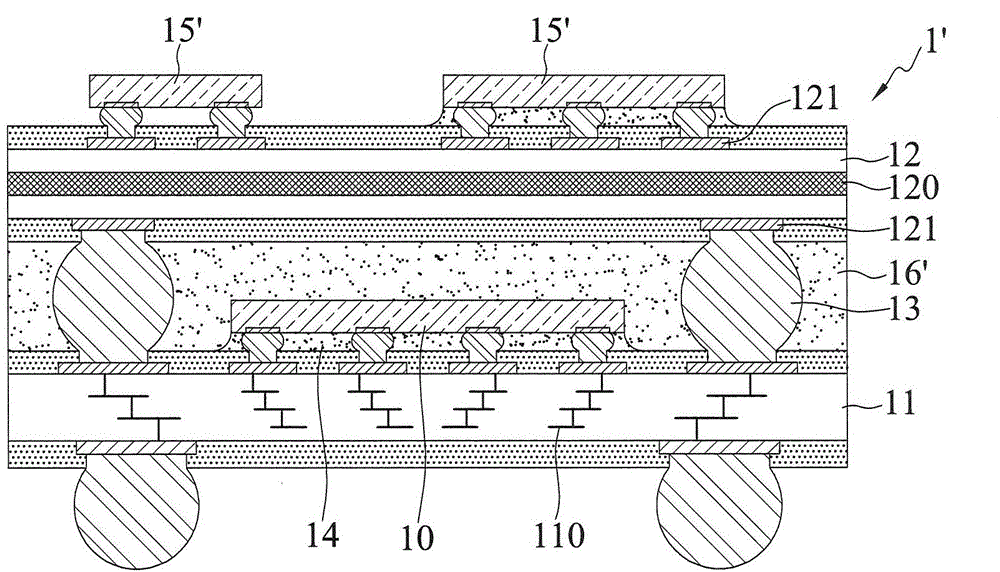

Coreless packaging substrate, pop structure, and methods for fabricating the same

A packaging substrate, no core layer technology, applied in the field of packaging stack structure and its manufacturing method, can solve the problems of poor coplanarity, low product yield, difficult to comply with thinning, etc., to reduce materials and process, improve product quality Yield rate, effect of avoiding bridging phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

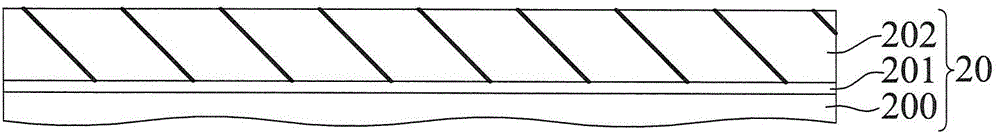

[0064] The implementation of the present invention will be described below through specific specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification.

[0065] It should be noted that the structures, proportions, sizes, etc. shown in the drawings attached to this specification are only used to match the content disclosed in the specification, for the understanding and reading of those skilled in the art, and are not used to limit the implementation of the present invention. Limiting conditions, so there is no technical substantive meaning, any modification of structure, change of proportional relationship or adjustment of size, without affecting the effect and purpose of the present invention, should still fall within the scope of the present invention. The disclosed technical content must be within the scope covered. At the same time, terms such as "above", "firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More