A Wear Leveling Method for Variable Resistive Memory Based on Software Compilation Layer

A technology of resistive memory and wear leveling, which is applied in the direction of memory address/allocation/relocation, input/output to record carrier, etc., can solve the problems of limiting the practical application of variable resistive memory, not small overhead, etc., and achieve fine detail Granularity, improved service life, and low storage overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Below in conjunction with accompanying drawing and embodiment the present invention will be further described:

[0019] The present invention comprises the following steps:

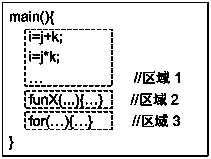

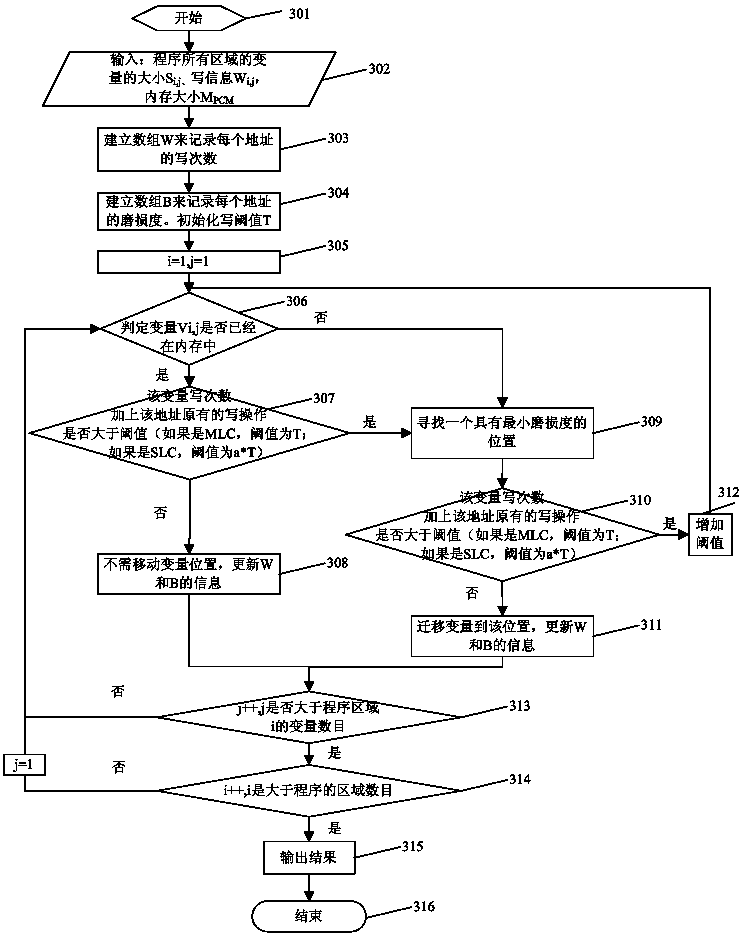

[0020] Step 1. According to the characteristics of the program, the program is divided into multiple program areas, and the number of write operations and the size of each variable are counted;

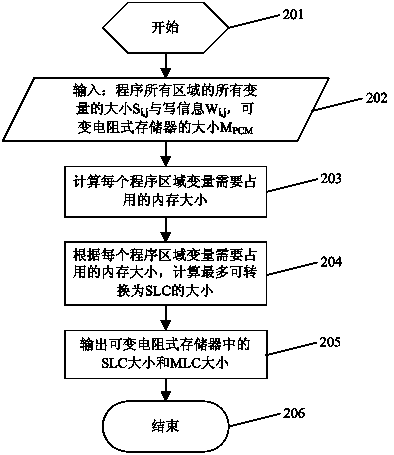

[0021] Step 2, according to the size of the unoccupied space of the memory, dynamically configure the size of the single-layer unit and the multi-layer unit of the variable resistance memory;

[0022] Step 3. Allocate appropriate addresses for each variable, allocate high-performance and long-life SLC for frequently written variables, and allocate large-capacity MLC for infrequently written variables, thereby reducing the access delay of variable programs and improving variable Resistive memory lifetime;

[0023] Step 4. Execute the compiled program on the embedded system to obtain wear leveling on the v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More