Method and system for generation of downlink scrambling code sequence in WCDMA system

A technology of scrambling code sequence and generating method, which is applied in the field of generation of downlink scrambling code sequence of WCDMA system, can solve the problems of multiple hardware resources, memory consumption, low processing efficiency, etc., so as to improve the scrambling code output efficiency, reduce resource occupation, improve The effect of processing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] A method for generating a WCDMA system downlink scrambling sequence, comprising the steps in the following order:

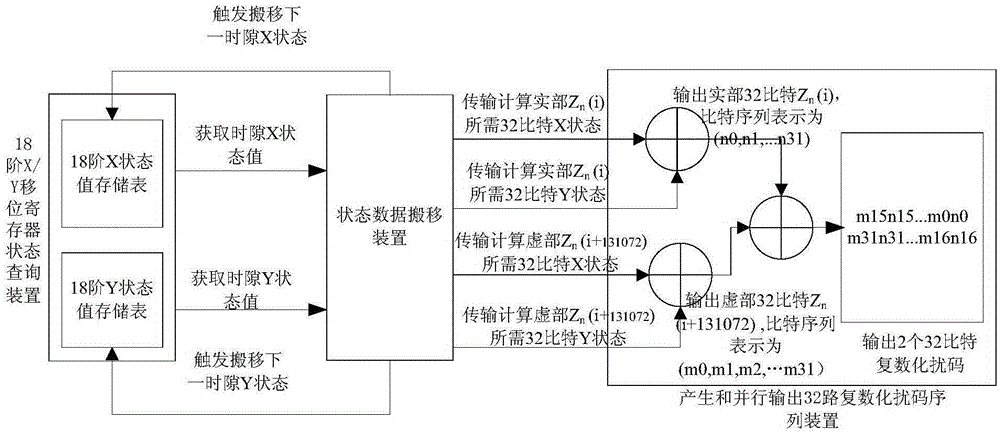

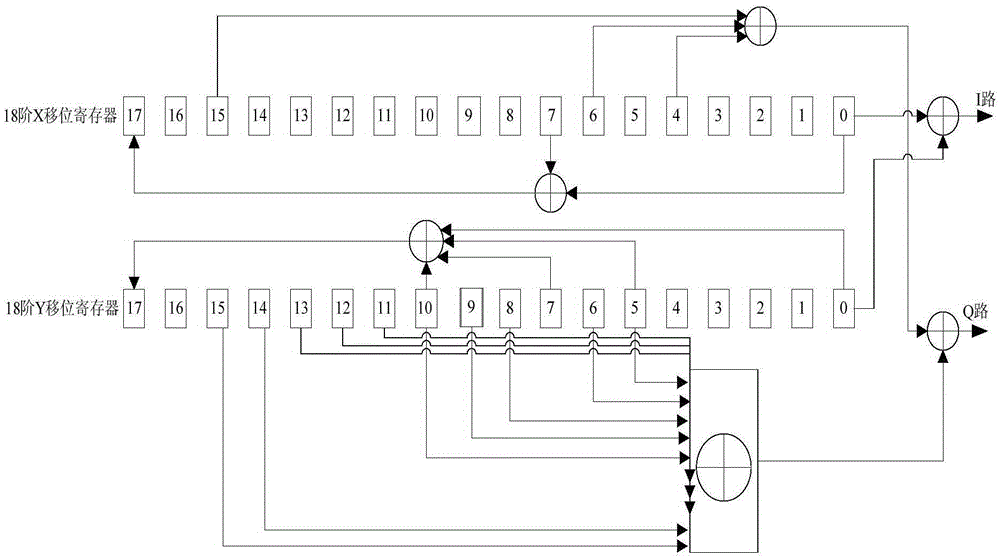

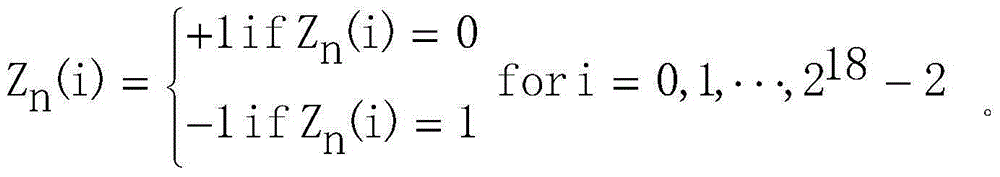

[0050] S1. According to the scrambling code generation device stipulated in the agreement 3GPPTS25.213, such as figure 2As shown, using the device and the initial value of the X / Y sequence specified by the protocol, the state values of the X / Y18-stage shift register can be generated respectively, and the state values are stored in bits and stored in the slow memory. The X / Y state value required for generating complex scrambling code sequence operations per time slot is located in the fast memory, and the real part of the scrambling code sequence is calculated according to the scrambling code number (range 0 to 8191) and the length offset of the complex scrambling code sequence per time slot. The starting position of the state data required by the imaginary part;

[0051] S2. According to the location of the X / Y state sequence storage required to gene...

Embodiment 2

[0058] The invention provides a method for generating downlink scrambling codes in a WCDMA system, which can quickly generate complex scrambling code sequences corresponding to arbitrary downlink scrambling code numbers.

[0059] (1) First, pre-store the status value of the 18th-order X / Y register, and the X / Y status value is currently based on the following figure 2 The shown scrambling code generation circuit produces, combined with the X / Y state register initial phase X (0) = 1, X (1) = X (2) = ... X (16) = X (17) = 0, Y (0 )=Y(1)=…=Y(16)=Y(17)=1, store the value of X\Y state register successively in order, there are 2 in total 18 status. The bit storage is about 8192Word, and the X / Y sequence occupies a total storage space of 16384Word. Considering that it takes up a lot of space, the X / Y status register table is placed in the external slow memory. Calculate the X / Y state value offset according to the downlink scrambling code number and the slot scrambling code length, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More