Flip chip failure analysis method and preparation method of detection sample in electric property positioning

A technology for failure analysis and sample detection, which is applied in the testing/measurement of circuits, electrical components, semiconductors/solid-state devices, etc. It can solve the problems that gold bumps cannot be packaged and re-wired, and the failure analysis that affects the positioning of electrical bright spots, etc., to achieve Avoid the effect of being corroded

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

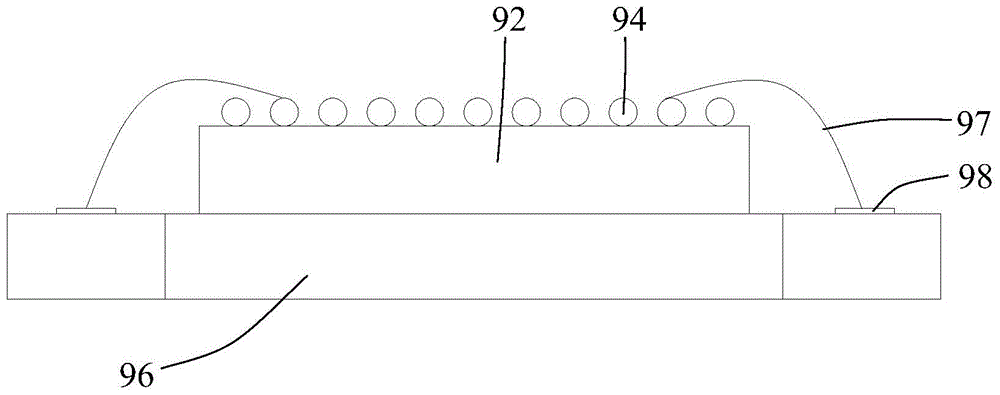

[0054] Cooperate with reference Figure 4 ~ Figure 7 as shown, Figure 4 It is a flow chart of the preparation method of the detection sample in the electrical positioning of the failure analysis of the flip-chip chip. Figure 5 ~ Figure 7 It is an exploded view of the steps of the preparation method of the detection sample in the electrical positioning of the failure analysis of the flip-chip chip of the present invention. The preparation method of the flip-chip chip failure analysis and detection sample of the present invention comprises:

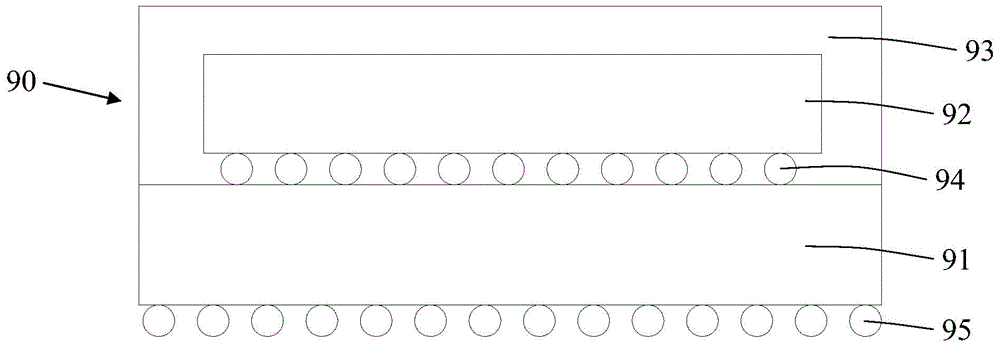

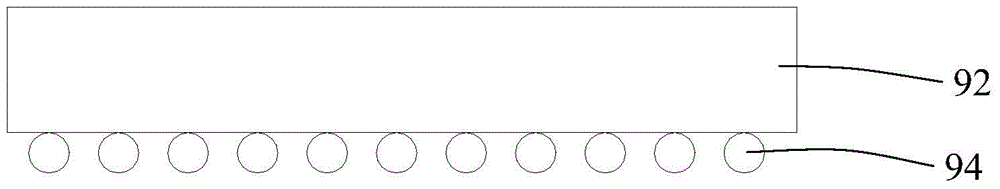

[0055] Step S101 : combine Figure 5 As shown, a flip chip 10 to be tested is provided. The flip chip 10 includes a package substrate 11 and a die 12 prepared on the package substrate 11. The outside of the die 12 is covered with a plastic package 13. The die 12 and the package substrate 11 Gold bumps 14 are connected between them, and solder balls 15 are welded on the bottom of the packaging substrate 11 . The packaging substrate 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More