Parameter-configurable FPGA-based Ethernet UDP/IP processor

A technology of Ethernet and processor, applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve the problems that affect the performance of the system, the MAC controller cannot be customized by the user, and increase the implementation cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

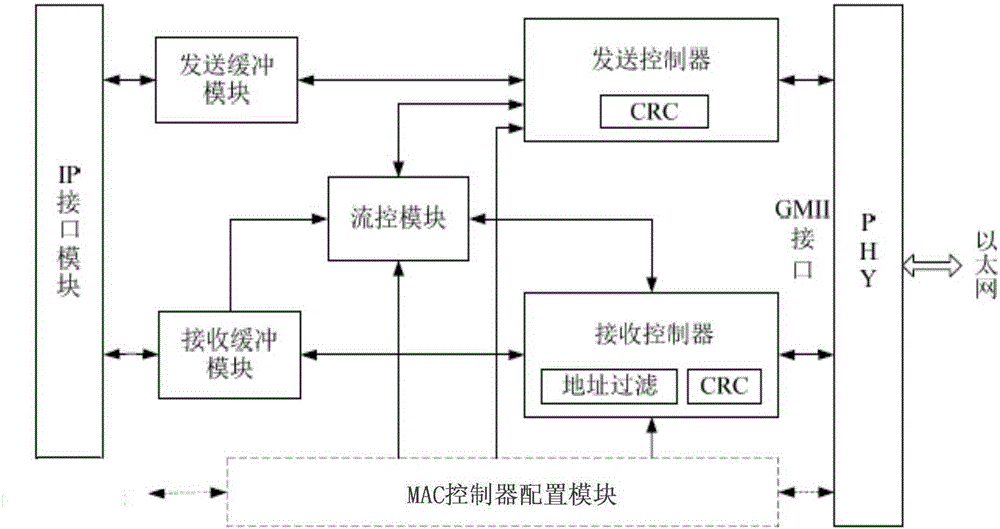

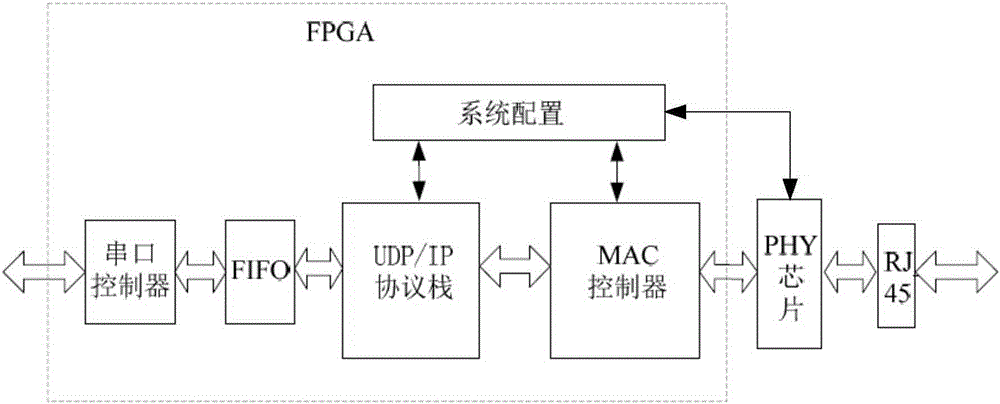

[0021] figure 1 It is an overall structural diagram of the FPGA-based Ethernet UDP / IP processor with configurable parameters of the present invention. like figure 1 As shown, the difference between the FPGA-based Ethernet UDP / IP processor with configurable parameters of the present invention and the common FPGA-based Ethernet UDP / IP processor is that a system configuration module is added.

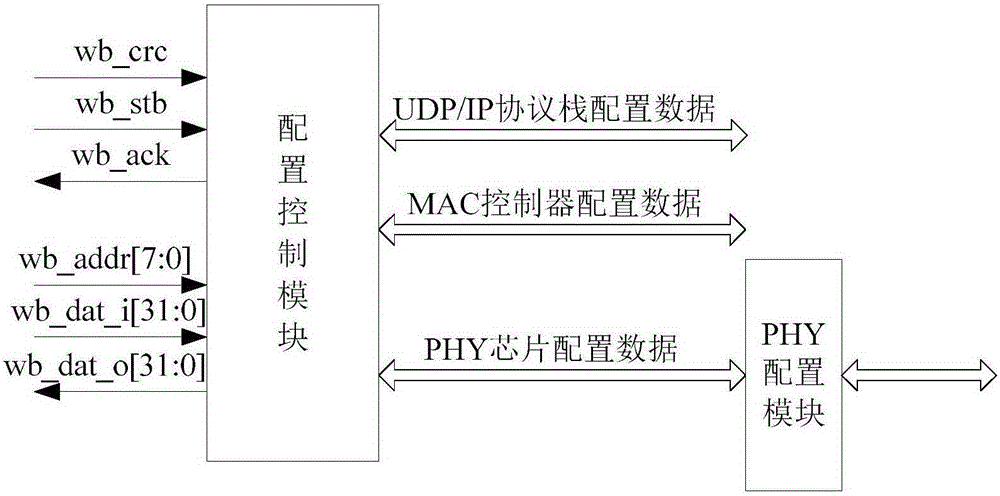

[0022] figure 2 Yes figure 1 A block diagram of the system configuration module in . like figure 2 As shown, the system configuration module includes a configuration control module and a PHY chip configuration module. In the configuration control module, parameter registers are respectively set for UDP / IP protocol stack configuration parameters or MAC control configuration parameters, and address registers and parameter registers are set for PHY (PhysicalLayer, physical layer) chip configuration parameters. When the configuration control module receives UDP / IP protocol stack config...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More