Method of controlling process plasma damages

A plasma and process technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, electrical components, etc., can solve plasma damage, change device electrical properties, and have no detection and control methods for plasma damage, etc. problem, achieve the effect of improving the process level and reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

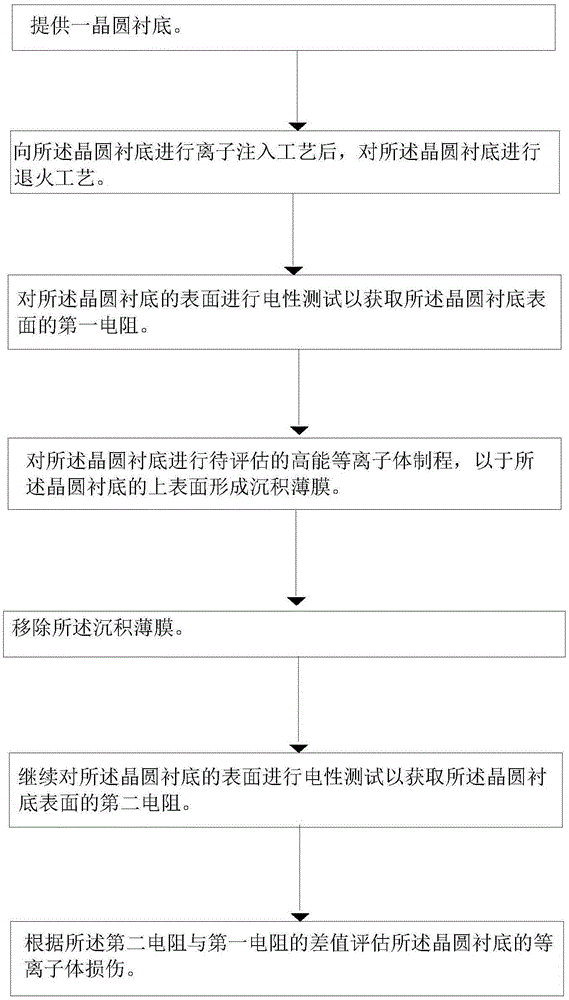

[0030] Such as figure 1 As shown, the present embodiment relates to a method for controlling process plasma damage, comprising the following steps:

[0031] Step 1, providing a wafer substrate 1, such as figure 2 As shown, in the embodiment of the present invention, the wafer substrate 1 is a blank wafer (blank wafer) without any device structure formed thereon.

[0032] In a preferred embodiment of the present invention, the wafer substrate 1 is a test wafer.

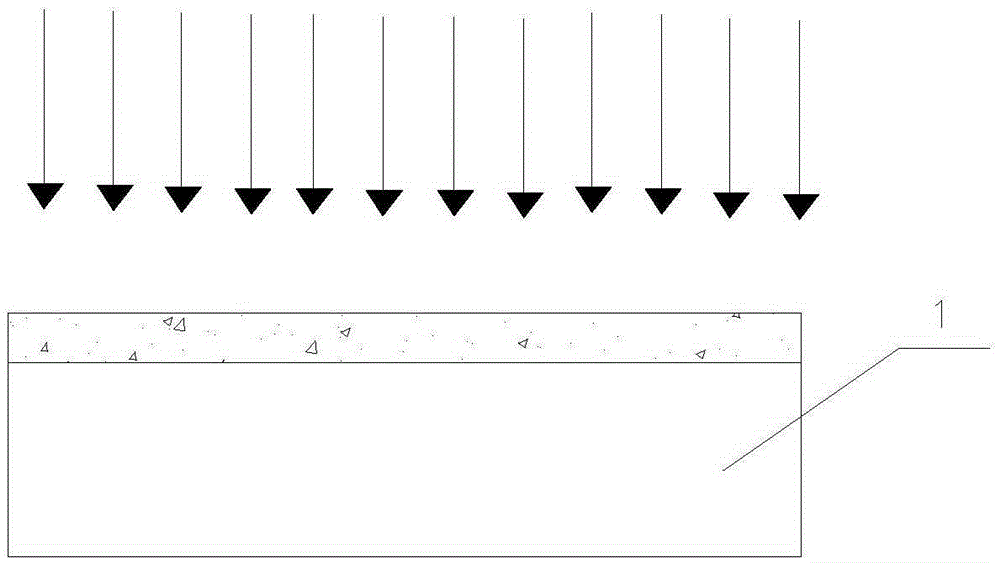

[0033] Step two, such as image 3 As shown, an ion implantation process is performed on the wafer substrate 1 , and an annealing process is performed on the ion-implanted wafer substrate 1 .

[0034] In a preferred embodiment of the present invention, the ions used in the ion implantation process are phosphorus (P) ions.

[0035] I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More