Method of forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve problems such as poor semiconductor structure performance, achieve the effect of reducing the number of ions and improving adjustment accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] After discovery and analysis, the reasons for the poor performance of the semiconductor structure formed by the method of the prior art are as follows:

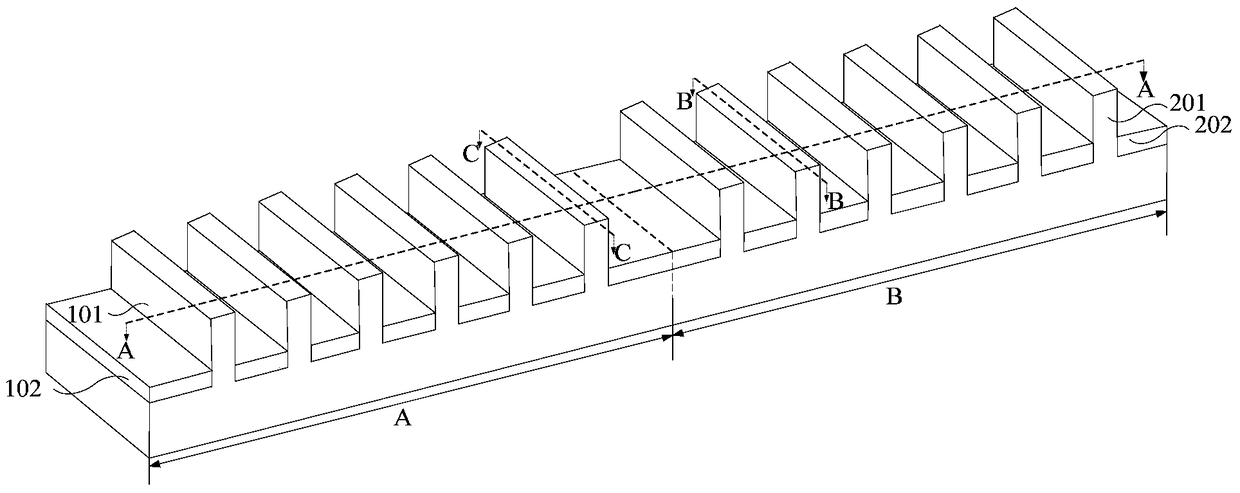

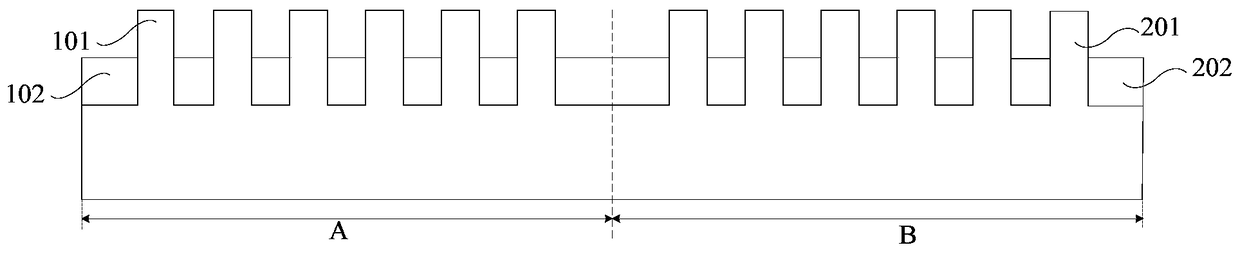

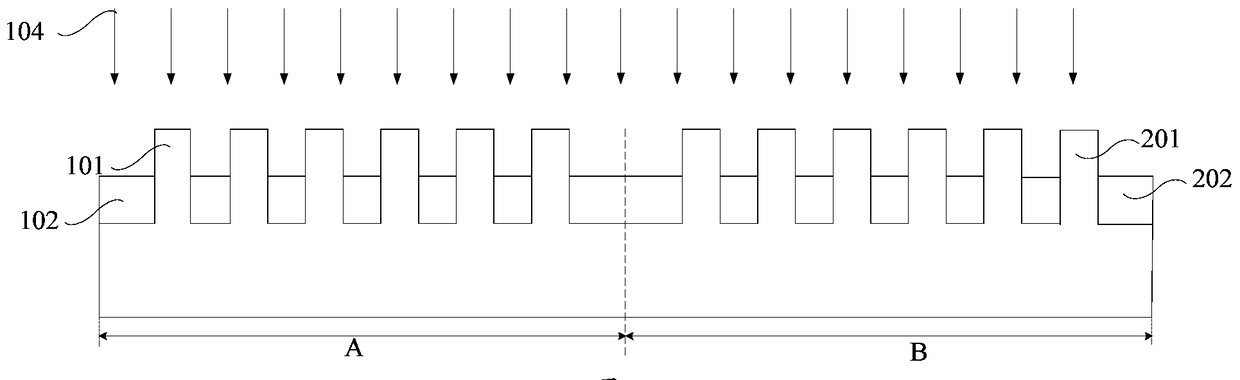

[0060] The device size (bulk width) of the FinFET is very small, especially, the top width (topwidth) of the fin and the bottom width (bottom width) of the fin. In prior art, refer to image 3 The ion implantation 104 of the semiconductor substrate in the peripheral region A, the fin portion 101 in the peripheral region and the semiconductor substrate in the core region B and the fin portion 201 in the core region is performed in one step. Ion implantation is first performed on the fin portion 201 of the core area to form a core area threshold voltage ion implantation layer. When the fin portion 201 of the core region is used to form an NMOS transistor, the implanted ions include phosphorus ions and arsenic ions. When the core region fin 201 is used to form a PMOS transistor, the implanted ions include boron ions. N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More