System and method for dispatching FPGA (Field Programmable Gate Array) accelerator based on Xen virtualized cluster

A scheduling system and scheduling method technology, applied in the field of scheduling systems, can solve problems such as high time complexity of algorithms, expensive hardware equipment, and shortened response time, so as to improve data transmission efficiency, solve low equipment utilization, and increase system throughput volume effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

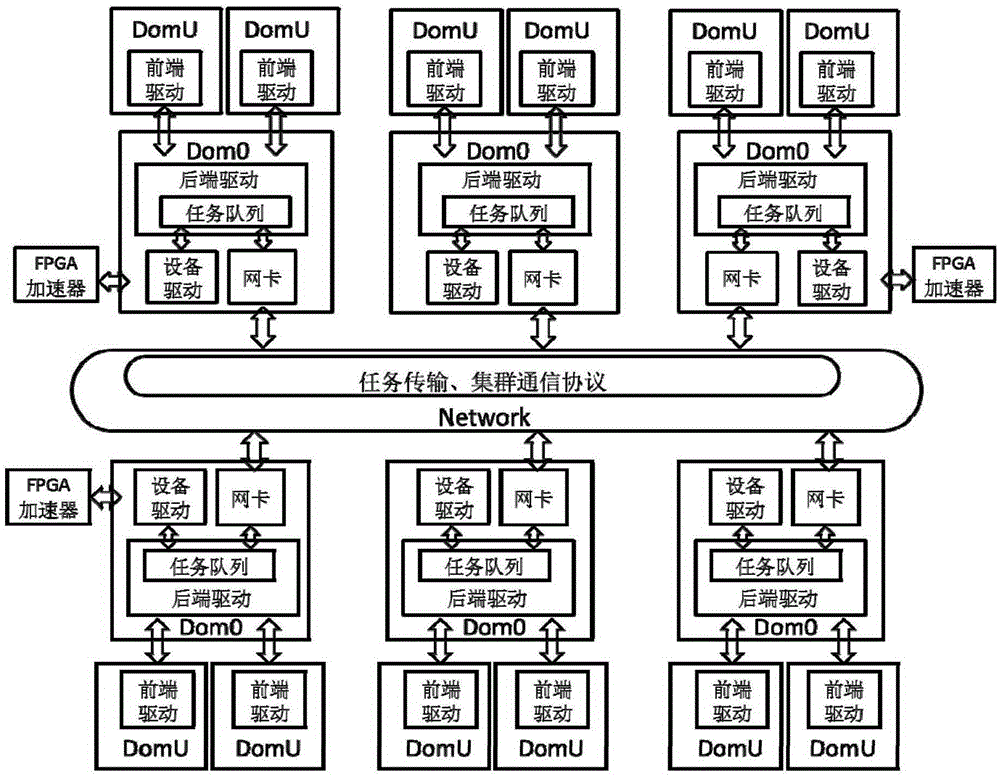

[0040] Realize the virtualized cluster scheduling system of FPGA accelerator, which mainly combines FPGA acceleration technology, I / O device virtualization technology and cluster scheduling technology to realize complete scheduling algorithm, so that all virtual machines in the cluster can share FPGA accelerator and balance servers Load, increase system throughput.

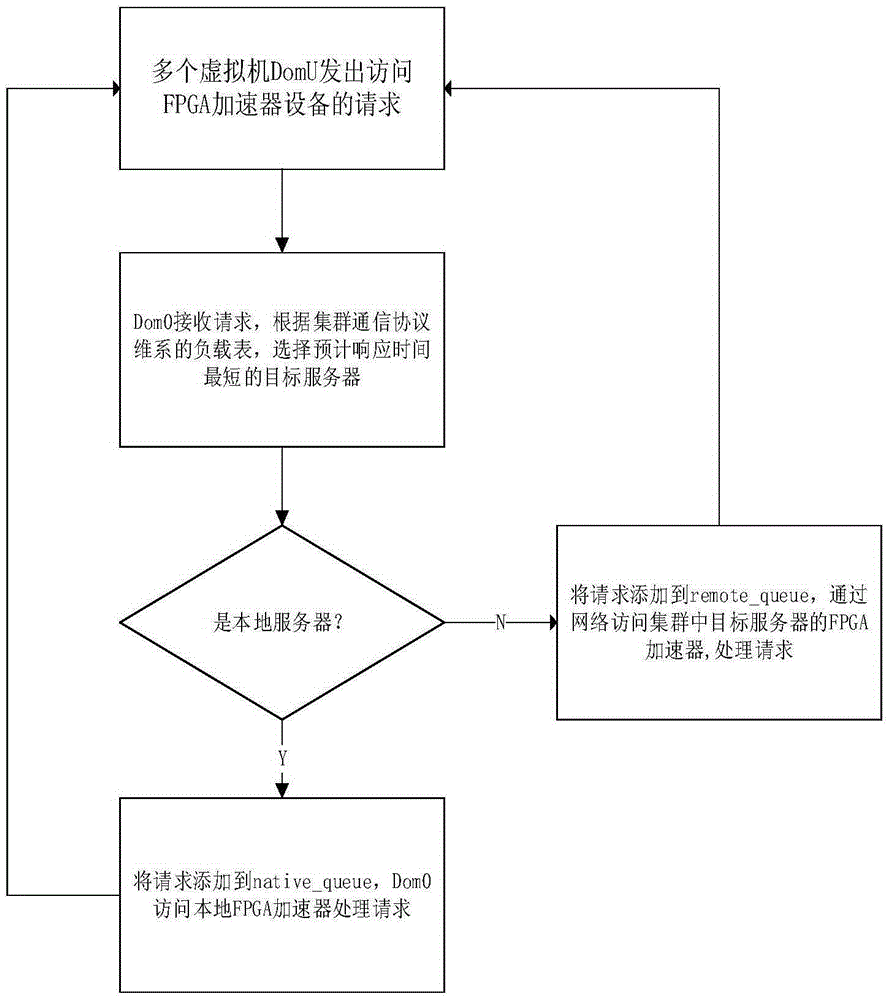

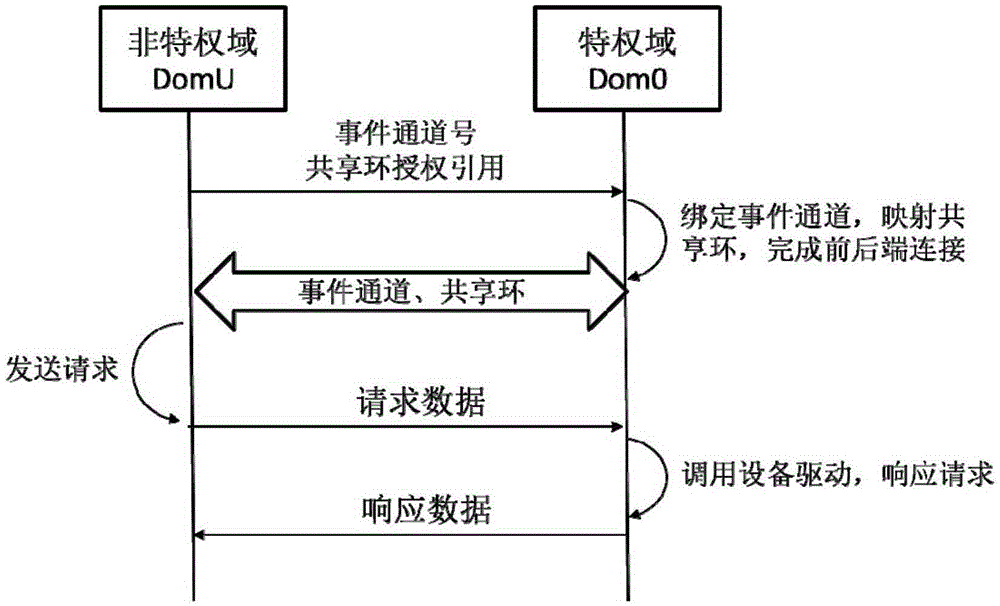

[0041] The overall framework is like figure 1 As shown, the software code with high computational complexity is replaced with FPGA, and the acceleration function is implemented on the FPGA; the FPGA is virtualized using Xen technology; different servers use the cluster scheduling method to balance the load and access the FPGA on the server with a small load. Using the Xen separation device driver model, create a front-end driver in the non-privileged domain virtual machine DomU, and create a back-end driver in the privileged domain virtual machine Dom0. The overall process is as figure 2 As shown, the DomU front-end...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com