Semiconductor structure and method of fabricating the same

A semiconductor and manufacturing technology, applied in the field of semiconductor structures and their manufacturing methods, can solve the problems of reducing product yield, alignment deviation, uneven height of copper bumps, etc., and achieve the effect of avoiding alignment deviation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

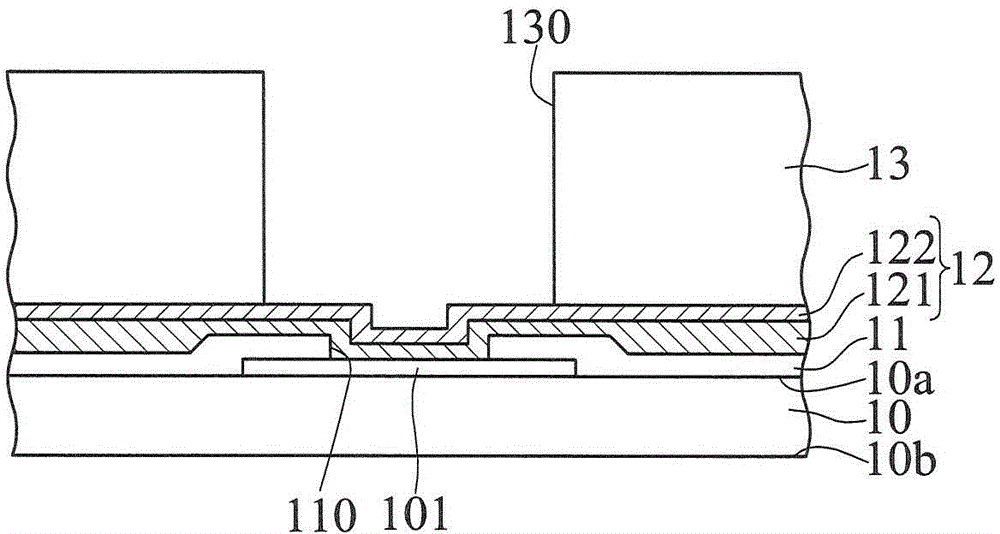

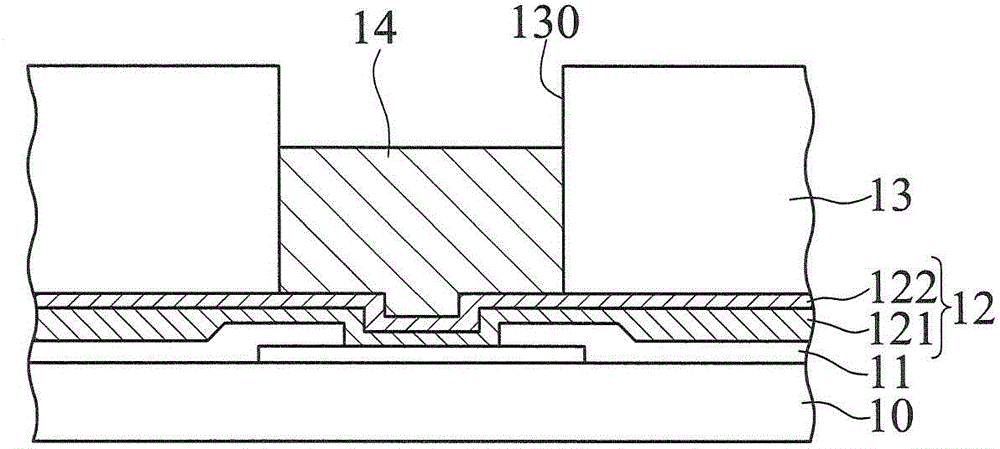

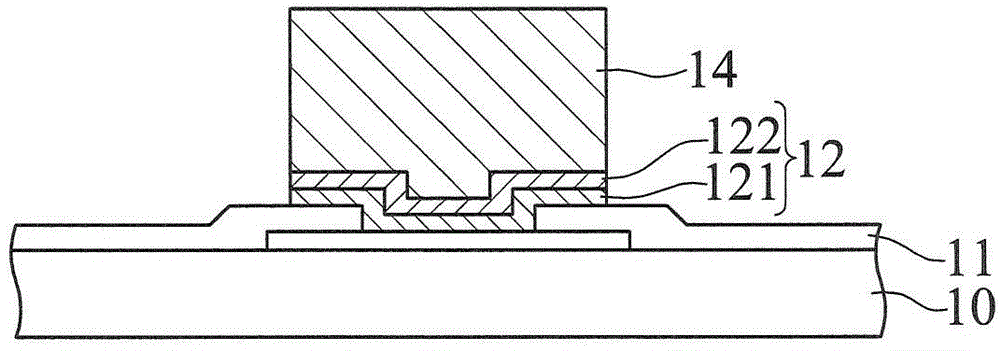

[0050] Figure 2A to Figure 2I What is shown is a cross-sectional view of the first embodiment of the manufacturing method of the semiconductor structure of the present invention.

[0051] like Figure 2A As shown, a semiconductor wafer 20 with opposite active surface 20a and non-active surface 20b is provided, and there are a plurality of electrode pads 201 on the active surface 20a, and a plurality of passivation layer openings are formed on the electrode pads 201 and the active surface 20a. The passivation layer 21 of the hole 210, each of the passivation layer openings 210 correspondingly exposes each of the electrode pads 201, and a dielectric layer 22 with a plurality of openings 220 is formed on the passivation layer 21, so that each of the openings 220 Corresponding to the exposed electrode pads 201 , the dielectric layer 22 can be a photosensitive insulating layer or a photoresist.

[0052] like Figure 2B As shown, a titanium layer 231 and a copper layer 232 as an...

no. 2 example

[0062] Figure 3A to Figure 3D What is shown is a cross-sectional view of the second embodiment of the manufacturing method of the semiconductor structure of the present invention.

[0063] This embodiment is substantially the same as the previous embodiment, and the main difference is that the thickness of the plurality of semiconductor wafers 20 or the thickness of the adhesive layer 25 on the non-active surface 20b of the present embodiment is not the same as that of the previous embodiment. Similarly, the semiconductor wafer 20 and the metal post 24' are located at different heights, but the implementation of the present invention is not affected by this.

[0064] The present invention provides a semiconductor structure, comprising: a carrier plate 26; a semiconductor chip 20, which is arranged on the carrier plate 26, and has a non-active surface 20b connected to the carrier plate 26 and an active surface 20a opposite to the non-active surface 20b A plurality of metal pi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More