Overlapping capacitor and manufacturing method thereof

A technology of superimposing capacitors and manufacturing methods, which is applied in the direction of circuits, electrical components, and electrical solid devices, can solve the problems of large process development costs for dielectric materials, and achieve the effects of saving development costs and large unit capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

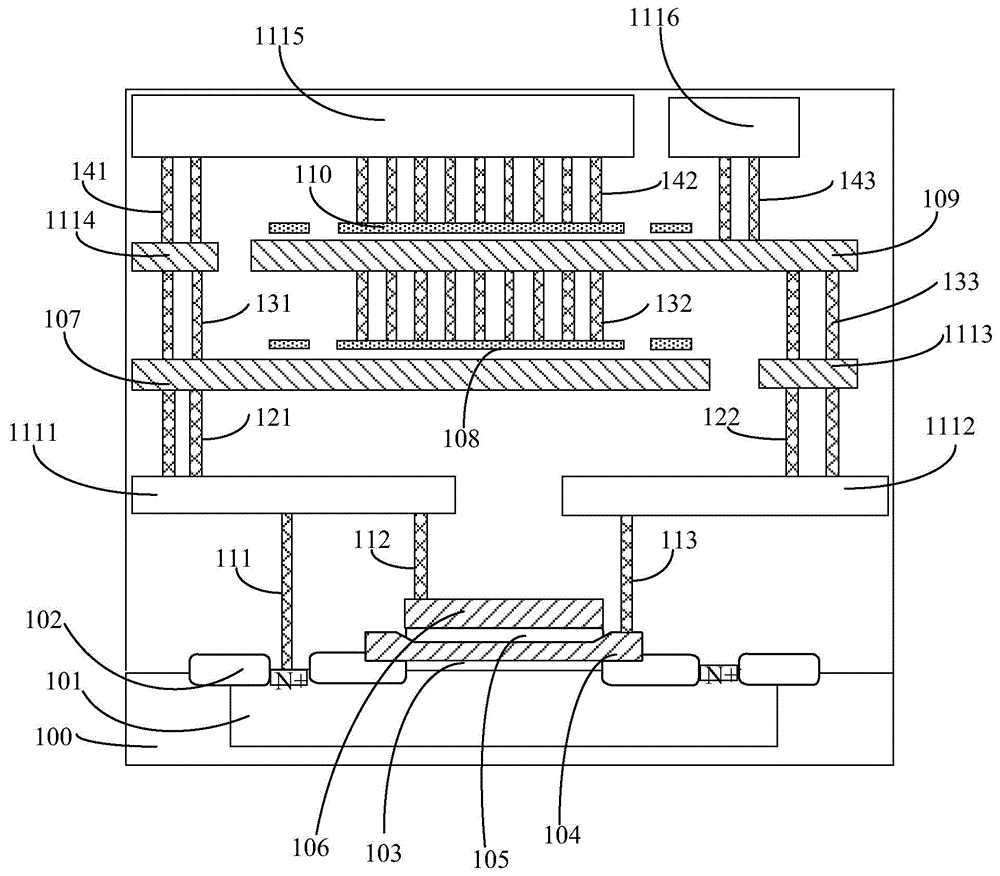

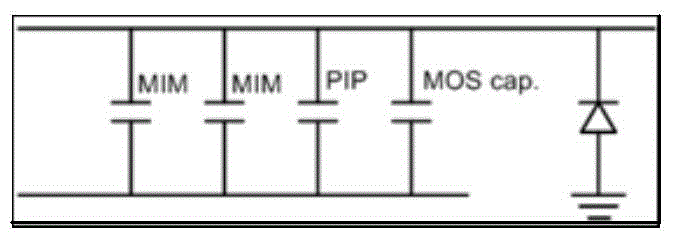

[0044] The present invention relates to a stack capacitor, which includes a MOS capacitor, a PIP capacitor and at least one MIM capacitor. figure 1 The structure of the superposition capacitor according to the embodiment of the present invention is shown.

[0045] refer to figure 1 , taking the superposition of a MOS capacitor, a PIP capacitor and two MIM capacitors as an example, the superposition capacitor structure of the present invention will be described. The superposition capacitor in the embodiment of the present invention includes a MOS capacitor, and the MOS capacitor includes: a semiconductor substrate 100, and the semiconductor substrate 100 may be silicon or silicon-on-insulator (SOI). The semiconductor substrate in the embodiment of the present invention is preferably a silicon substrate. An isolation structure 102 is formed in the semiconductor substrate 100, and the isolation structure 102 serves as device isolation and defines a device region. Optionally, the...

Embodiment 2

[0057] refer to Figure 5 , to describe in detail the fabrication method of the superimposed capacitor in Embodiment 2 of the present invention.

[0058] Embodiment 2 of the present invention provides a method for manufacturing a superimposed capacitor in Embodiment 1, including:

[0059] First, step 501 is performed to provide a semiconductor substrate on which a MOS capacitor is fabricated. Specifically include the following steps:

[0060] Step 1: performing ion implantation on the semiconductor substrate to form a well region, and the well region is used as a lower plate of a MOS capacitor. Optionally, the well region is an N-type well region or a P-type well region. If the N-type well region is pre-formed, the implanted ions need to be N-type dopant ions, such as phosphorus; if the P-type well region is pre-formed, the implanted ions need to be P-type dopant ions, such as boron or boron fluoride.

[0061] Step 2, forming an isolation structure in the semiconductor sub...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More