Test circuit used for measuring SRAM array capacitor and method for measuring SRAM array capacitance

A technology for testing circuits and arrays, applied in static memory, instruments, etc., can solve problems such as large errors, low accuracy, and trouble, and achieve the effects of simple structure, easy implementation, and high measurement accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

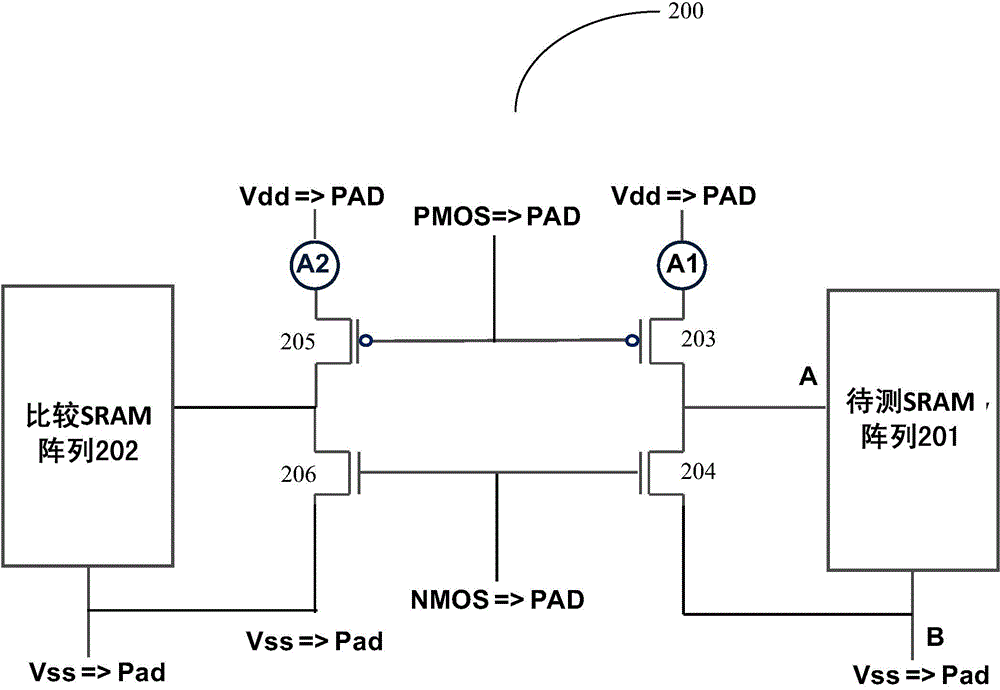

[0029] In one aspect, the present invention provides a test circuit for measuring the capacitance of an SRAM array. figure 2 A structural diagram of a test circuit 200 for measuring the capacitance of an SRAM array according to an embodiment of the present invention is shown. Such as figure 2 As shown, the test circuit 200 for measuring the capacitance of the SRAM array includes a SRAM array 201 to be tested, a comparison SRAM array 202 for comparing with the SRAM array 201 to be tested, a first PMOS transistor 203 corresponding to the SRAM array to be tested and The first NMOS transistor 204 , and the second PMOS transistor 205 and the second NMOS transistor 206 corresponding to the comparative SRAM array 202 .

[0030] Wherein, the drain of the first PMOS transistor 203 is connected to the first power supply, and the drain of the second PMOS transistor 205 is connected to the second power supply;

[0031] The source of the first NMOS transistor 204 is connected to the th...

Embodiment 2

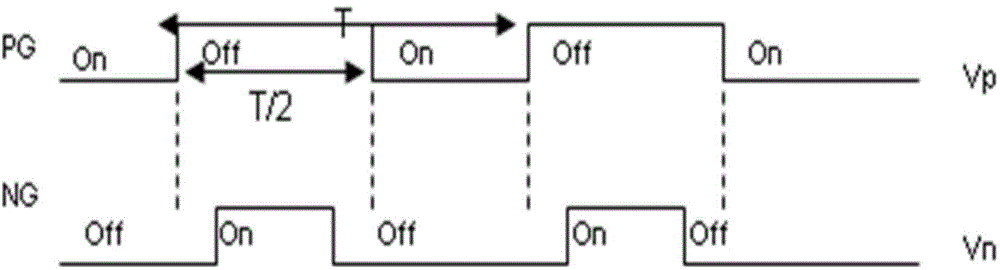

[0048] In another aspect, the present invention provides a method for measuring the capacitance of an SRAM array using the above test circuit. The method includes: when the test circuit is working, applying pulses to the first PMOS transistor, the first NMOS transistor, the second PMOS transistor and the second NMOS transistor to turn them on or off; The first current of the drain of the tube and the second current through the drain of the second PMOS tube; and based on the first current and the second current, the frequency of the pulse and the voltage of the first power supply and the second power supply that make the test circuit work Calculate the capacitance of the SRAM array under test. Exemplarily, the frequency of the pulses applied to the PMOS transistor and the NMOS transistor is X, the measured first current is IA1, the second current is IA2, and the voltages of the first power supply and the second power supply that make the test circuit work Both are Vdd, then th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com