SSD controller based on read-write cache separation of STT-MRAM

A controller and cache technology, applied in the direction of static memory, memory system, digital memory information, etc., can solve the problems of insufficient data protection, increase system reliability, etc., and achieve the effect of simplifying system design complexity and increasing system reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

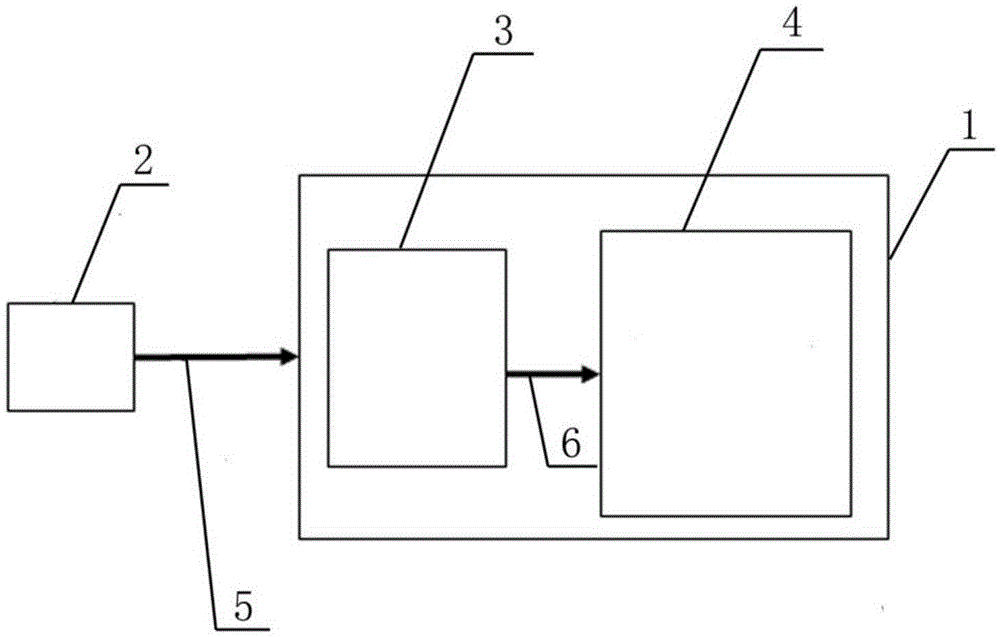

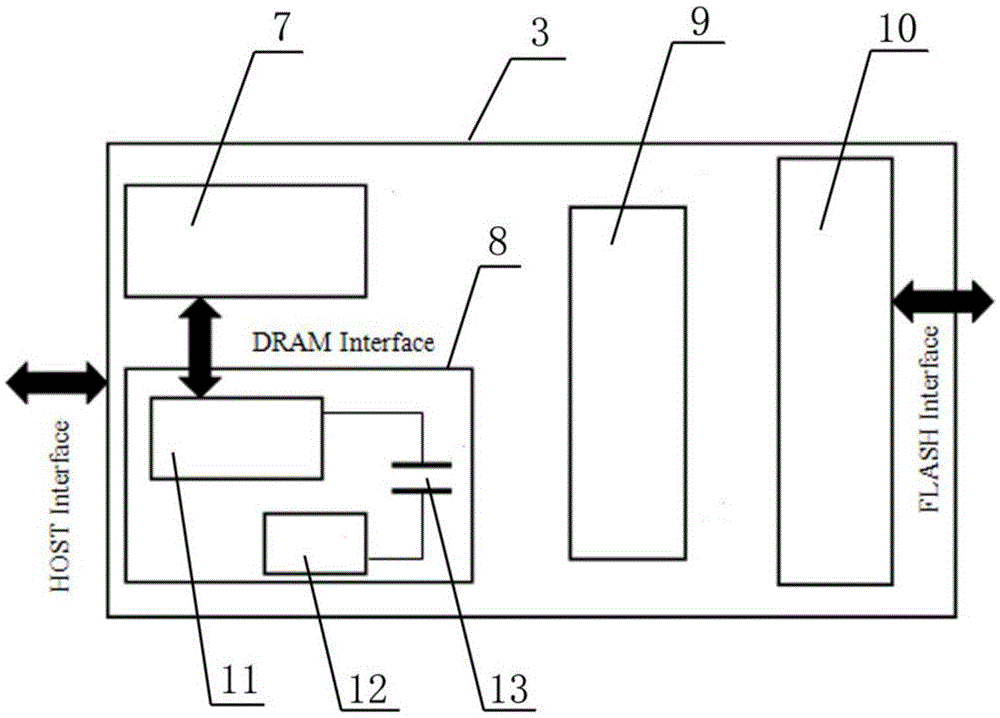

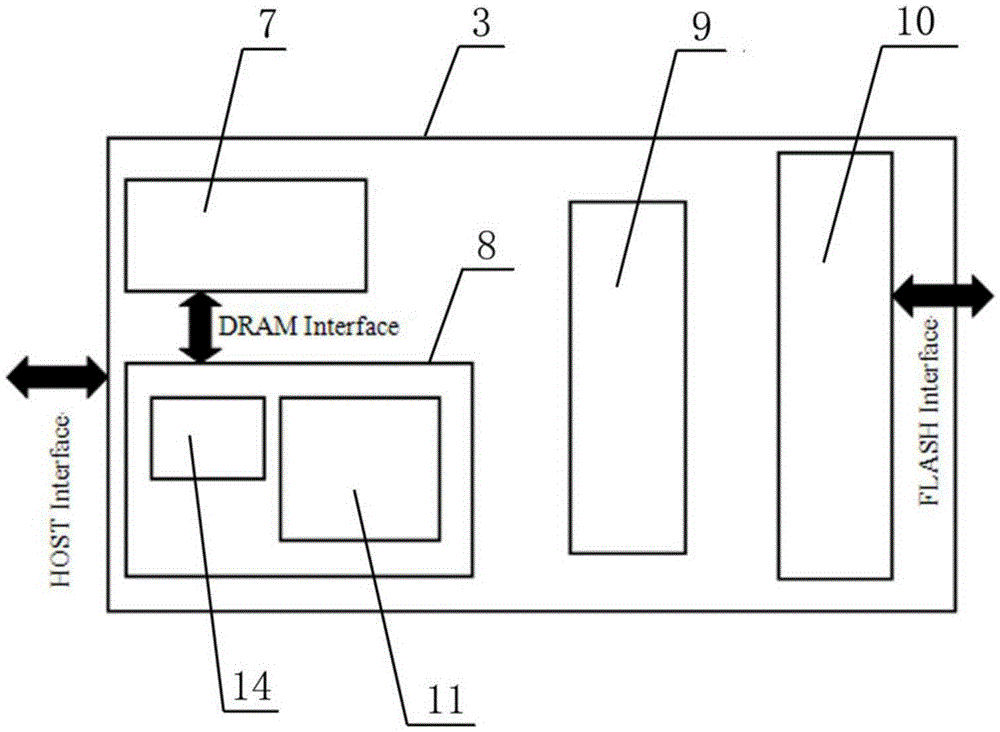

[0018] Embodiment 1: as image 3 As shown, the SSD controller 3 is responsible for controlling data transmission between the FLASH storage array 4 and the host processor 2 . The read-write cache module 8 is responsible for caching all the data that needs to be written into the FLASH storage array 4, all the data that needs to be read from the FLASH storage array 4, the logical address (LBA) mapping table, the LBA modification increment table, the storage controller program and User configuration and other information, wherein the STT-MRAM memory 14 is responsible for caching all data that needs to be written into the FLASH storage array 4 and the LBA modification increment table; the DRAM memory 11 is responsible for caching all data that needs to be read from the FLASH storage array 4, LBA mapping table, controller program and user configuration. The communication interface between the read-write cache module 8 and the control logic module 7 is a DRAM interface, which can be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More