An asic design clock network extraction system

A clock network and extraction system technology, which is applied in computing, instruments, electrical digital data processing, etc., to reduce error rates and improve work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

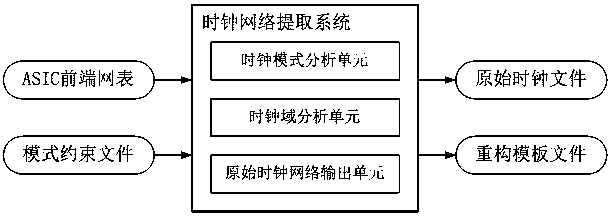

[0017] attached figure 1 A schematic structural representation of the ASIC design clock network extraction system described in this embodiment; as attached figure 1 As shown, the central box area in the figure is the system of the present invention, the left side of the system is the input file, and the right side is the output file. It can be seen from the figure that the system consists of three parts: clock mode analysis unit, clock domain analysis unit, and original clock network output unit. The input files on the left include ASIC front-end netlist and mode constraint files; the output files on the right include original clock files and reconstruction template files.

[0018] The ASIC design clock network extraction system described in this embodiment, the clock mode analysis unit generates various parameters of the ASIC design for clock network analysis in different operating modes according to the input mode constraint file, and transmits them to the clock domain anal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com