A double gate array substrate and display device

An array substrate and double gate technology, which is applied to instruments, semiconductor devices, optics, etc., can solve the problem of low transmittance of the double gate array substrate, and achieve the effects of increasing transmittance, increasing rotation, and increasing aperture ratio.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

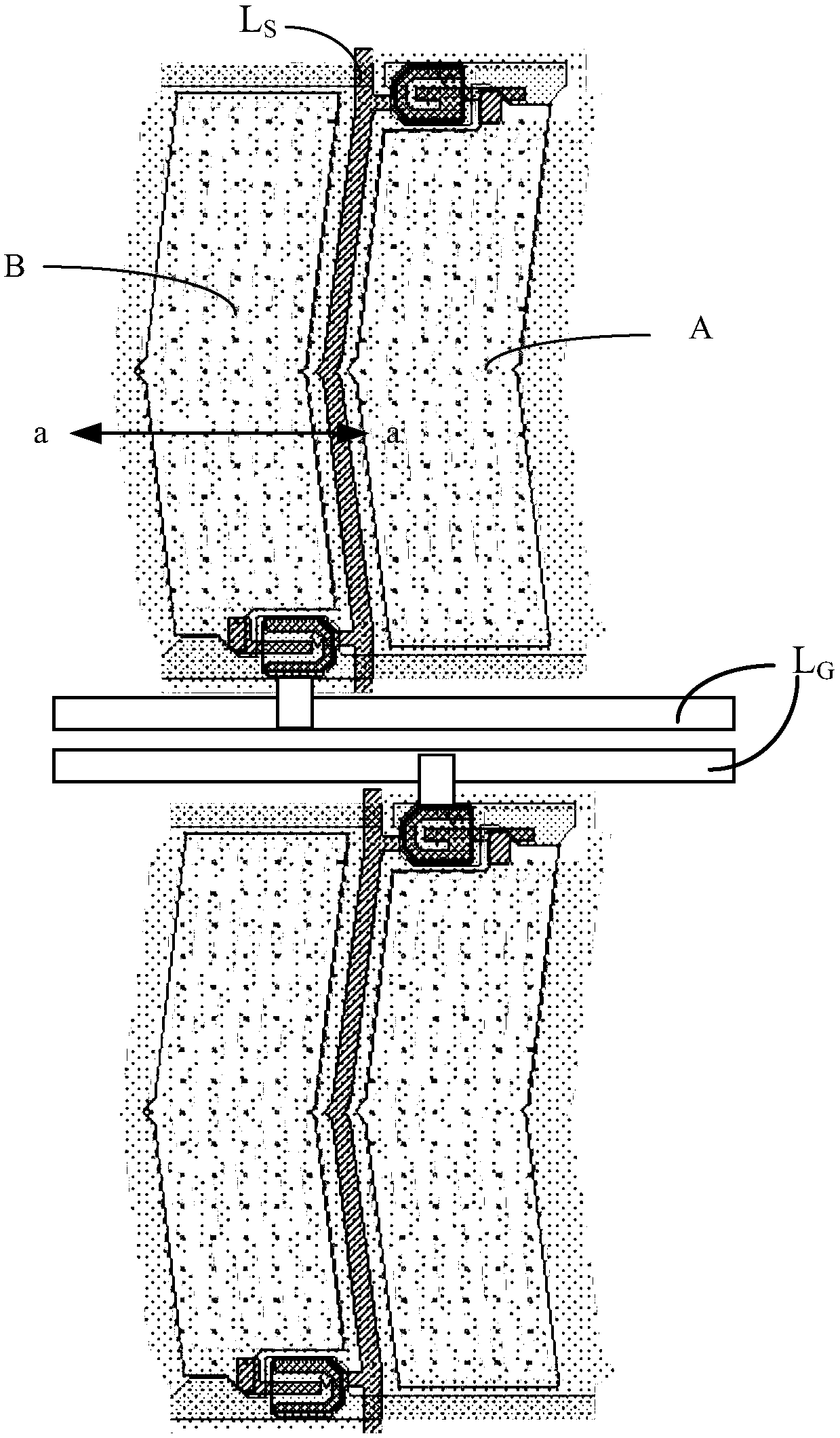

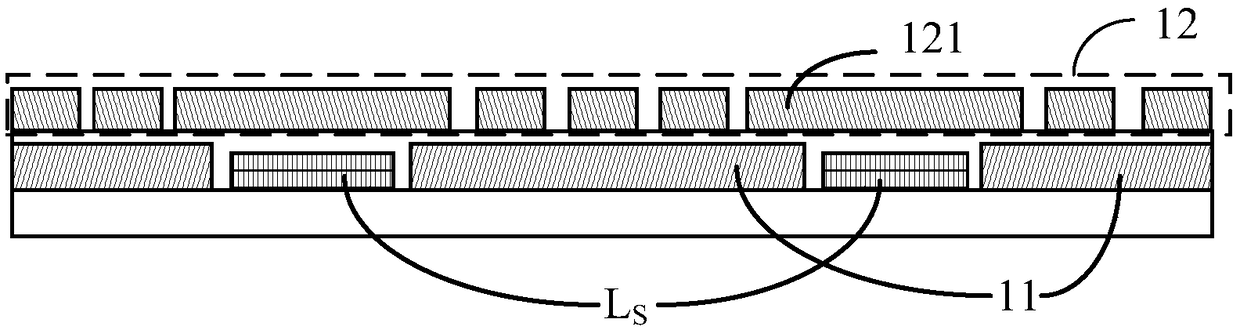

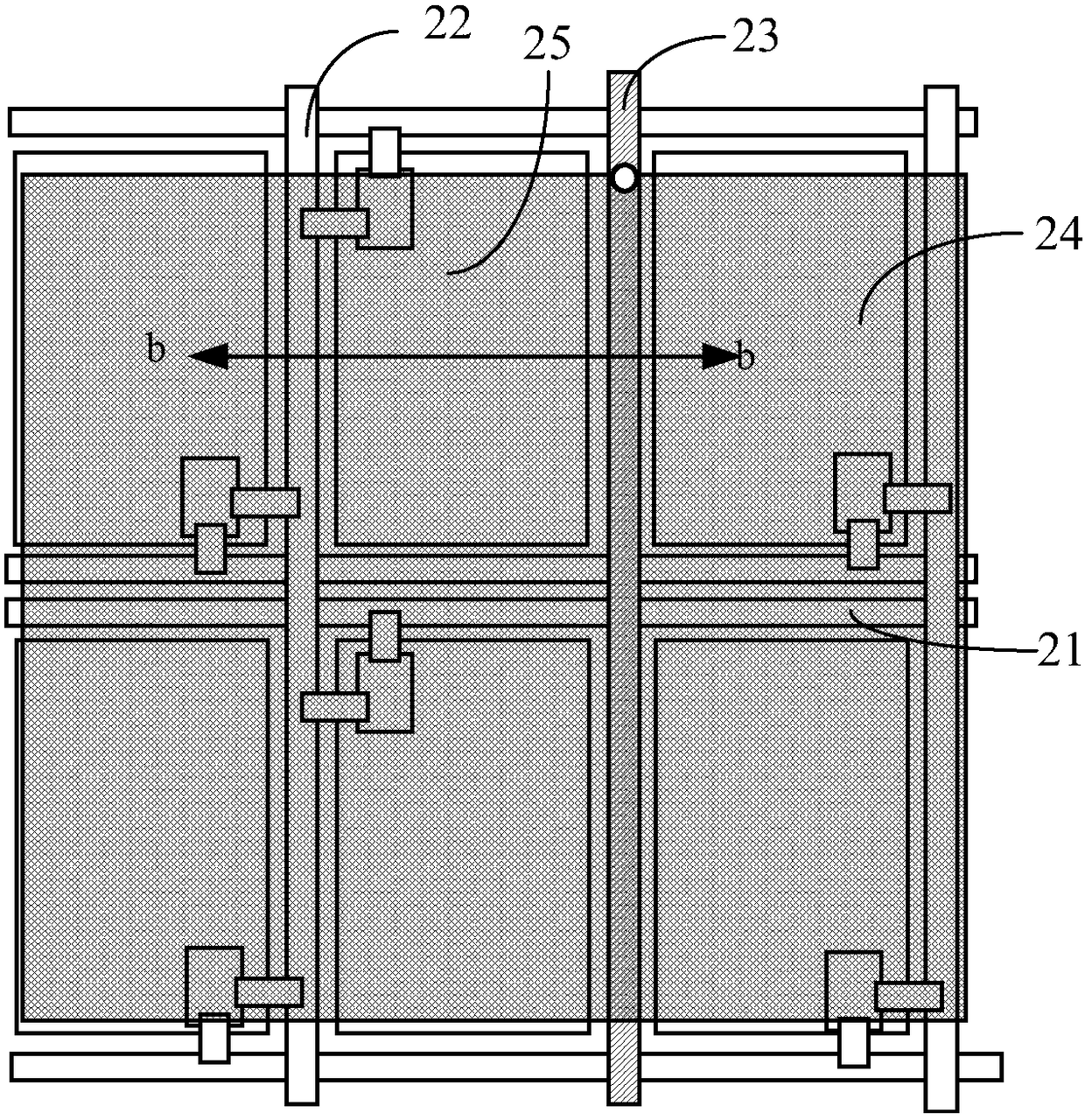

[0046] As shown in FIG. 4(a), it is a schematic structural diagram of the array substrate in the FFS display mode in Example 1, wherein, any adjacent two dry electrodes 411 in the common electrode 41 and the space between the two dry electrodes 411 The common electrode pattern formed by the branch electrodes 412 corresponds to a pixel unit P; combined with the cross-sectional structure diagram of FIG. The orthographic projections of the adjacent pixel electrodes 42 on the double gate array substrate have overlapping areas (the dotted elliptical frame in the figure) and at least cover the main signal line 43, and the other dry electrode 411 adjacent to one of the dry electrodes 411 has an overlapping area. The orthographic projection of the electrode 411 (the dry electrode on the right in the figure) on the double gate array substrate is located in the gap between adjacent pixel electrodes 42 and covers the secondary signal line 44 . In addition, the double gate array substrate...

example 2

[0049] As shown in Figure 5 (a), it is a schematic structural diagram of the array substrate of the AFFS display mode in Example 2, wherein the dry electrode 511 of the common electrode 51 is arranged along the extending direction of the main signal line 53, and the branch electrodes 512 are arranged along the main signal line 53. Lines 53 are set in the direction where they intersect, and the common electrode pattern formed by any two adjacent dry electrodes 511 and the branch electrodes 512 between the two dry electrodes 511 corresponds to two adjacent pixel units Q; in combination with FIG. 5(b ), and the cross-sectional view at the cross-section B-B shown in FIG. The orthographic projection on the gate array substrate has an overlapping area and at least covers the main signal line 53 , and the branch electrodes 512 have a continuous pattern at the junction between adjacent pixel units Q. Based on the above scheme, after the sub-signal line 54 is connected to the common el...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More