Fault location method and server

A fault location and server technology, applied in the computer field, can solve problems such as inability to quickly locate faults, system hangs, and difficulty in obtaining MCA.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

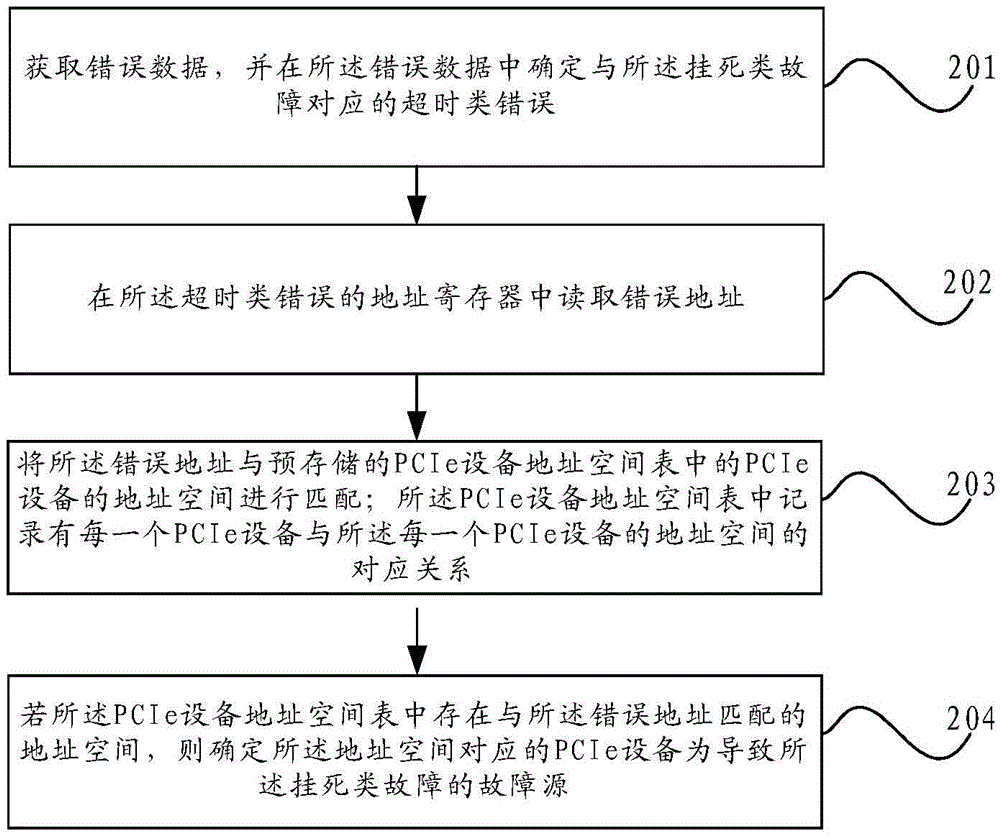

[0062] An embodiment of the present invention provides a fault location method, such as figure 2 As shown, the method includes the following steps:

[0063] 201. Acquire error data, and determine a timeout error corresponding to the hang-up error in the error data.

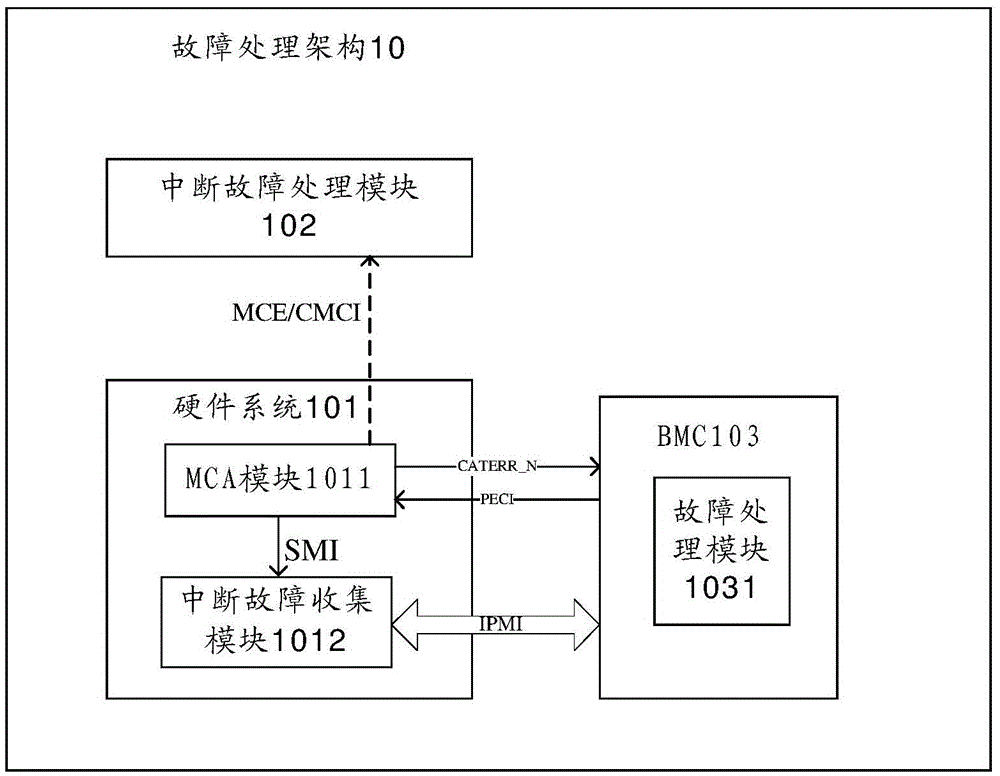

[0064] Wherein, the hanging failure is 3-Strike. The error data is used to record errors generated when the server fails, and the timeout error is an error generated when the server fails. The execution subject of the fault location method in this embodiment may be the BMC in the processor of the server where the 3-Strike fault occurs, namely figure 1 The BMC module 103 is shown.

[0065] Of course, the server will first detect the failure notification message. The fault notification message indicates that a hang-up fault has occurred, which may be a CATERR_N signal. For example, when the hang-up failure occurs, the MCA module of the server will send a CATERR_N signal to the BMC (that is, the pin communicati...

Embodiment 2

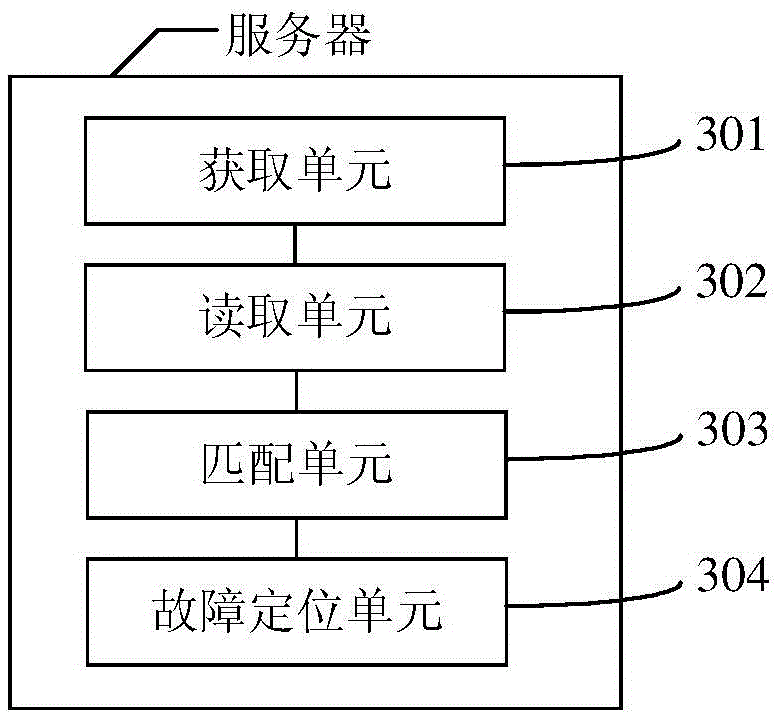

[0154] The embodiment of the present invention provides a server 30, such as image 3 As shown, the server 30 includes: an acquiring unit 301 , a reading unit 302 , a matching unit 303 and a fault location unit 304 .

[0155] The obtaining unit 301 is configured to obtain error data, and determine a timeout type error corresponding to the hanging type fault in the error data. The error data is used to record errors generated when the server fails, and the timeout error is an error generated when the server fails.

[0156] The reading unit 302 is configured to read the error address in the address register of the timeout error determined by the acquisition unit.

[0157] The matching unit 303 matches the error address with the pre-stored bus and interface standard PCIe device address space table; the address space of each PCIe device and each PCIe device is recorded in the PCIe device address space table corresponding relationship.

[0158] The fault locating unit 304 is con...

Embodiment 3

[0173] The embodiment of the present invention provides a server 40, such as Figure 4 As shown, the server 40 includes: a processor 401 , a system bus 402 and a memory 403 .

[0174] Wherein, the processor 401 may be a central processing unit (English: central processing unit, abbreviation: CPU).

[0175] The memory 403 is used to store program codes, and transmit the program codes to the processor 401, and the processor 401 executes the following instructions according to the program codes. The memory 403 may include a volatile memory (English: volatile memory), such as a random access memory (English: random-access memory, abbreviated: RAM); the memory 403 may also include a non-volatile memory (English: non-volatile memory), such as Read-only memory (English: read-only memory, abbreviation: ROM), flash memory (English: flashmemory), hard disk (English: harddiskdrive, abbreviation: HDD) or solid-state drive (English: solid-state drive, abbreviation: SSD). The memory 403 m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More