How transistors are made

A manufacturing method and transistor technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as low yield and transistor failure, and achieve the effect of reducing thickness, reducing losses, and avoiding excessive losses.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] It is known from the background art that the transistors formed in the prior art are prone to failure and low yield.

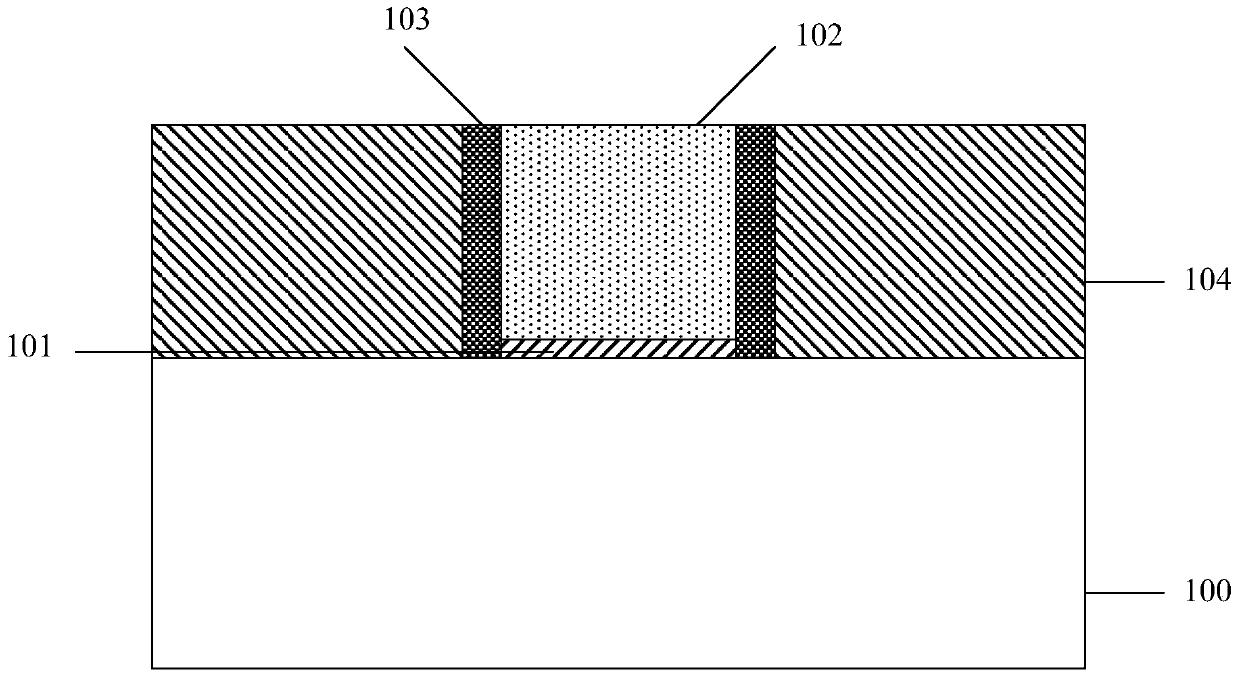

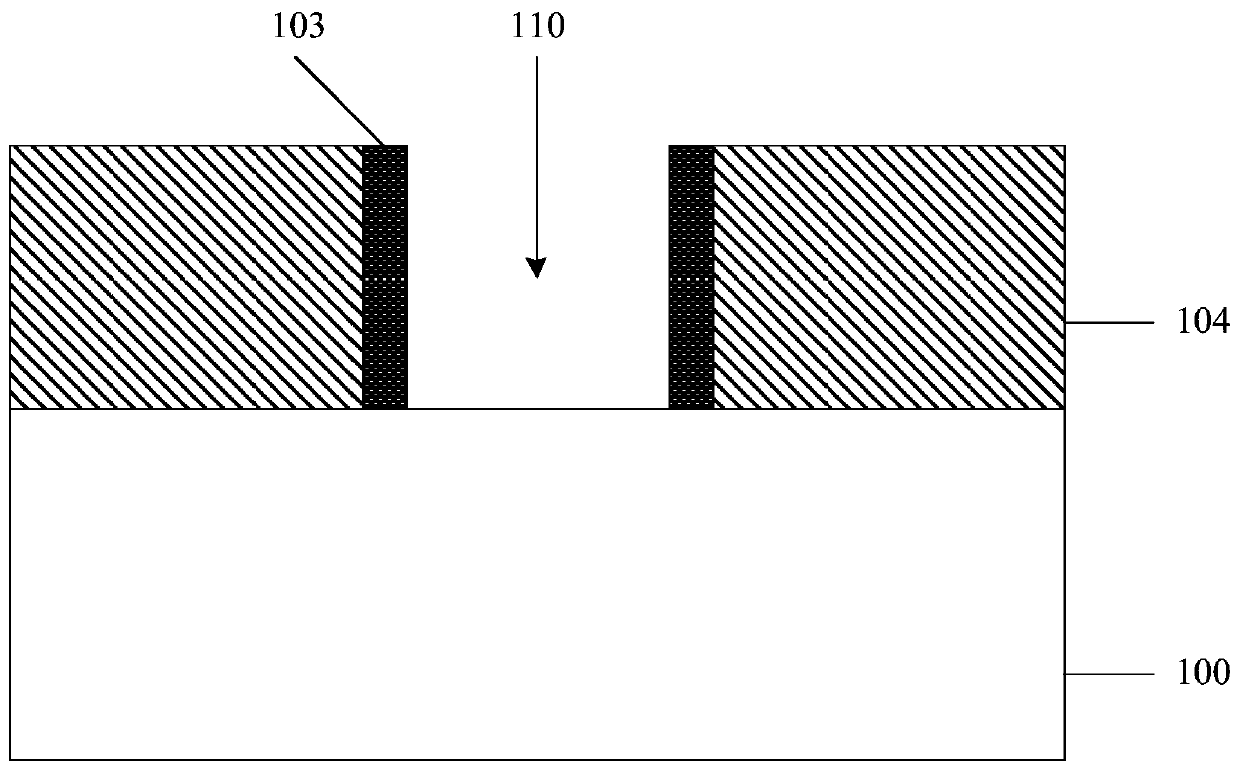

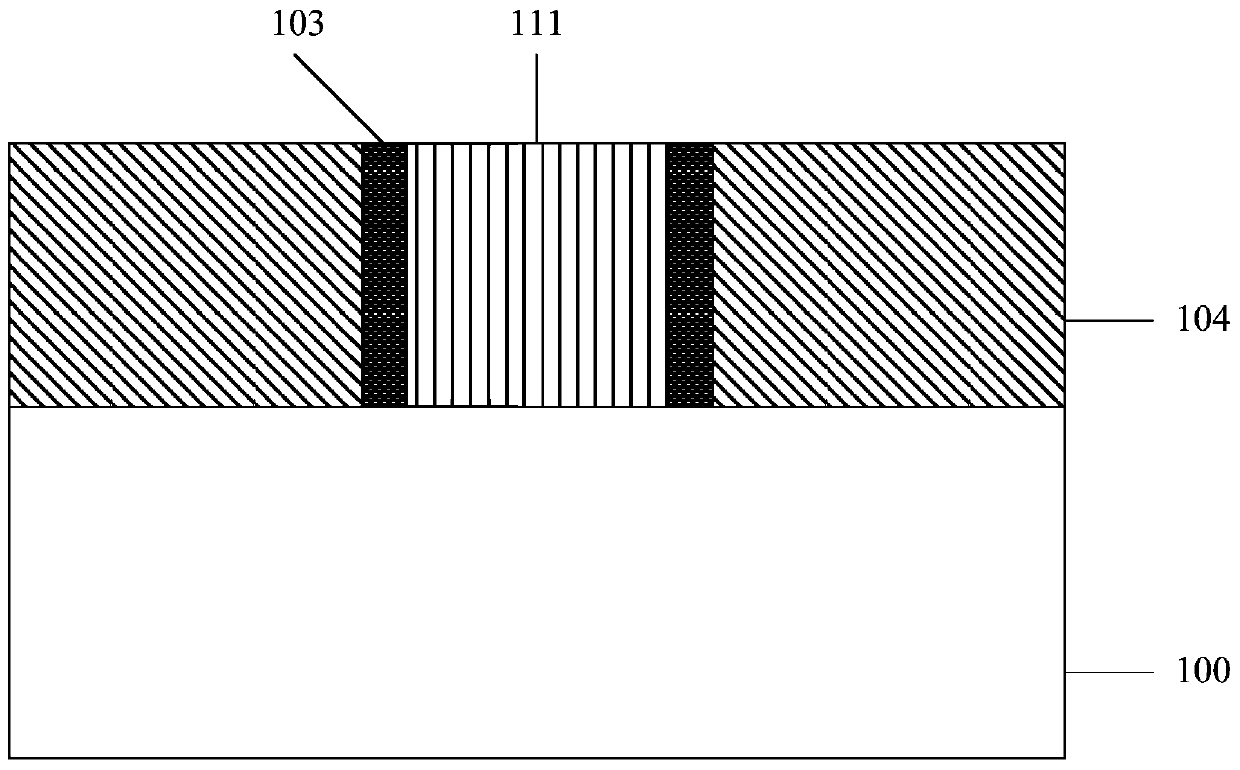

[0038] combine Figure 1 to Figure 3 The schematic diagram of the manufacturing method of the transistor in the prior art is shown, and the reasons for the failure of the transistor and the low yield are analyzed:

[0039] refer to figure 1 The material of the transistor protection layer 101 and the material of the interlayer dielectric layer 104 are oxides, and when the protection layer 101 is removed by cleaning with a diluted hydrofluoric acid solution, a part of the thickness of the interlayer dielectric layer 104 will also be consumed. Moreover, since the formation process of the protective layer 101 and the interlayer dielectric layer 104 is different (the method for forming the protective layer 101 is mostly a thermal oxidation process, and the method for forming the interlayer dielectric layer 104 is mostly a chemical vapor deposition process),...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More