Memory system and programming, erasing and reading method

A storage system and memory technology, applied in the field of memory, can solve the problems of multiple time, energy consumption, and consumption, and achieve the effect of reducing the chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the above-mentioned objects, features and advantages of the present invention more obvious and understandable, the specific embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

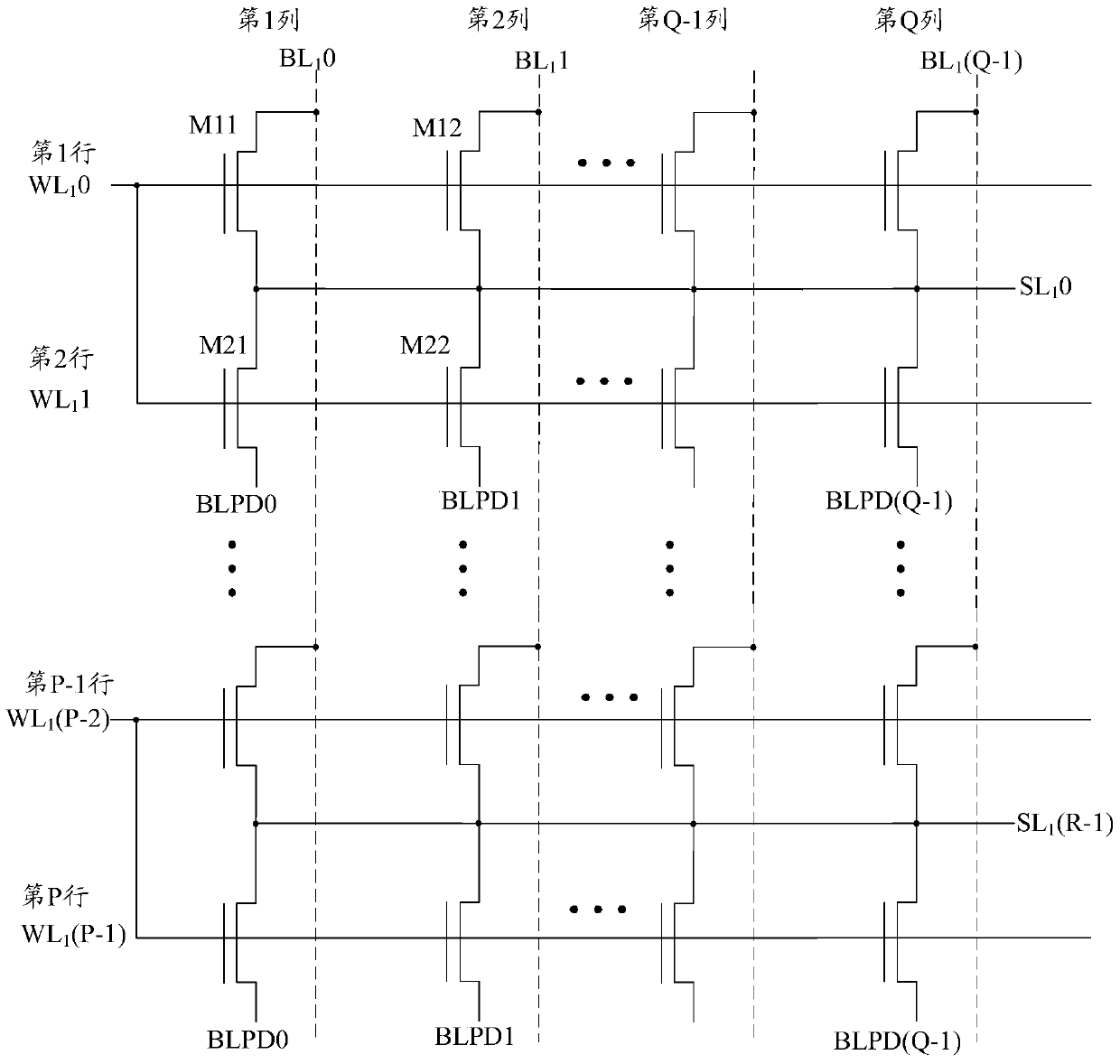

[0034] Such as figure 1 As shown, the first memory provided by the embodiment of the present invention includes: first memory cells arranged in P rows and Q columns, and P first word lines WL 1 (0, P-1), Q first bit lines BL 1 (0, Q-1), Q second bit lines BLPD (0, Q-1), and R first source lines SL 1 (0, R-1), P≥1, Q≥1, R≥1.

[0035] The first memory cell located in the p-th row and the q-th column is connected to the q-th first bit line BL 1 , P≥p≥1, Q≥q≥1, and the first memory cell located in the p+1th row and the qth column is connected to the qth second bit line BLPD.

[0036] The P rows of first memory cells and the P first word lines WL 1 One-to-one correspondence connection, the sth first word line and the s+1th first...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More