Shallow junction shield groove technique for protecting active region area

A technology for isolating trenches and active regions, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of reducing the effective area of active regions, affecting the high density and critical dimensions of devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

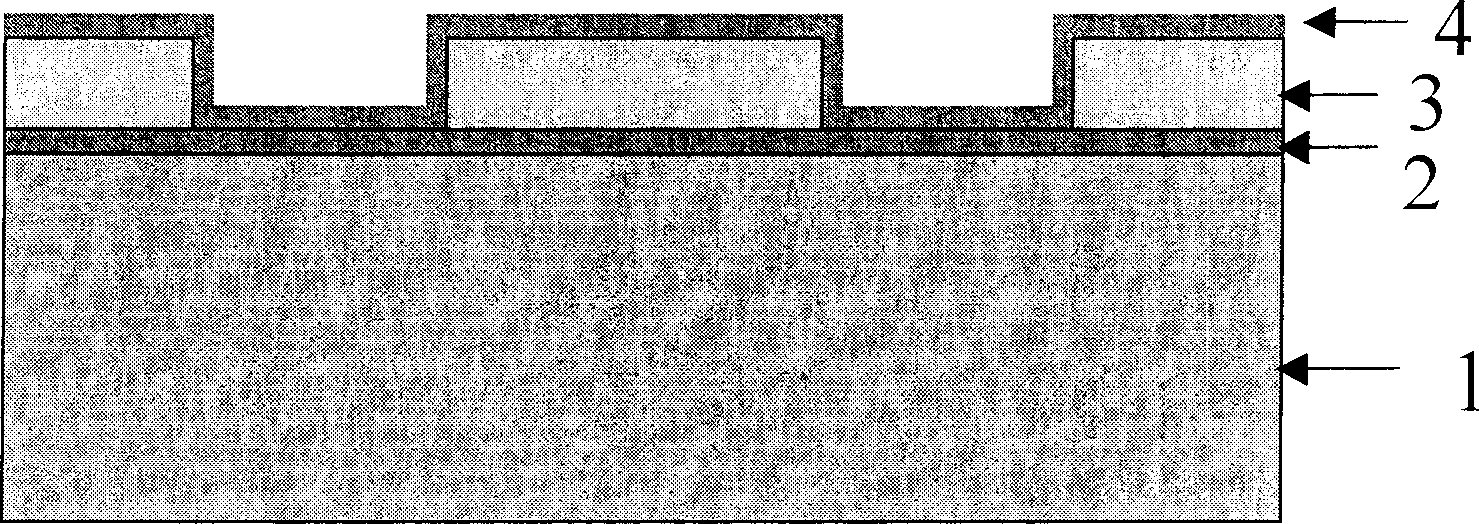

[0031] The present invention is in conventional STI process, reaches the above-mentioned object by the method for increasing a MASK and relevant process step, therefore, the main process step of process method of the present invention is listed below (particularly different from conventional STI process flow The process steps), that is, in the STI process flow, the process before the STI planarization, and the subsequent processes are consistent with the processes in other conventional STI processes, and will not be repeated here.

[0032] The following is the process steps before STI CMP in the process flow of this STI (see the description of the drawings):

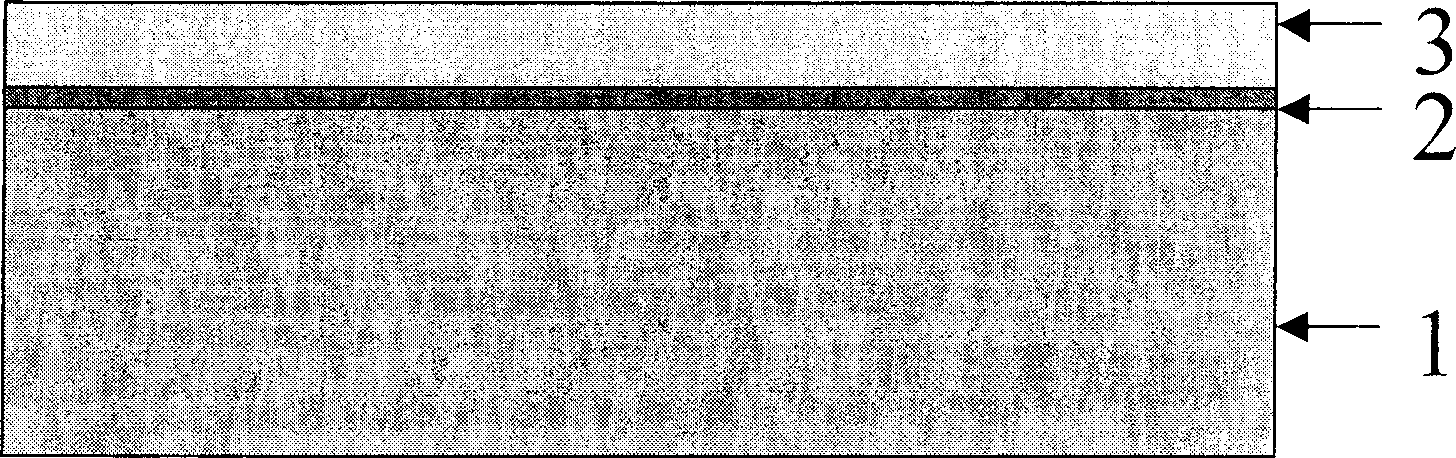

[0033] 1. Deposit silicon oxide and silicon nitride layers, as the HARD MASK defined by STI, the thicknesses are silicon oxide: 10nm; silicon nitride: 200nm; ( figure 1 )

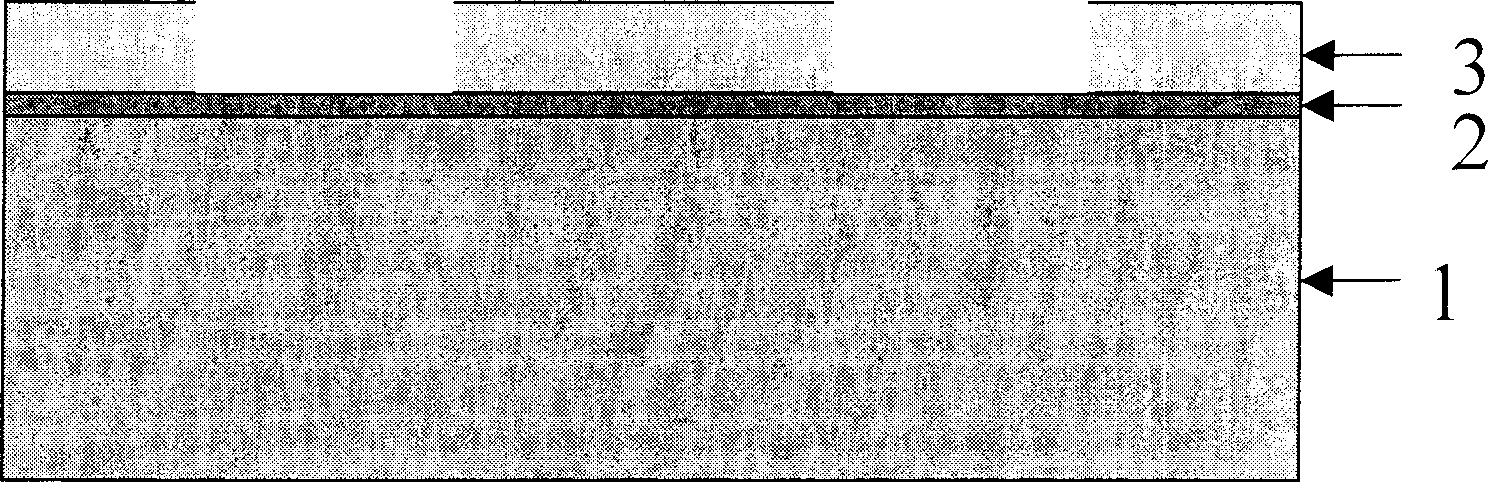

[0034] 2. Use STI MASK to define the STI and active area, that is, the photolithography process

[0035] 3. Etching silicon oxide to expose the STI...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More