Full-digital multi-convolution core-convolution processing chip for AER (Address-Event Representation) image sensor

An image sensor and processing chip technology, used in image communication, color TV parts, TV system parts, etc. The effect of precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

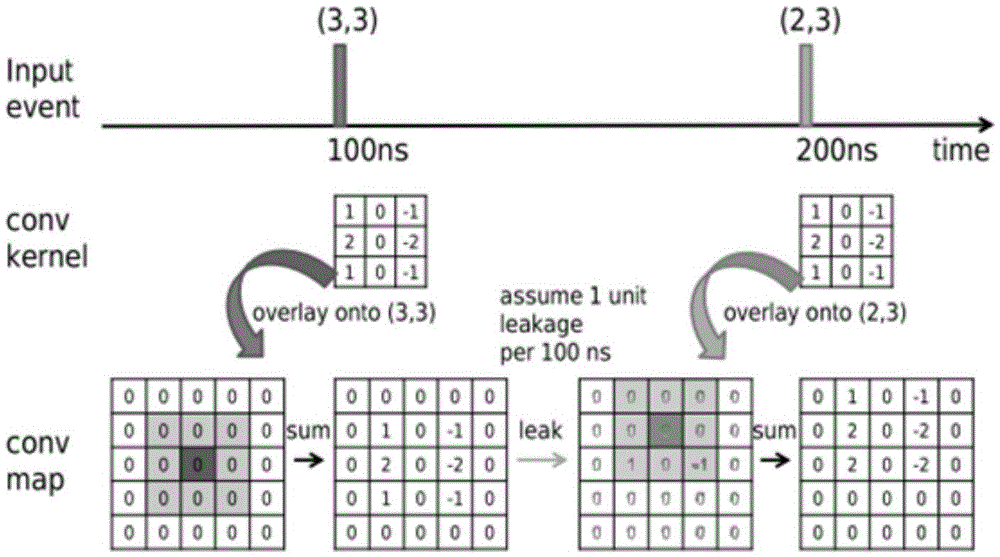

Method used

Image

Examples

Embodiment Construction

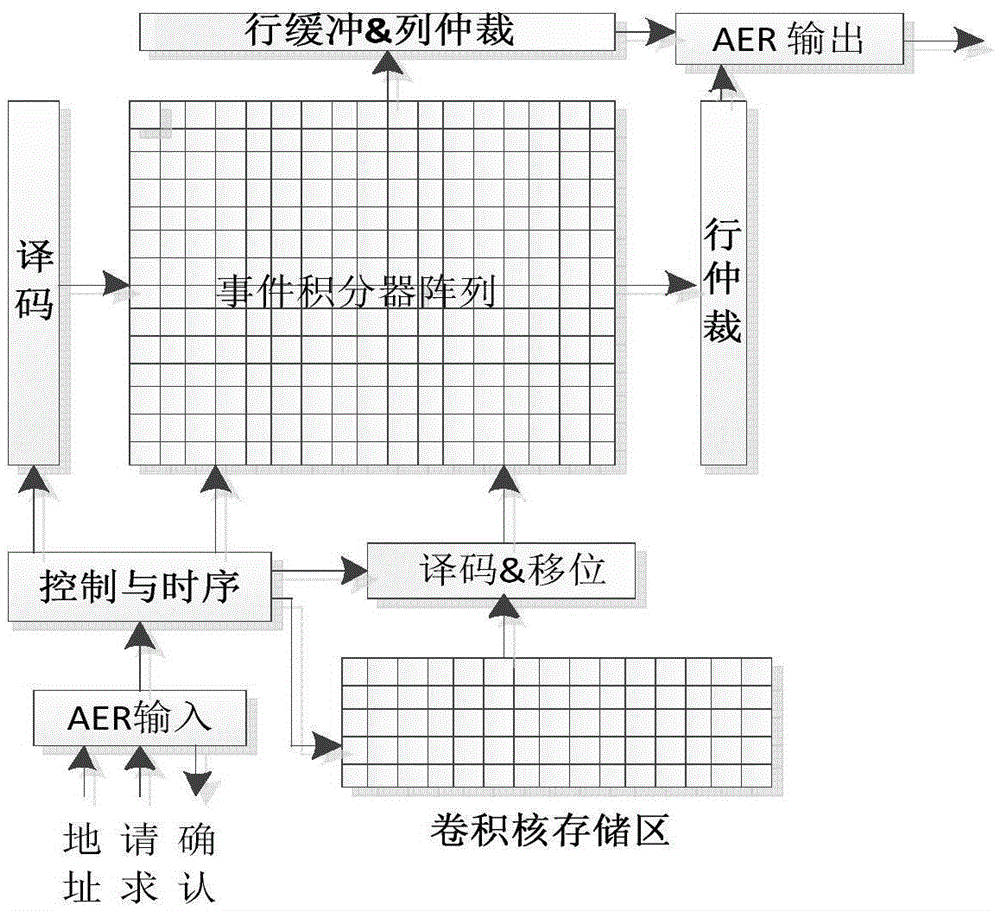

[0016] The all-digital multi-convolution kernel convolution processing chip proposed by the present invention has a structure such as image 3 shown. The all-digital convolution processing chip includes seven parts including event integrator array, convolution kernel storage area, control and timing, and row and column arbitration. The functions of each part are as follows.

[0017] (1) Event integrator array: This structure mainly includes a high-precision, low-power accumulator and a threshold comparator, and its working process is as follows Figure 4 As shown, the control switch reads the convolution kernel into the event integration array according to the occurrence address of the light intensity event of the front-end visual sensor, the adder and accumulator complete the addition of the weight and the historical accumulated value, and the comparator compares the current Compared with the threshold value, the output request is generated if the threshold value is exceeded...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More